# HIGH EFFICIENCY VIDEO CODING PROCESSOR WITH RESIDUE NUMBER SYSTEM

by

Niras Cheeckottu Vayalil

Dissertation submitted in fulfilment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Engineering

Faculty of Science and Engineering

Macquarie University

Sydney, Australia

June 2017

Copyright © 2017 Niras Cheeckottu Vayalil $\label{eq:copyright} \mbox{All Rights Reserved}$

#### ABSTRACT

The recent demand for high density video, such as ultra high definition (UHD) as well as its distribution over wired and wireless networks, led to the proposal of the latest video encoding standard, high efficiency video coding (HEVC/H.265), by the joint collaborative team on video coding (JCT-VC). HEVC/H.265 achieves a significantly better compression than its predecessor, advanced video coding (AVC/H.264), by roughly 50% for an equivalent visual reproduction quality. However, the improved compression efficiency comes with a drawback, the computational complexity. Since HEVC/H.265 encoding involves enormous computations, a hardware implementation of the encoder is necessary for real-time encoding, in particular for UHD video.

The most computationally intensive task in video encoding is motion estimation, which comprises up to 80% of the total time for video encoding. There have been several suggestions for motion-estimation algorithms for reducing the complexity, but many proposed for AVC/H.264 are no longer suitable for HEVC/H.265 due to the underlying coding changes and other complications. Hence, this research offers different algorithms and architectures for motion estimation, providing a trade-off between implementation cost and performance.

Hardware design is proposed for a full-search motion-estimation algorithm which always comes up with the best results. The memory requirement is reduced to a large extent together with the data bandwidth demand. Another important aspect of real-time video compression, including motion estimation, is the delay of

the arithmetic computations. Residue number systems have been used for decades for improving arithmetical operations performance. However, the non-positional nature of an RNS makes it difficult to do some mathematical operations such as sign detection, but it is a vital component for designing motion estimation and other elements of a video processor. The dissertation presents a fast algorithm and its architecture for sign detection, which decreases the area-delay product by 24% compared to designs in the literature.

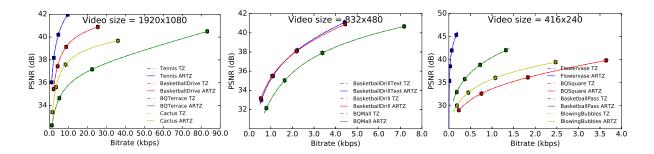

Since the full-search algorithm searches every possible location in a search area, the algorithm involves much computation, therefore fast-search methods are preferred for low-cost solutions. The test zone (TZ) search is a fast-search algorithm and is widely used for HEVC/H.265 as it provides near optimal performance. In this dissertation, a TZ-search hardware architecture is presented, which shows 51% less gate count than existing proposals in the literature and considerably fewer memory requirements than most. Further improvement is achieved by developing a fast-search algorithm appropriate for hardware designs, providing an area-efficient, real-time UHD video-encoding-capable design without degradation in quality from the TZ search in HEVC reference software. An angle-restricted test zone (ARTZ) search motion estimation is also proposed for software applications exploiting directional probabilities of the search, saving about 17% to 55% of time for motion estimation compared to the TZ search.

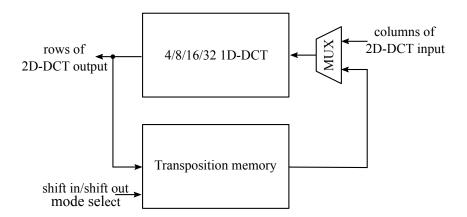

The discrete cosine transform (DCT) is a standard method in several previous codecs and it is also a key factor for compression techniques in HEVC/H.265. A variable-length two-dimensional design is proposed for HEVC/H.265, where the architecture is optimised for the most likely block sizes in UHD video, thus eliminating unnecessary complexities found in many designs, and accomplishing more than 60% savings in hardware.

STATEMENT OF CANDIDATE

I certify that the work in this thesis has not previously been submitted for a

degree nor has it been submitted as part of the requirements for a degree to any

other university or institution other than Macquarie University.

I also certify that the thesis is an original piece of research and it has been written

by me.

In addition, I certify that all information sources and literature used are indicated

in the thesis.

Niras Cheeckottu Vayalil

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the support and contribution of many people. First and foremost, I would like to express my sincere gratitude to my supervisor Dr Yinan Kong for his advice and support throughout the project. He provided many valuable comments and suggestions and constant encouragement during this work. I would also extend my thanks to A/Prof. Manoranjan Paul, Charles Sturt University, my adjunct supervisor, Dr Gengfa Fang and Prof. Michael Heimlich, my co-supervisors, for their excellent support.

I am also thankful to A/Prof. Joachim Rodrigues, EIT, Lund University for providing me with an opportunity to work with digital design tools in EIT, and the necessary guidance. I am also grateful to Dr Oskar Andersson, EIT, for his excellent advice and support during the visit to Lund University.

I am grateful to Dr Keith Imrie for proofreading, and his valuable suggestions on my research papers and this dissertation. I also thank to Md Selim Hossain, Dr. Shahzad Asif, all my friends, all my teachers, and my colleagues who contributed directly or indirectly to my research. I am also thankful to the admirable staff in the engineering department for their wonderful support.

I wish acknowledge to Macquarie University for awarding me an international Macquarie University research excellence scholarship (iMQRES), and the travel grants for collaborative work at Lund University.

I am blessed to have an amazing family and am grateful for their endless support, particularly during the research.

# Contents

| 18 | abie o       | or Con | ntents                    |  |                |   | XV   |

|----|--------------|--------|---------------------------|--|----------------|---|------|

| Li | st of        | public | cations                   |  |                | : | xxi  |

| Li | st of        | contri | ributors                  |  |                | X | xiii |

| Li | ${ m st}$ of | Figure | res                       |  |                | 3 | ΚΧV  |

| Li | ${f st}$ of  | Tables | es                        |  |                | X | xxi  |

| 1  | Intr         | oducti | cion                      |  |                |   | 1    |

|    | 1.1          | Challe | enges and objectives      |  | <br>. <b>.</b> |   | 2    |

|    | 1.2          | Main o | contributions             |  | <br>. <b>.</b> |   | 4    |

|    | 1.3          | Disser | rtation outline           |  | <br>           |   | 5    |

| 2  | Bac          | kgrour | and and Related Work      |  |                |   | 9    |

|    | 2.1          | Video  | compression               |  | <br>           |   | 9    |

|    |              | 2.1.1  | Statistical redundancy    |  | <br>. <b>.</b> |   | 10   |

|    |              | 2.1.2  | Psycho-visual redundancy  |  | <br>. <b>.</b> |   | 12   |

|    |              | 2.1.3  | Coding redundancies       |  | <br>. <b>.</b> |   | 13   |

|    |              | 2.1.4  | Video quality measurement |  | <br>. <b>.</b> |   | 13   |

|    |              | 2.1.5  | Video encoder             |  | <br>           |   | 14   |

${\it xvi}$   ${\it CONTENTS}$

|   | 2.2               | High 6                                                             | efficiency video coding (HEVC/H.265)                                               | 16                               |

|---|-------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------|

|   |                   | 2.2.1                                                              | Coding block and coding tree units                                                 | 16                               |

|   |                   | 2.2.2                                                              | High-level parallelisation features of HEVC/H.265                                  | 20                               |

|   |                   | 2.2.3                                                              | Intra-picture prediction                                                           | 21                               |

|   |                   | 2.2.4                                                              | Inter-picture prediction                                                           | 21                               |

|   |                   | 2.2.5                                                              | Transform coding                                                                   | 24                               |

|   | 2.3               | Block                                                              | matching motion estimation algorithms                                              | 26                               |

|   |                   | 2.3.1                                                              | Full-search block-matching algorithm                                               | 27                               |

|   |                   | 2.3.2                                                              | Fast-search block-matching algorithms                                              | 27                               |

|   | 2.4               | Residu                                                             | ne number systems                                                                  | 36                               |

|   |                   | 2.4.1                                                              | Arithmetic operations in RNS                                                       | 38                               |

|   |                   | 2.4.2                                                              | Negative numbers                                                                   | 39                               |

|   |                   | 2.4.3                                                              | Moduli selection                                                                   | 40                               |

|   |                   | 2.4.4                                                              | Applications of RNS                                                                | 42                               |

|   |                   |                                                                    |                                                                                    |                                  |

|   |                   | 2.4.5                                                              | HEVC procesor with RNS                                                             | 43                               |

| 3 | VLS               |                                                                    | HEVC procesor with RNS                                                             |                                  |

| 3 |                   | SI Arc                                                             |                                                                                    |                                  |

| 3 |                   | SI Arc                                                             | hitecture of Full-Search Variable-Block-Size Motion Estima-                        |                                  |

| 3 | <b>tion</b> 3.1   | SI Arc<br>a for H                                                  | hitecture of Full-Search Variable-Block-Size Motion Estima-<br>EVC Video Encoding  | 45<br>45                         |

| 3 | <b>tion</b> 3.1   | SI Arc<br>a for H<br>Abstra<br>Introd                              | hitecture of Full-Search Variable-Block-Size Motion Estima-<br>EVC Video Encoding  | 45<br>45<br>46                   |

| 3 | 3.1<br>3.2        | SI Arc<br>of for H<br>Abstra<br>Introd<br>Full-S                   | hitecture of Full-Search Variable-Block-Size Motion Estima- EVC Video Encoding act | 45<br>45<br>46                   |

| 3 | 3.1<br>3.2<br>3.3 | SI Arc<br>a for H<br>Abstra<br>Introd<br>Full-S<br>Hardy           | hitecture of Full-Search Variable-Block-Size Motion Estima-EVC Video Encoding  act | 45<br>45<br>46<br>49             |

| 3 | 3.1<br>3.2<br>3.3 | SI Arc<br>a for H<br>Abstra<br>Introd<br>Full-S<br>Hardy           | hitecture of Full-Search Variable-Block-Size Motion Estima-EVC Video Encoding  act | 45<br>45<br>46<br>49             |

| 3 | 3.1<br>3.2<br>3.3 | SI Arc<br>a for H<br>Abstra<br>Introd<br>Full-S<br>Hardy<br>mation | hitecture of Full-Search Variable-Block-Size Motion Estima-EVC Video Encoding  act | 45<br>45<br>46<br>49             |

| 3 | 3.1<br>3.2<br>3.3 | Abstra Introd Full-S Hardv mation 3.4.1                            | hitecture of Full-Search Variable-Block-Size Motion Estima-EVC Video Encoding  act | 45<br>45<br>46<br>49<br>50<br>51 |

| CONTENTE | • • |

|----------|-----|

| CONTENTS | XVI |

|          |     |

|      | 3.5.1                                                         | FPGA Synthesis Results                                                                                                                                                                                                                                          | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 3.5.2                                                         | ASIC Synthesis                                                                                                                                                                                                                                                  | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.6  | Conclu                                                        | ısion                                                                                                                                                                                                                                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Fast | t Sign-                                                       | detection Algorithm for Residue Number System Moduli Set                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                               |                                                                                                                                                                                                                                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •    |                                                               |                                                                                                                                                                                                                                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                               |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                               |                                                                                                                                                                                                                                                                 | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.3  |                                                               |                                                                                                                                                                                                                                                                 | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.4  | Sign d                                                        | etection                                                                                                                                                                                                                                                        | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.4.1                                                         | Sign determination for special moduli sets                                                                                                                                                                                                                      | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.4.2                                                         | Proposed sign detection algorithm for moduli set $\{2^n-1,2^n,2^{n+1}-$                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                               | 1}                                                                                                                                                                                                                                                              | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.4.3                                                         | Optimization for hardware                                                                                                                                                                                                                                       | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.4.4                                                         | Hardware                                                                                                                                                                                                                                                        | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.5  | Perfor                                                        | mance analysis                                                                                                                                                                                                                                                  | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.6  | Conclu                                                        | asion                                                                                                                                                                                                                                                           | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ASI  | C Desi                                                        | ign in Residue Number System for Calculating Minimum Sum                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| of A | Absolut                                                       | te Differences                                                                                                                                                                                                                                                  | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | Abstra                                                        | act                                                                                                                                                                                                                                                             | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2  | Introd                                                        | uction                                                                                                                                                                                                                                                          | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

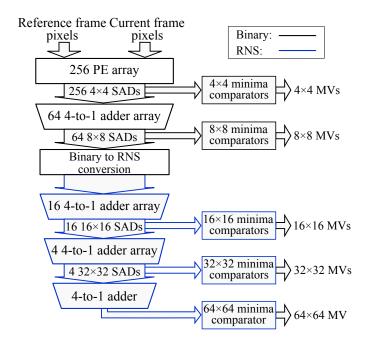

| 5.3  | Propos                                                        | sed architecture for calculating minimum of SAD                                                                                                                                                                                                                 | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.3.1                                                         | Sign detection                                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.3.2                                                         | Modulo- $(2^n - 1)$ adder and subtractor                                                                                                                                                                                                                        | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.3.3                                                         | Absolute difference unit                                                                                                                                                                                                                                        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.3.4                                                         | Accumulation and comparison                                                                                                                                                                                                                                     | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Fast {2 <sup>n</sup> 4.1 4.2 4.3 4.4 4.5 4.6 ASI of A 5.1 5.2 | 3.5.2  3.6 Conclust  Fast Sign-  {2 <sup>n</sup> - 1, 2 <sup>n</sup> ,  4.1 Abstract  4.2 Introd  4.3 Residu  4.4 Sign d  4.4.1  4.4.2  4.4.3  4.4.4  4.5 Perfor  4.6 Conclust  ASIC Desiration  6.1 Abstract  5.2 Introd  5.3 Proposition  5.3.1  5.3.2  5.3.3 | 3.5.2 ASIC Synthesis 3.6 Conclusion  Fast Sign-detection Algorithm for Residue Number System Moduli Set $\{2^n-1,2^n,2^{n+1}-1\}$ 4.1 Abstract 4.2 Introduction 4.3 Residue Number Systems 4.4 Sign detection 4.4.1 Sign determination for special moduli sets 4.4.2 Proposed sign detection algorithm for moduli set $\{2^n-1,2^n,2^{n+1}-1\}$ 4.4.3 Optimization for hardware 4.4.4 Hardware 4.5 Performance analysis 4.6 Conclusion  ASIC Design in Residue Number System for Calculating Minimum Sum of Absolute Differences 5.1 Abstract 5.2 Introduction 5.3 Proposed architecture for calculating minimum of SAD 5.3.1 Sign detection 5.3.2 Modulo- $(2^n-1)$ adder and subtractor 5.3.3 Absolute difference unit |

xviii CONTENTS

|   | 5.4 | Implementation and results                                                   |

|---|-----|------------------------------------------------------------------------------|

|   | 5.5 | Conclusion                                                                   |

| 6 | ASI | C Design of TZ Search Motion-Estimation for HEVC with RNS 93                 |

|   | 6.1 | Abstract                                                                     |

|   | 6.2 | Introduction                                                                 |

|   | 6.3 | Residue Number Systems                                                       |

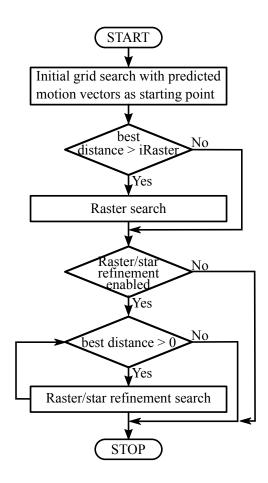

|   | 6.4 | Hardware design of test zone search motion estimation in RNS for HEVC . 97   |

|   |     | 6.4.1 Hardware architecture for test zone (TZ) search motion-estimation . 98 |

|   |     | 6.4.2 Residue number systems for the motion-estimation hardware archi-       |

|   |     | tecture                                                                      |

|   | 6.5 | Analysis of Results                                                          |

|   | 6.6 | Conclusion                                                                   |

| 7 | A F | tesidue Number System Hardware Design of Fast-Search Variable-               |

|   | Mo  | cion-Estimation Accelerator for HEVC/H.265 109                               |

|   | 7.1 | Abstract                                                                     |

|   | 7.2 | Introduction                                                                 |

|   | 7.3 | Residue Number Systems                                                       |

|   | 7.4 | Proposed algorithm for motion estimation                                     |

|   | 7.5 | Motion estimation hardware design                                            |

|   |     | 7.5.1 Residue number systems for motion-estimation hardware architecture 119 |

|   |     | 7.5.2 Motion-estimation architecture                                         |

|   | 7.6 | Analysis of results                                                          |

|   | 7.7 | conclusion                                                                   |

| 8 | ΑN  | Tovel Angle-Restricted Test Zone Search Algorithm for Performance            |

| - |     | provement of HEVC 135                                                        |

| xix |

|-----|

|     |

|              | 8.1   | Abstract                                                                    | . 135 |

|--------------|-------|-----------------------------------------------------------------------------|-------|

|              | 8.2   | Introduction                                                                | . 136 |

|              | 8.3   | Overview of Test Zone Search Algorithm                                      | . 137 |

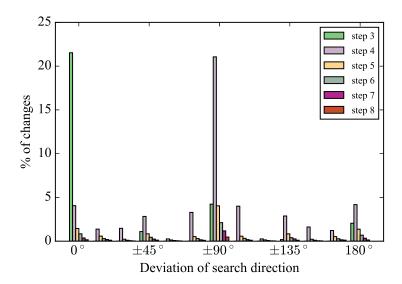

|              | 8.4   | Proposed Algorithm                                                          | . 139 |

|              | 8.5   | Simulation and results                                                      | . 143 |

|              | 8.6   | Conclusion                                                                  | . 144 |

| 9            | An l  | Efficient ASIC Design of Variable-Length Discrete Cosine Transform          | n     |

|              | for l | HEVC                                                                        | 147   |

|              | 9.1   | Abstract                                                                    | . 147 |

|              | 9.2   | Introduction                                                                | . 148 |

|              | 9.3   | Hardware Architecture for DCT computation                                   | . 149 |

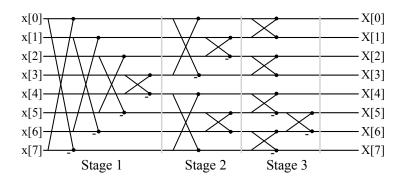

|              |       | 9.3.1 Four-point DCT architecture                                           | . 151 |

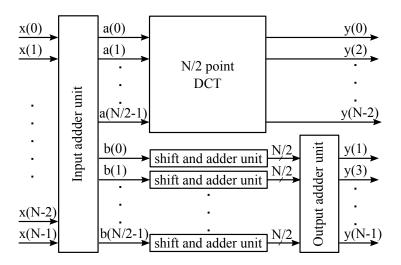

|              |       | 9.3.2 Architecture for higher length 1-D DCTs                               | . 152 |

|              | 9.4   | Proposed hardware architecture for variable-length two-dimensional DCT $$ . | . 153 |

|              | 9.5   | Results and comparison                                                      | . 156 |

|              | 9.6   | Conclusion                                                                  | . 157 |

| 10           | Con   | clusions and Future Work                                                    | 159   |

|              | 10.1  | Conclusions                                                                 | . 159 |

|              | 10.2  | Future work                                                                 | . 162 |

| $\mathbf{A}$ | TCI   | scripts sample for fast search motion estimation design                     | 165   |

| В            | List  | of acronyms                                                                 | 169   |

| Bi           | bliog | raphy                                                                       | 172   |

|              |       |                                                                             |       |

### List of publications

Following are the list of peer-reviewed research papers published, accepted or in review which resulted from the part of research.

#### Discussed in thesis

- N. C. Vayalil, and Y. Kong, "VLSI Architecture of Full-Search Variable-Block-Size Motion Estimation for HEVC Video Encoding", IET Circuits Devices & Systems, 2017, in press.

- 2. N. C. Vayalil, and Y. Kong, "Fast sign-detection algorithm for residue number system moduli set  $\{2^n 1, 2^n, 2^{n+1} 1\}$ ", *IET Computers Digital Techniques*, vol. 11, no. 1, pp. 33–42, 2016.

- 3. N. C. Vayalil, A. Safari, and Y. Kong, "ASIC design in residue number system for calculating minimum sum of absolute differences", *Tenth International Conference on Computer Engineering & Systems (ICCES)*, Dec. 2015, pp. 129-132.

- 4. N. C. Vayalil, and Y. Kong, "ASIC design of test zone search motion-estimation hardware for high efficiency video coding (HEVC) with residue number system", IET Circuits Devices & Systems, 2017, in review.

- 5. N. C. Vayalil, M. Paul, and Y. Kong, "A residue number system hardware design of

- fast-search variable-motion-estimation accelerator for HEVC/H.265", IEEE Transactions on Circuits and Systems for Video Technology, 2017, In review.

- N. C. Vayalil, M. Paul, and Y. Kong, "A novel angle-restricted test zone search algorithm for performance improvement of HEVC", IEEE International Conference on Image Processing (ICIP), 2017, accepted.

- N. C. Vayalil, J. Haddrill, and Y. Kong, "An efficient ASIC design of variable length discrete cosine transform for HEVC", 2016 European Modelling Symposium (EMS), Nov. 2016, pp. 229-233.

#### Other Publications

These publications are related but are not discussed in the thesis.

- A. Safari, N. C. Vayalil, and Y. Kong, "Power-performance enhancement of two-dimensional RNS-based DWT image processor using static voltage scaling", Integration, the VLSI Journal, vol. 53, no. 2, pp. 145156, 2016.

- 2. M. Hossain, Y. Kong, E. Saeedi, and N. C. Vayalil, "High-performance elliptic curve cryptography processor over NIST prime fields", *IET Computers & Digital Techniques*, vol. 11, no. 1, pp. 33–42, 2017.

- 3. N. C. Vayalil, A. Safari, and Y. Kong, "Overlapped block-processing VLSI architecture for separable 2D filters", *Electronics, Communications and Networks IV*, , June 2015, pp. 1355–1358.

- Y. Kong, A. Safari, and N. C. Vayalil, "A low-cost architecture for DWT filter banks in RNS applications," 2014 International Symposium on Integrated Circuits (ISIC), Dec. 2014, pp. 448–451.

### List of contributors

Supervisor Dr. Yinan Kong, Department of Engineering, Macquarie University, NSW, Australia

**Adjunct Supervisor** A/ Prof. Manoranjan Paul, School of Computing and Mathematics, Charles Sturt University, NSW, Australia.

In all the publications discussed in the thesis, I have conducted the major investigations, designs measurements, data processing, and drafting. Dr. Yinan Kong, who is the principle supervisor provided suggestions, advices and invaluable guidance at every stage of the research. A/ Prof. Manoranjan Paul, adjunct supervisor provided invaluable guidance and reviewed, proof-read and corrected all the manuscripts that he has contributions. A graduate student and internal collaborator Joshua Haddrill, helped in designing of DCT architecture for HEVC/H.265 and writing a research paper co-authored with him. Table 1 gives detailed list of contributors.

#### List of contributors

Division of labour in co-authored articles

NC - Niras Cheeckottu Vayalil; YK Yinan Kong; MP Manoranjan Paul; JH Joshua Haddrill

|                 | 1      | 2      | 3      | 4      | 5       | 6       | 7       |

|-----------------|--------|--------|--------|--------|---------|---------|---------|

| Conception&     | NC     | NC     | NC     | NC     | NC      | NC      | NC, JH  |

| Design          |        |        |        |        |         |         |         |

| Planning &      | NC     | NC     | NC, YK | NC     | NC      | NC, MP  | NC, JH  |

| implementation  |        |        |        |        |         |         |         |

| Data collection | NC     | NC     | NC     | NC     | NC      | NC      | NC, JH  |

| Analysis &      | NC     | NC     | NC     | NC     | NC      | NC      | NC, JH  |

| interpretation  |        |        |        |        |         |         |         |

| Writing the     | NC, YK | NC, YK | NC, YK | NC, YK | NC, MP, | NC, MP, | NC, JH, |

| article         |        |        |        |        | YK      | YK      | YK      |

| Overall         | YK     | YK     | YK     | YK     | MP, YK  | MP, YK  | YK      |

| responsibility  |        |        |        |        |         |         |         |

Table 1:  $Author's \ contributions$

# List of Figures

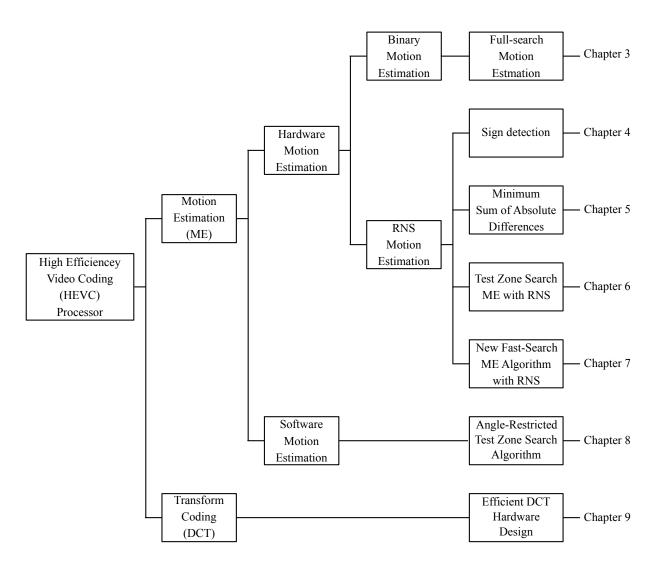

| 1.1  | Thesis outline                                                                 | 6  |

|------|--------------------------------------------------------------------------------|----|

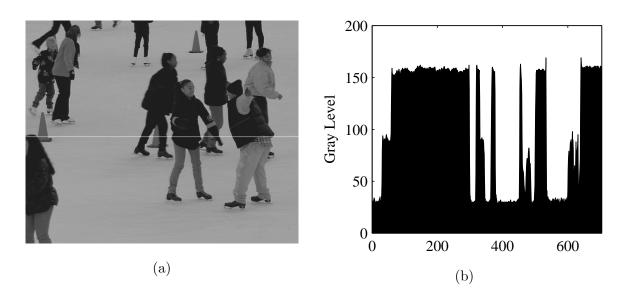

| 2.1  | (a) First frame of ice_4cif video sequence and (b) grey levels of pixels along |    |

|      | the $300^{\rm th}$ row of this frame                                           | 10 |

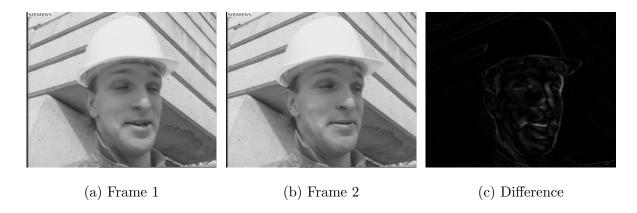

| 2.2  | Frames from video sequence Foreman, and the differences                        | 12 |

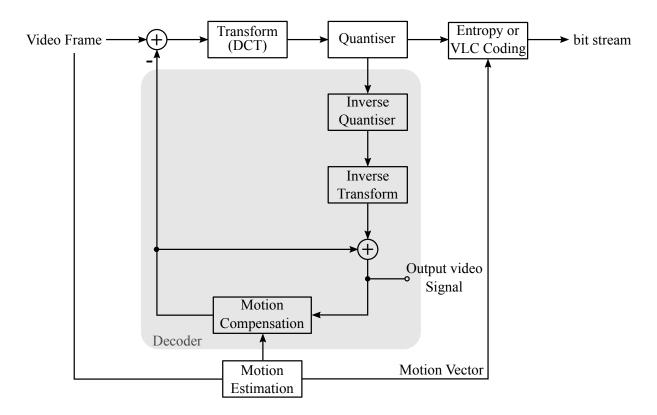

| 2.3  | Simplified block diagram of a video encoder                                    | 15 |

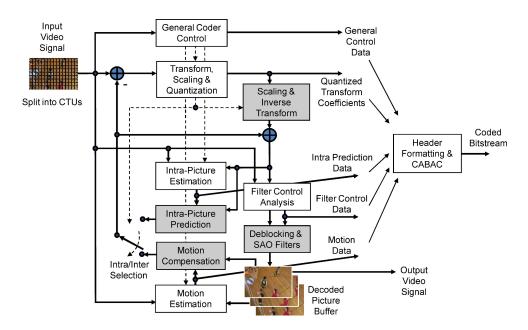

| 2.4  | HEVC Encoder (with decoder modeling elements shaded in light grey)             | 17 |

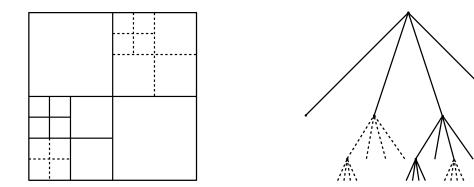

| 2.5  | Subdivision of a CTB with its partitioning and corresponding quad-tree         |    |

|      | structure. CBs represented in solid lines and TBs in dotted lines              | 18 |

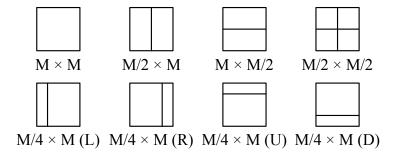

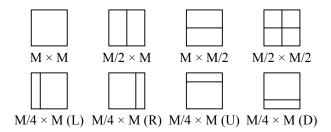

| 2.6  | Splitting coding blocks (CBs) into prediction blocks (PBs); the lower four     |    |

|      | are called asymmetric motion partitioning (AMP)                                | 18 |

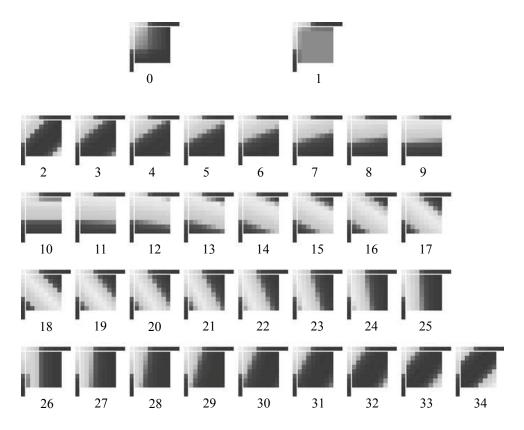

| 2.7  | Examples for HEVC intra-prediction for an $8 \times 8$ luma block, where 0 is  |    |

|      | the DC prediction, 1 is planar and the rest are angular predictions            | 22 |

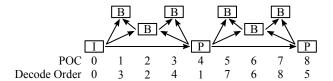

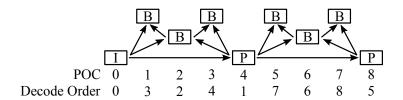

| 2.8  | A hierarchical GOP coding structure with size 4                                | 24 |

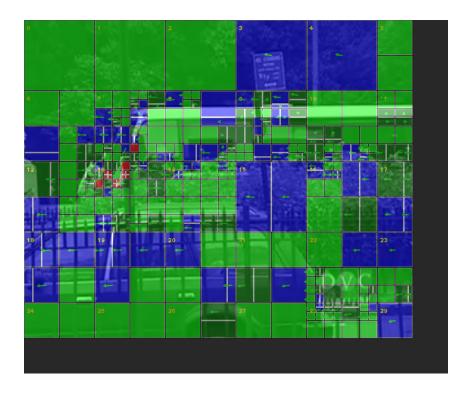

| 2.9  | CTB structure and motion vectors of the 'bus' sequence frame 3, where          |    |

|      | intra blocks are in red, inter blocks are in blue, merge-mode blocks are in    |    |

|      | dark green and skip-mode blocks are in light green                             | 25 |

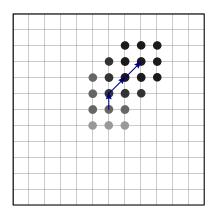

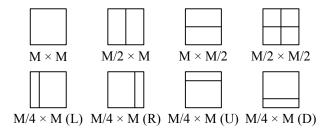

| 2.10 | A 2D logarithme search procedure for finding minimum distortion                | 30 |

xxvi LIST OF FIGURES

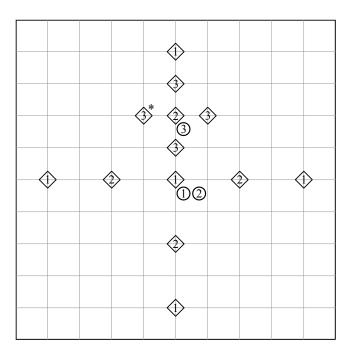

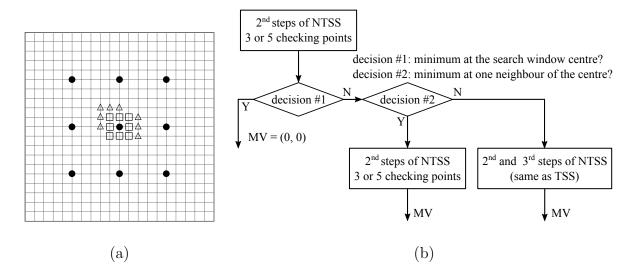

| 2.11 | NTSS algorithm. (a) Showing search points, where filled circles are the                       |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | checking points in TSS and squares are the additional 8 points in the first                   |    |

|      | step of NTSS, and the triangle shows the second step if the minimum is at                     |    |

|      | one of the eight neighbours. (b) NTSS flow chart                                              | 31 |

| 2.12 | Illustration of block-based gradient-descent algorithm; the arrows demon-                     |    |

|      | strate movements of the search centre                                                         | 32 |

| 2.13 | Search patterns used for the diamond search algorithm. (a) Large diamond                      |    |

|      | search pattern. (b) Small diamond search pattern                                              | 33 |

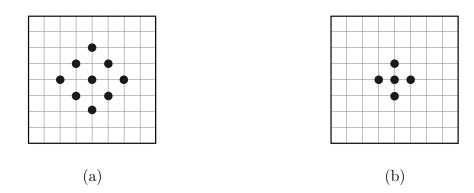

| 2.14 | Use of acceleration information for motion vector prediction in EPZS algo-                    |    |

|      | rithm.                                                                                        | 34 |

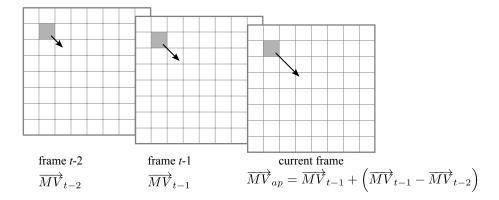

| 2.15 | Search patterns used in test zone search algorithm. (a) Square pattern. (b)                   |    |

|      | Diamond pattern. (c) Raster scan pattern                                                      | 35 |

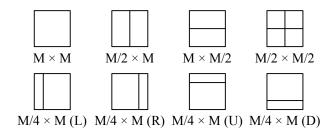

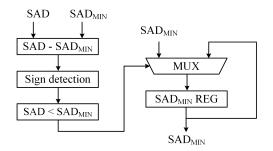

| 3.1  | Partitioning of CB into PB in HEVC                                                            | 49 |

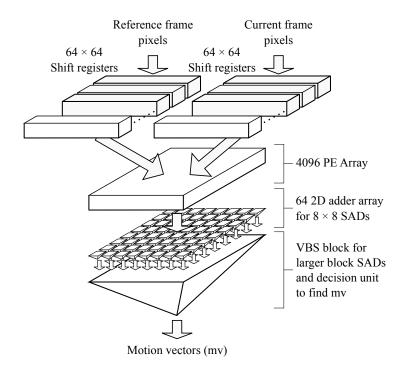

| 3.2  | Motion Estimation (ME) hardware architecture. RAMs are used for storing                       |    |

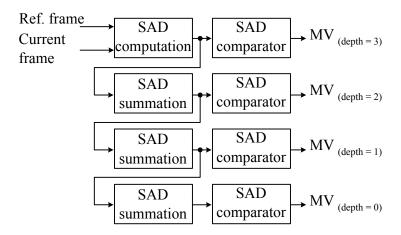

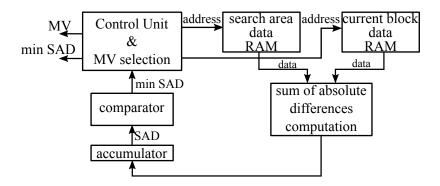

|      | partial and SAD results in each summation stage                                               | 51 |

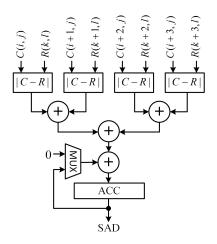

| 3.3  | Processing Element (PE) for calculating SAD of 4 pixels                                       | 51 |

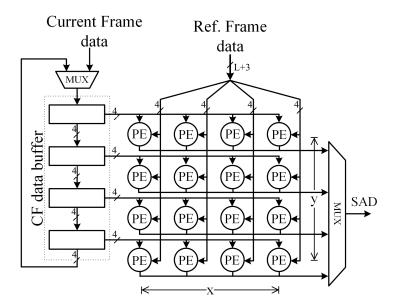

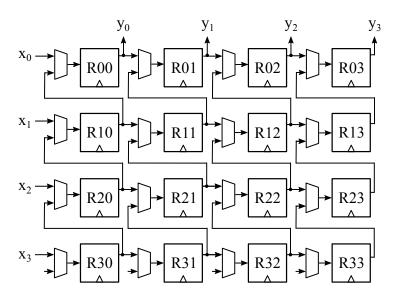

| 3.4  | Processing Element (PE) array for Motion Estimation SAD computation.                          |    |

|      | The $L \times 4$ PE array can be reconfigurable in the $x$ direction; in the above            |    |

|      | L=4.                                                                                          | 52 |

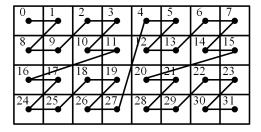

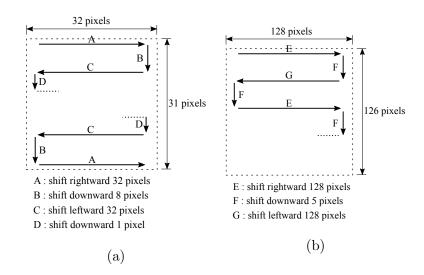

| 3.5  | Morton order or Z-order method for loading data into CF data buffer.                          |    |

|      | $32 \times 64$ pixels are shown, where each square represents a block of $8 \times 8$ pixels. | 54 |

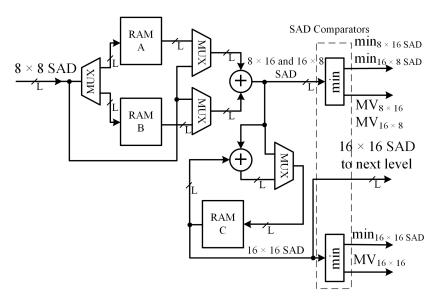

| 3.6  | SAD Summation block with the SAD comparators. This calculates SAD                             |    |

|      | values for higher levels using SAD values from the lower level in HEVC                        |    |

|      | quad-tree SADs, and finds the minimum of these SAD values. The above                          |    |

|      | shows calculation of $8 \times 16, \ 16 \times 8$ and $16 \times 16$ block SAD values and MVs |    |

|      | from $8 \times 8$ block SAD values                                                            | 55 |

LIST OF FIGURES xxvii

| 3.7 | Simulation window of ModelSim simulator, simulated with ICE (4CIF) test                                               |    |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

|     | video sequence. The snapshot shows motion vectors and SAD values of the                                               |    |

|     | first CTU of the video when hardware completes motion search with search                                              |    |

|     | range of $\pm 8$ pixels                                                                                               | 58 |

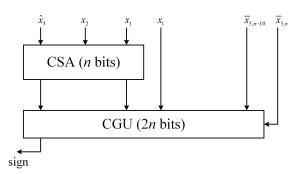

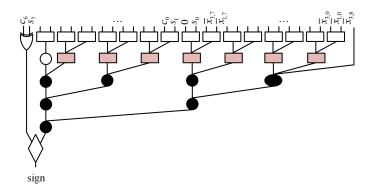

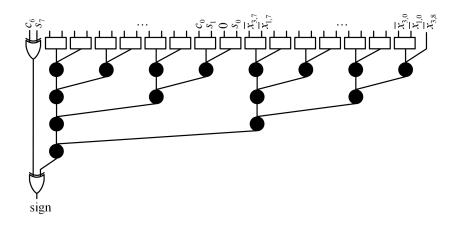

| 4.1 | Sign-detection schematic. $\hat{x}_3$ is $\bar{x}_{3,n-2:0}$ concatenated with bit $\bar{x}_{3,n}$ , and              |    |

|     | CSA, CGU are $n$ -bit carry-save adder and $2n$ -bit carry-generation units                                           |    |

|     | respectively                                                                                                          | 74 |

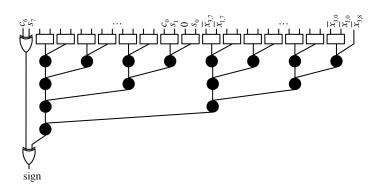

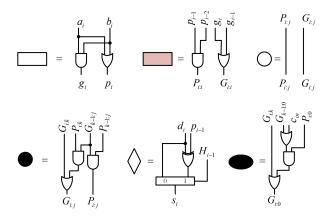

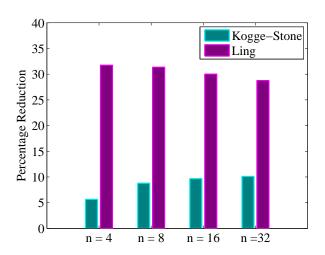

| 4.2 | 2n-bit carry-generation Unit (CGU) based on Kogge-Stone architecture;                                                 |    |

|     | $n = 8. \dots $ | 76 |

| 4.3 | 2n-bit carry-generation Unit (CGU) based on Ling architecture; $n=8.$                                                 | 76 |

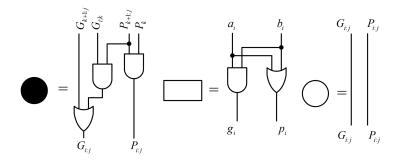

| 4.4 | Blocks of the carry-generation unit                                                                                   | 77 |

| 4.5 | Percentage reduction of area-delay product based on the unit model                                                    | 78 |

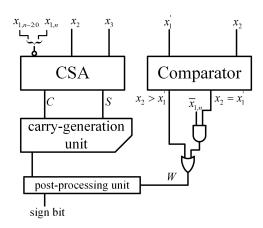

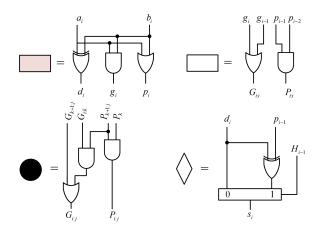

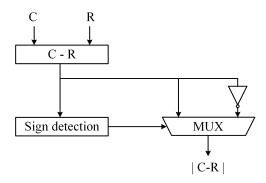

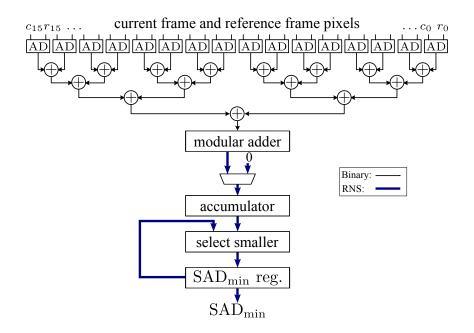

| 5.1 | Sign detection module for the moduli set $\{2^{n+1}-1,2^n-1,2^n\}$                                                    | 86 |

| 5.2 | Carry-generation unit and post-processing unit, modified with the blocks                                              |    |

|     | in Fig. 5.3                                                                                                           | 86 |

| 5.3 | Modified blocks for carry-generation unit                                                                             | 86 |

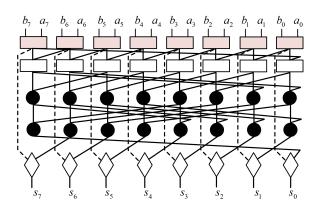

| 5.4 | Modulo-255 adder based on Ling structure                                                                              | 88 |

| 5.5 | Prefix logic operators for modulo- $(2^n - 1)$ adder                                                                  | 88 |

| 5.6 | Absolute difference unit                                                                                              | 90 |

| 5.7 | Finding minimum SAD                                                                                                   | 91 |

| 6.1 | Partitioning of CB into PBs in HEVC                                                                                   | 97 |

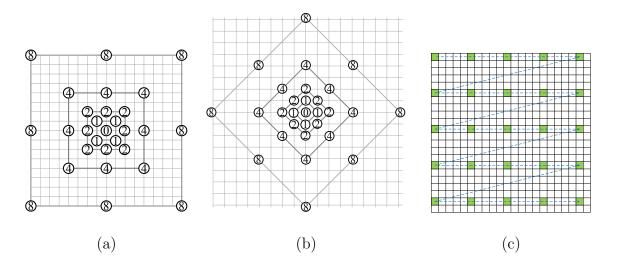

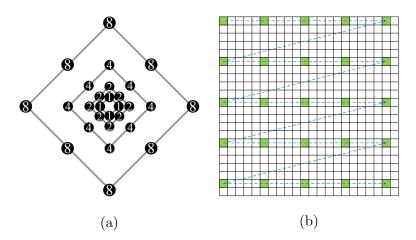

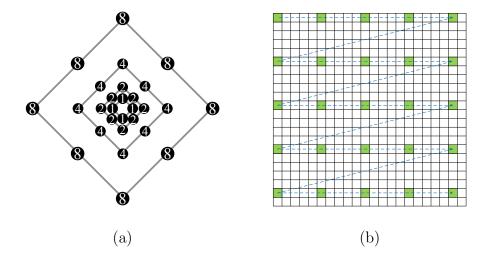

| 6.2 | Search pattern for initial grid search and raster search in test zone (TZ)                                            |    |

|     | search algorithm: (a) diamond pattern for initial grid search, (b) raster-                                            |    |

|     | scan pattern.                                                                                                         | 98 |

| 6.3 | Architecture of test zone (TZ) search motion-estimation                                                               | 99 |

xxviii LIST OF FIGURES

| 6.4 | Data path of motion-estimation architecture; modular adders are used to             |

|-----|-------------------------------------------------------------------------------------|

|     | convert binary into RNS, thus carry-propagation delays in long-word addi-           |

|     | tions in the accumulator are diminished                                             |

| 7.1 | Search pattern for initial grid search and raster search in test zone (TZ)          |

|     | search algorithm: (a) diamond pattern for initial grid search, (b) raster           |

|     | scan pattern                                                                        |

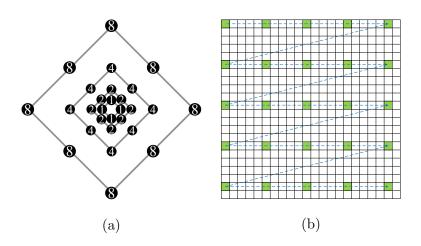

| 7.2 | Search pattern for initial search and raster-like scan in the proposed search       |

|     | algorithm: (a) pattern for initial grid search, (b) raster-like search pattern. 117 |

| 7.3 | Partitioning of CB into PB in HEVC                                                  |

| 7.4 | Architecture of motion estimation hardware                                          |

| 7.5 | Detailed structure of VBS block, where RNS data path and hardware sec-              |

|     | tions are shown in different color. Motion vectors (MVs) are provided in            |

|     | binary from both binary and RNS minima comparators                                  |

| 7.6 | A hierarchal GOP coding structure with size 4. This structure is used               |

|     | for determining the number of clock cycles for encoding videos as listed in         |

|     | Table 7.5                                                                           |

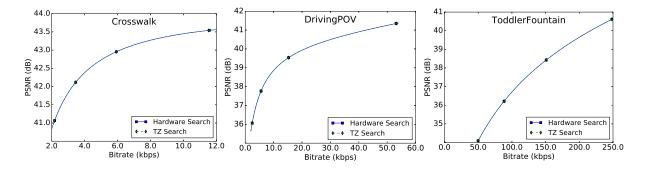

| 7.7 | RD curves for (a) Crosswalk (b) DrivingPOV (c) ToddlerFountain se-                  |

|     | quences with QPs 24, 28, 32, 36                                                     |

| 8.1 | Flow chart for the Test Zone Search Algorithm                                       |

| 8.2 | Search pattern for initial grid search and raster search in test zone (TZ)          |

|     | search algorithm: (a) diamond pattern for initial grid search, (b) raster           |

|     | scan pattern                                                                        |

| 8.3 | Change of search direction in each step of initial search in the TZ Search          |

|     | Algorithm. This image shows the location of minima changes in the 22 <sup>nd</sup>  |

|     | frame of the Netflix_Crosswalk video sequence                                       |

LIST OF FIGURES xxix

| 8.4 | RD curves for different video sequences with QPs 22, 27, 32, 37, with search |

|-----|------------------------------------------------------------------------------|

|     | length 64                                                                    |

| 9.1 | Stick diagram of the butterfly technique applied to the DCT                  |

| 9.2 | A generalized structure of higher radix DCTs, where $N=8,16,32.\dots$ 152    |

| 9.3 | The proposed 2D-DCT architecture, transposition memory implemented           |

|     | using a 2-D register array                                                   |

| 9.4 | The proposed 2D shift register architecture, showing 4 inputs and 4 out-     |

|     | puts. Data is shifted in the horizontal direction from left to right, and    |

|     | shifted out in the up direction; all MUX selection changes accordingly 154   |

## List of Tables

| 1   | Author's contributions                                                     | xxiv |

|-----|----------------------------------------------------------------------------|------|

| 2.1 | Comparison of supported prediction block sizes in different generations of |      |

|     | video coding standards                                                     | 19   |

| 2.2 | Residues of various moduli sets                                            | 37   |

| 3.1 | The detailed data flow in the PE array with $L=4$                          | 53   |

| 3.2 | Comparison of space time complexities of different integer motion estima-  |      |

|     | tion hardwares                                                             | 57   |

| 3.3 | Comparison of proposed design with other HEVC/H.265 full-search integer    |      |

|     | motion estimation implementation in Xilinx Virtex-5 devices                | 59   |

| 3.4 | Comparison of proposed design with previous HEVC/H.265 full-search in-     |      |

|     | teger motion estimation in ASIC                                            | 61   |

| 4.1 | Area and delay comparison for the unit-gate model                          | 78   |

| 4.2 | Area, delay and power comparison of radix-2 architecture experimental      |      |

|     | results                                                                    | 79   |

| 4.3 | Area, delay and power comparison of radix-4 architecture experimental      |      |

|     | results                                                                    | 80   |

xxxii LIST OF TABLES

| 5.1 | Performance comparison of modulo adders, designed with GLOBALFOUNDRIES $^\circledR$    |

|-----|----------------------------------------------------------------------------------------|

|     | 0.18 μm                                                                                |

| 5.2 | Performance comparison of proposed SAD unit                                            |

| 6.1 | Number of $4 \times 4$ SAD computations involved in various test videos for TZ         |

|     | search inter-picture motion-estimation                                                 |

| 6.2 | Comparison of HEVC/H.265 motion-estimation architectures 105                           |

| 7.1 | Percentage of raster searches in a TZ search motion estimation                         |

| 7.2 | Percentage of first minimum error locations occurring after the 'iRaster' (5           |

|     | pixels) distance, only considered search involving raster scans                        |

| 7.3 | Percentage of $64 \times 64$ inter-prediction coding blocks (CBs) in 4K UHD videos 122 |

| 7.4 | Bit-rate and PSNR changes of proposed algorithm compared to the TZ                     |

|     | search                                                                                 |

| 7.5 | Bit rate and PSNR and total clock cycles to encode 64 UHD video frames                 |

|     | using the GOP structure in Fig. 7.6                                                    |

| 7.6 | BD rate and BD PSNR comparison with TZ search                                          |

| 7.7 | Comparison of motion estimation architectures                                          |

| 8.1 | Percentage of raster searches in a TZ search                                           |

| 8.2 | Percentage of first minimum error locations occurs after the 'iRaster' (5              |

|     | pixels) distance                                                                       |

| 8.3 | ARTZ search algorithm results (negative values are improvements) with                  |

|     | different search lengths for 4K UHD resolution                                         |

| 8.4 | ARTZ results with search length 64 and different QPs                                   |

| 9.1 | Four-Point DCT Algorithm by Stage                                                      |

| 9.2 | Comparison of 2D-DCT architectures                                                     |

### Chapter 1

### Introduction

The influence of video and related applications in everyday life has increased exponentially since the advent of digital video. It has a great impact on almost all types of industries including communication, entertainment, and arts. With the advancement of digital technologies, there has been an ever-increasing demand for high-quality video in real-time communication as well as broadcasting or distribution, which necessitate efficient video data compression and standards. Since the early 1990s two main standardisation organizations, the International Telecommunication Union (ITU) and the moving picture expert group (MPEG) formed by International Standardisation Organizations/The International Electrotechnical Commission (ISO/IEC) proposed several standards. Although started for different tracks of applications, they have engaged in close cooperations and proposed advanced video coding (AVC/H.264) and high efficiency video coding (HEVC/H.265) standards, which became milestones in video coding.

On the other hand, the use of mobile devices also increased many-fold along with the advancement of digital technology. As a result, a significant amount of video processing is now taking place on these mobile devices or embedded processors, for which speed and power consumption are very critical. Every new proposal for video coding is targeted

for efficient compression and improved quality, which in turn increases computational complexities in the encoding process; this applies to the latest video coding standard HEVC/H.265 as well, whose computation requirements increased substantially compared to its predecessor.

HEVC/H.265 video coding provides approximately 50% better compression efficiency compared to AVC/H.264. The improved compression capability is imperative for very-high-density videos such as in 4K ultra-high-definition (UHD) resolution. These high-resolution videos provide an immense display experience and are being widely accepted for multi-media display panels. The introduction of HEVC/H.265 saves data bandwidth and storage requirements, but the increased complexity demands hardware implementations specifically targeted for the application.

#### 1.1 Challenges and objectives

Real-time video encoding is very challenging as it involves much computation. Moreover, the problem is aggravated by the increased coding complexities of the latest proposal and the increasing demand for high-quality or UHD-resolution videos. Application specific integrated circuit (ASIC) designs can exploit their parallel-processing features to mitigate several challenges in real-time processing. However, the new features of HEVC/H.265 have not been addressed before, in particular for motion estimation which comprises 60% to 80% of the overall computations for the encoding. HEVC/H.265 introduces several new choices of partitioning types, a hierarchical quad-tree structure, and increases the size of the basic coding block for motion estimation and the residual coding. Therefore, many proposals suggested for its predecessor cannot be adopted for HEVC/H.265.

Due to the difficulties in motion estimation, various algorithms are proposed for alleviating this bottleneck. However, the majority of suggestions are made for software platforms, but the time and power consumption for software implementation are very high, especially for processes with much computation. Furthermore, the solutions implied for software are not optimal for hardware architectures as the latter varies significantly in their operation. As an illustration, it is easy to distribute data in parallel into different sections and process it concurrently, whereas the representation of data is preferred in fixed-point notation as the floating-point notations significantly increase hardware area or cost. On the other hand, parallelism in software is limited by the number of processors available, but the floating-point data representations and algorithms with irregular structures or steps are relatively easy.

The speed of arithmetic units are crucial for hardware architectures, but carry propagation delays generally limit their performance. Residue number systems (RNSs) has been used for improving mathematical operations in hardware platforms for many decades. However, the research on RNS for video processing is not strong. The RNS has a potential to outperform traditional binary systems, as the former could have better arithmetic hardware, and this research investigates the possible areas of using RNS for video processing and its benefits.

In this dissertation, one of the primary objectives is to implement a real-time hard-ware for motion estimation for HEVC/H.265 as it is responsible for the majority of the computations. Most of the problems in current proposals in the literature are addressed in this dissertation. For example, the memory and data bandwidth requirements are minimised by broadcasting data and using specific reading patterns for full-search motion estimation. Different proposals for motion estimation, including new algorithms for both hardware and software platforms, are provided. These choices allow a trade-off between hardware implementation cost and coding performance, as both increase together.

#### 1.2 Main contributions

In this dissertation, several architectures and algorithms have been presented to meet the challenges in real-time video encoder design with the HEVC/H.265 specifications and for UHD resolution, which is becoming very popular. A vital problem in hardware processing is the speed of arithmetic operations, which has been addressed using RNS whenever appropriate. However, some mathematical operations such as magnitude comparison and sign detection are not trivial in an RNS, hence a novel algorithm and architecture have been proposed for addressing this. Motion-compensated prediction is the key for efficient video compression but it is the most tedious and time-consuming process, and it is increased many times in HEVC/H.265 and also by the increased pixel resolution for UHD video. Therefore most of the dissertation is devoted to addressing this problem and providing fastest and most cost-effective solutions. Residual picture coding is another challenge in video encoding, and an ASIC design has been presented as a solution. The following are the some of the key scientific contributions:

- Motion estimation has been broadly classified into full-search and fast-search methods, where a full-search provides better results than fast-search methods. The memory and bandwidth requirements of full-search motion estimation in hardware implementations have been reduced using a different approach for the data reading pattern and by broadcasting data simultaneously to multiple processing elements.

- In this dissertation, the RNS has been used extensively for addressing challenges in video processor design. Nevertheless, one fundamental difficulty in RNS, the sign detection problem, has to be solved since it is the key to many hardware designs. A novel algorithm and architecture have been provided, which significantly reduces the area-delay product compared to others in the literature for a specific moduli set.

- Test-zone (TZ) search is a widely used fast-search motion estimation in HEVC/H.265

as it provides similar results to full-search methods with significant improvement in computational time. A TZ-search hardware implementation has been presented with RNS, providing a very cost-effective solution for motion estimation.

- A new algorithm has been proposed for hardware designs which provides equivalent or better results than a TZ search without increasing hardware cost significantly.

- Angle-restricted test zone (ARTZ) has been proposed for software implementations, exploiting directional probabilities of a motion-vector search, decreasing motion estimation time by 20% to 55% with little quality degradation compared to TZ search in HEVC/H.265 reference software.

- A variable-length discrete cosine transform (DCT) architecture has been presented for HEVC/H.265 specifications. The design is optimised for the most likely block sizes in UHD video, hence unnecessary complexities found in many architectures proposed have been eliminated, which brings about 60% hardware saving and plenty of processing power for the transform coding of UHD video.

## 1.3 Dissertation outline

This dissertation follows the non-traditional "Thesis-by-publication" format which has been approved by the *Macquarie University Higher Degree Office*. It consists of a general introduction, background, and a list of the PhD candidate's major scientific publications. The thesis materials are original texts and graphics of the author's publications, published or under review, that have been reformatted to improve readability. As mentioned before, motion estimation is the most time-consuming operation in video encoding and the dissertation provides a few alternative solutions with a trade-off between many parameters such as hardware cost, quality, and compression efficiency.

Fig. 1.1: Thesis outline

Chapter 2 gives a brief overview of an overall structure of video compression including various basic concepts, encoder architectures and a short introduction to the latest HEVC/H.265 coding standard. A comprehensive review of different algorithms existing in the literature for motion estimation is included in this chapter. It also introduces RNS fundamentals and gives a brief explanation for the choice of a particular moduli set for the application.

Chapter 3 discusses architecture for motion estimation for HEVC/H.265 with the full-search method, which always comes up with better results than fast-search methods. The memory requirement for hardware has been reduced by following a Morton order for data reading and a sum of absolute differences (SAD) reuse strategy. The data bandwidth is also minimised by broadcasting data to multiple processing elements (PEs).