### PULSE WIDTH MODULATION TECHNIQUES TO SUPPRESS

## ELECTROMAGNETIC INTERFERENCE IN POWER CONVERTERS

by

Saad Ul Hasan

Dissertation submitted in fulfilment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

School of Engineering Faculty of Science and Engineering Macquarie University Sydney, Australia

June 2018

This page has been intentionally left blank

Copyright © 2018 Saad Ul Hasan

All Rights Reserved

This page has been intentionally left blank

#### ABSTRACT

Rapid developments in power electronics and semiconductor manufacturing technology have increased the integration of power electronic converters in our everyday life. From biomedical services, utilities, electric cars up to satellite power systems, power electronics has been widely adopted to fulfil the power demands in the most efficient possible ways.

The modern power converter can be viewed as a combination of power switching devices, switched in a pattern to charge/discharge various passive elements to produce the required voltages and currents in a controlled manner. This switching pattern leads to a natural phenomenon of producing voltage and current transitions (dv/dt and di/dt respectively)which are the main cause of electromagnetic interference (EMI) noise from power converters. This noise may be conducted and/or radiated, leading to interference with neighboring electronic circuits and systems. Hence various electromagnetic compatibility (EMC) standards are introduced to keep the naturally occurring noise within a threshold limit.

Traditionally, EMI filters are used to suppress conducted EMI and hence are applicable to a narrow range of frequencies. On the other hand, EMI shielding is used for shielding the sources of EMI in an enclosed chamber to contain the radiated EMI. Both solutions have their limitations and increase the cost and weight of a power converter. Spread-spectrum techniques are utilized to spread the noise over a wider bandwidth, which leads to the suppression of the peaks of EMI, and which eventually suppresses the EMI.

The research work presented in this thesis is based on the generation and application of an aperiodic modulation methodology, which effectively spreads the spectrum of switching harmonics over a wide range of frequencies. It subsequently suppresses the peak EMI of a power converter. A framework to generate such an aperiodic pulse-width modulated signal is presented which can readily be applied to different types of power converters to suppress the EMI. To support this proposition, the modulation methodology has been applied to a single-ended primary-inductor converter (SEPIC) converter, a quasi-Z-source (qZS) DC-DC and a novel transformerless common-ground DC-AC inverter. The suppression in EMI is presented for these converter topologies along with various simulation and experimental results in support of the proposed methodology. Since wide-bandgap (WBG)-based power semiconductor devices allow faster switching, with its associated transients, WBG-based power converters generate more EMI than their silicon-based counterparts. Therefore, WBG-based power converters here are considered for application to the proposed methodology. The hardware prototypes have been developed to integrate WBG power switches, which makes the results more thought-provoking and conclusive.

The presented aperiodic modulation methodology is generalized, which is applicable to a large variety of modern power converters. Various theoretical, analytical and empirical insights are presented in this thesis which develop a sound base for the understanding and suppression of EMI in power converters.

**Keywords:** Electromagnetic interference (EMI), electromagnetic compatibility (EMC), pulse width modulation (PWM), wide bandgap (WBG) semiconductors, spread-spectrum techniques.

#### STATEMENT OF CANDIDATE

I certify that the work in this dissertation titled "Pulse Width Modulation Techniques to suppress Electromagnetic Interference in Power Converters" has not previously been submitted for a degree nor has it been submitted as part of the requirements for a degree to any other university or institution other than Macquarie University. I also certify that the dissertation is an original piece of research and it has been written by me. In addition, I certify that all information sources and literature used are indicated in the dissertation.

. . . . . . . . . . . . . . . .

Saad Ul Hasan

This page has been intentionally left blank

Dedicated to my awesome parents, siblings

Ċ

all the people who are struggling

This page has been intentionally left blank

#### ACKNOWLEDGEMENTS

"All praise and thanks to the Almighty (swt)"

I would like to especially thank my principle supervisor Prof. Graham Town for his continuous guidance and support throughout this Ph.D. Without his unconditional dedication and constructive criticism, this dissertation would not have been possible. I would also like to take this opportunity to thank my associate supervisor Dr. Jahangir Hossain for his kind support and encouraging words.

Also, I deeply thank my adjunct supervisor Dr. Yam P. Siwakoti for his technical feedback and sharing his experiences which motivated me to learn more. I am also very grateful to Dr. Mark J. Scott for hosting me and enabling a collaborative and fruitful research work between Macquarie University, University Technology Sydney and Miami University, Ohio, USA. I would also like to thank the nominated thesis reviewers for giving their consent to examine this thesis despite their busy schedules.

I also want to thank my undergraduate supervisor Prof. Abid Ali Minhas for his support and guidance in each field of life. I want to thank Prof. Liu Jinjun for supervising me during my graduate studies at Xi'an Jiaotong University. With his kind support and my group mates at "Power Electronics & Renewable Energy Research Centre" (PEREC), I really learned a lot about power electronics.

I owe my gratitude to my loving parents and siblings for their support and understanding. I am very much thankful to my grandparents who always have been a motivation and emphasized the importance of learning. Without their support, love and prayers, I would not have reached this point.

I would like to thank the kind support by Dr. Keith Imrie for his kind support, especially in proof-reading my thesis and publications within a short period of time.

Last but not the least, I would like to thank my friends, colleagues and peers for making my life comfortable and enjoyable in Australia. Finally, I am thankful to the financial support and resources provided by Macquarie University to support my PhD and making this journey fruitful and memorable for me. Without this great support, it was not possible to pursue my dream of higher studies.

## Contents

| AF    | BSTR    | ACTiii                                                              |

|-------|---------|---------------------------------------------------------------------|

| Lis   | st of F | Figuresxv                                                           |

| Lis   | st of ] | ſablesxix                                                           |

| Lis   | st of F | Publicationsxxi                                                     |

| Chap  | oter 1  | Introduction and Motivation1                                        |

| 1.1   | l. C    | Overview and Significance of the Research Topic1                    |

| 1.2   | 2. F    | Problem Statement and Research Motivation                           |

| 1.3   | B. C    | Dejectives and Scope of Dissertation                                |

| 1.4   | 4. I    | Dissertation Outline                                                |

| Chapt | ter 2 A | n Overview of EMI and Its Suppression Techniques                    |

| 2.1   | l. E    | CMI and EMC of Power Converters7                                    |

|       | 2.1.1.  | Types of EMI                                                        |

|       | 2.1.2.  | EMI in WBG-based Power Converters11                                 |

|       | 2.1.3.  | EMI Measurement Methods                                             |

|       | 2.1.4.  | EMC Standards16                                                     |

| 2.2   | 2. A    | An Overview of EMI Suppression Techniques                           |

|       | 2.2.1.  | EMI Filters                                                         |

| :     | 2.2.2.  | Electromagnetic Shielding                                           |

|       | 2.2.3.  | Soft Switching                                                      |

|       | 2.2.4.  | Modulation of Switching Signal(s)                                   |

| 2.3   | 3. C    | Chapter Summary                                                     |

| Chap  | oter 3  | EMI Suppression for a High-Frequency GaN-based SEPIC Converter      |

| 3.1   | L A     | Aperiodic Switching Function                                        |

|       | 3.1.1   | Framework for the Implementation of an Aperiodic Switching Signal32 |

| 3      | .1.2.        | Functional Analysis of the Proposed Methodology                               | 34  |

|--------|--------------|-------------------------------------------------------------------------------|-----|

| 3      | .1.3.        | Spectral Analysis of a Pulse-position Modulated Signal                        | 35  |

| 3.2.   | I            | ntroduction to the GaN-based SEPIC Converter                                  | 38  |

| 3.3.   | Ι            | Design Considerations                                                         | 40  |

| 3      | .3.1.        | Design Parameters                                                             | 40  |

| 3      | .3.2.        | High-Frequency PCB Design                                                     | 42  |

| 3.4.   | A            | periodic Gate-drive Signal for EMI Suppression                                | 44  |

| 3.5.   | F            | Experimental Results and Discussion                                           | 47  |

| 3      | .5.1.        | EMI Suppression, Voltage Gain and Efficiency Analysis                         | 47  |

| 3      | .5.2.        | Switching-Frequency Impact on the EMI and Thermal Performance                 | 51  |

| 3.6.   | S            | ummary and Conclusions                                                        | 54  |

| Chapt  | er 4         | Aperiodic Modulation for Cascade GaN HEMT-based qZS DC-DC Converter           | 55  |

| 4.1.   | I            | ntroduction to an Isolated qZS DC-DC Converter Topology                       | 56  |

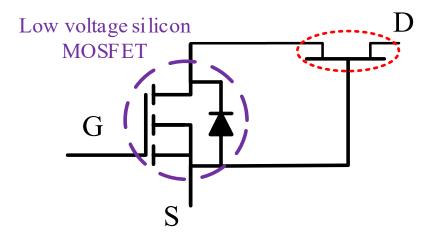

| 4.2.   | C            | Cascode GaN HEMT Switches                                                     | 58  |

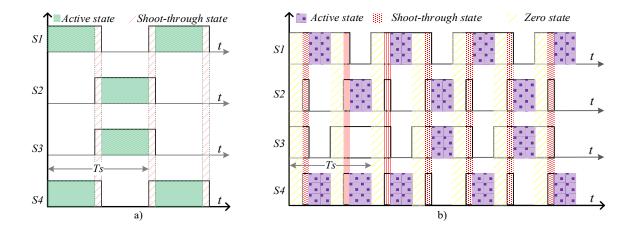

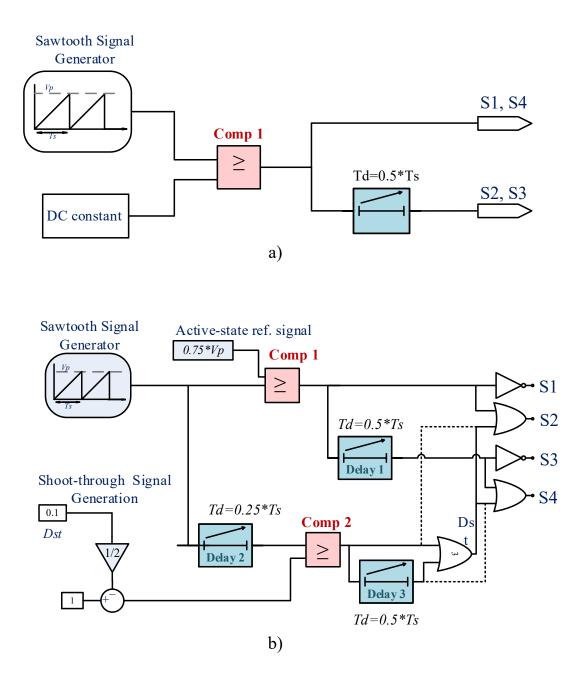

| 4.3.   | C            | Overview of Reference Modulation Schemes for qZS DC-DC Converter              | 59  |

| 4.4.   | A            | aperiodic Modulation Methodology for EMI suppression in a qZS DC-DC Converter | r62 |

| 4      | .4.1         | Aperiodic Modulation Methodology for Reference Scheme A                       | 62  |

| 4      | .4.2         | Aperiodic Modulation Methodology for Reference Scheme B                       | 66  |

| 4.5.   | F            | Results and Discussion                                                        | 70  |

| 4      | .5.1.        | Design Parameters for qZS DC-DC Converter                                     | 70  |

| 4      | .5.2.        | Switching Sequence of Aperiodic Version of Reference Modulation Schemes       | 70  |

| 4      | .5.3.        | Voltage Gain and Efficiency Analysis                                          | 75  |

| 4      | .5.4.        | EMI Analysis                                                                  | 77  |

| 4.6.   | $\mathbf{S}$ | ummary and Conclusions                                                        | 84  |

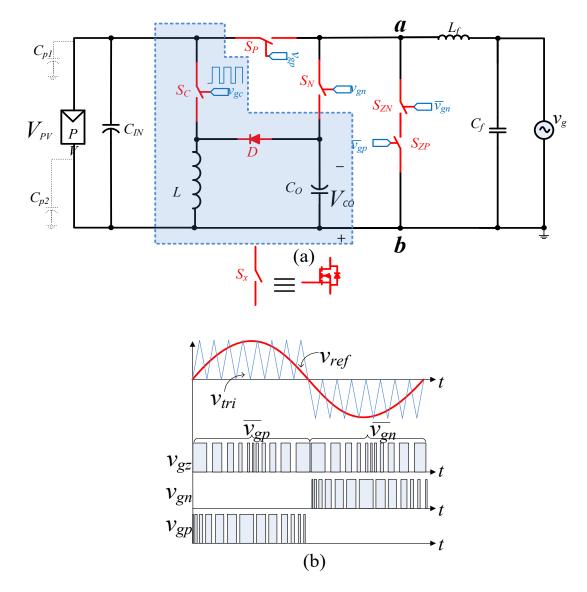

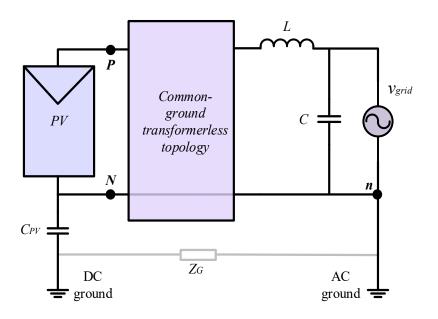

| Chapte | r5A          | Novel Common-Ground Transformerless PV Inverter and Its EMI Analysis          | 87  |

| 5.1.   | Ι            | iterature Survey and Motivation                                               | 88  |

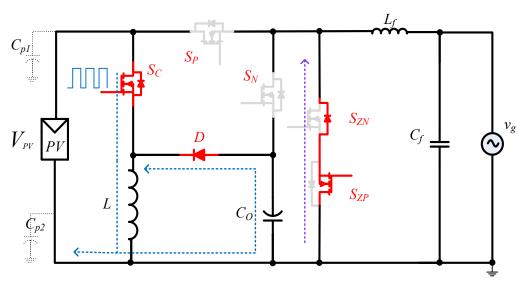

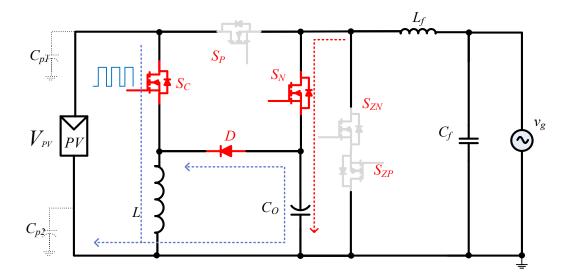

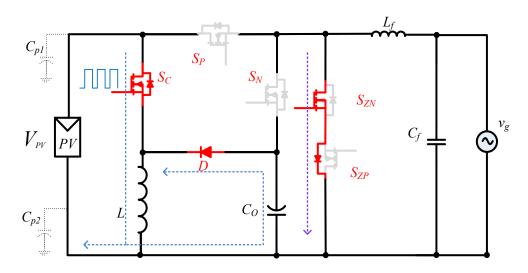

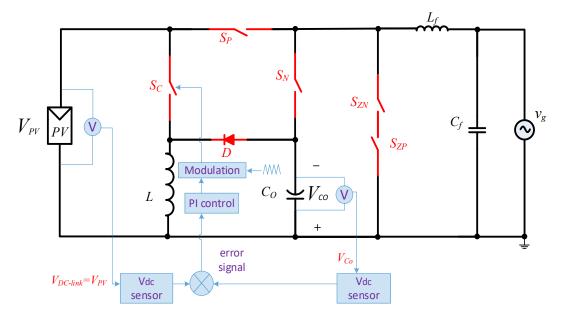

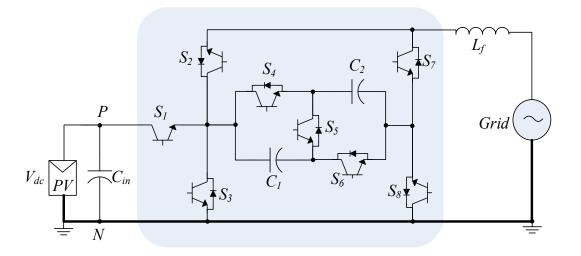

| 5.2.   | F            | Proposed Topology and Principle of Operation                                  | 92  |

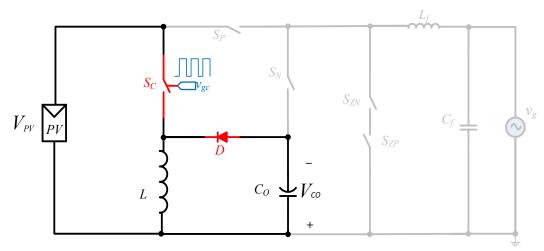

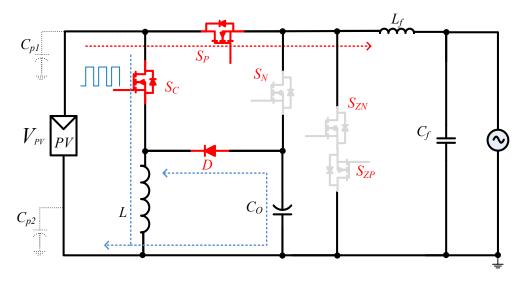

| 5.2.1.      | Principle of Operation of Proposed Inverter Topology               | 93  |

|-------------|--------------------------------------------------------------------|-----|

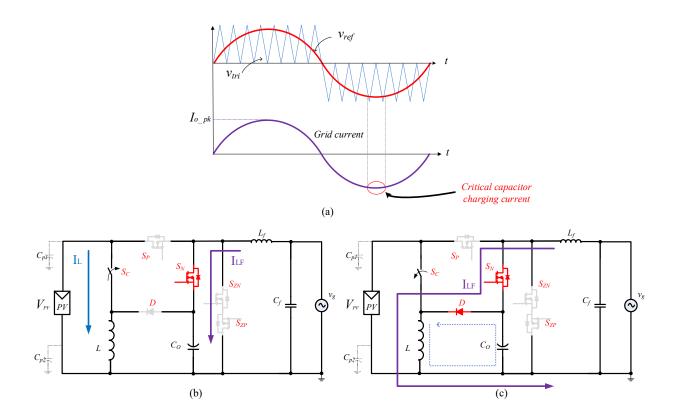

| 5.2.2.      | Operating States of the Proposed Topology                          | 95  |

| 5.3. Co     | mparative Analysis and Design Guidelines                           | 99  |

| 5.3.1.      | Comparison with Similar Topologies                                 | 99  |

| 5.3.2.      | Virtual DC Bus Capacitor Sizing                                    | 102 |

| 5.3.3.      | Common-mode Behavior and Leakage Current                           | 104 |

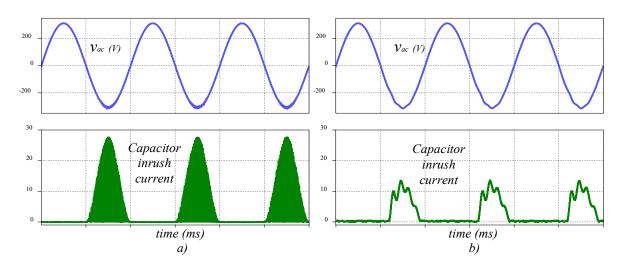

| 5.3.4.      | Voltage and Inrush Current Control of the Virtual DC Bus Capacitor | 105 |

| 5.4. Ap     | eriodic Sinusoidal PWM for EMI Reduction                           | 109 |

| 5.5. Sin    | nulation and Experimental Results                                  | 111 |

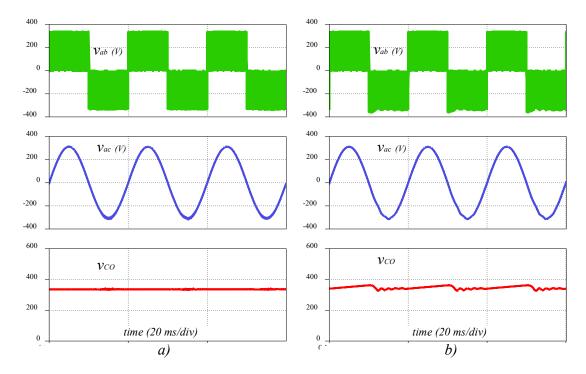

| 5.5.1.      | Simulation Results                                                 | 113 |

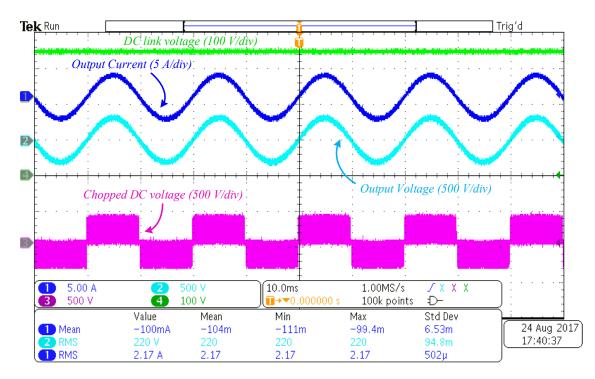

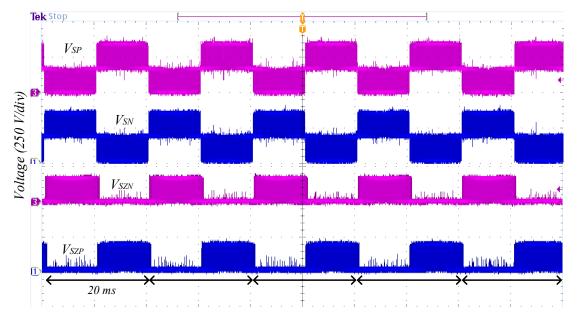

| 5.5.2.      | Experimental Results                                               | 115 |

| 5.6. Sur    | mmary and Conclusions                                              | 125 |

| Chapter 6 C | onclusion and Future Work                                          | 127 |

| 6.1. Th     | esis Summary and Conclusions                                       | 128 |

| 6.2. Fu     | ture Work Avenues                                                  | 129 |

| Appendix    | A                                                                  | 133 |

| Appendix    | В                                                                  | 137 |

| Appendix    | C                                                                  | 139 |

| Bibliograp  | hy                                                                 | 145 |

This page has been intentionally left blank

## List of Figures

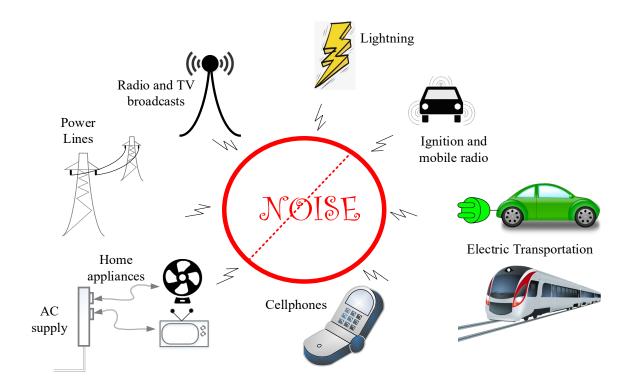

| Figure 1.1. Natural/man-made common sources of EMI                                              |

|-------------------------------------------------------------------------------------------------|

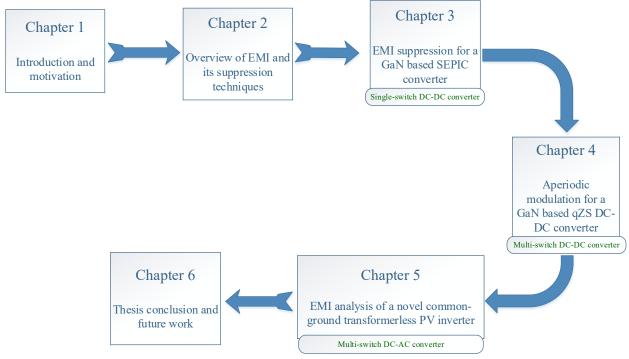

| Figure 1.2. Thesis outline                                                                      |

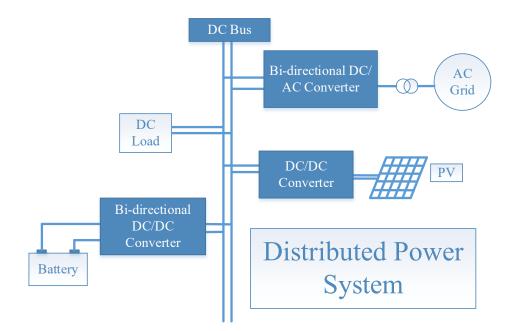

| Figure 2.1. A typical example of a distributed power system (DPS) with DC bus                   |

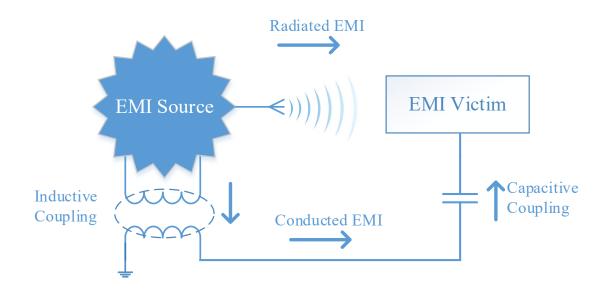

| Figure 2.2. EMI coupling modes                                                                  |

| Figure 2.3. Types of conducted EMI10                                                            |

| Figure 2.4. Comparative overview of switching transients between a) Silicon and b) wide-bandgap |

| switching devices                                                                               |

| Figure 2.5. a) A LISN and b) its functionality [15]14                                           |

| Figure 2.6. Generic limits based on CISPR-25 [22]                                               |

| Figure 2.7. A broad classification of EMI suppression techniques                                |

| Figure 2.8. A classification of Conducted EMI suppression techniques                            |

| Figure 2.9. The switching process for hard switching (a and b), and soft switching (c and d)21  |

| Figure 2.10. A classic buck converter and its associated waveforms                              |

| Figure 2.11. A generic switching signal used to drive the switches of a power converter         |

| Figure 2.12. Spectrum of an unmodulated signal compared with a frequency-modulated sinusoidal   |

| signal [45]                                                                                     |

| Figure 2.13. Spreading of harmonics leading to overlap                                          |

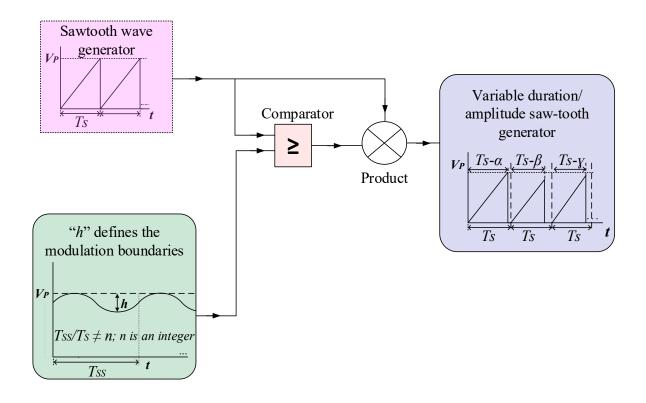

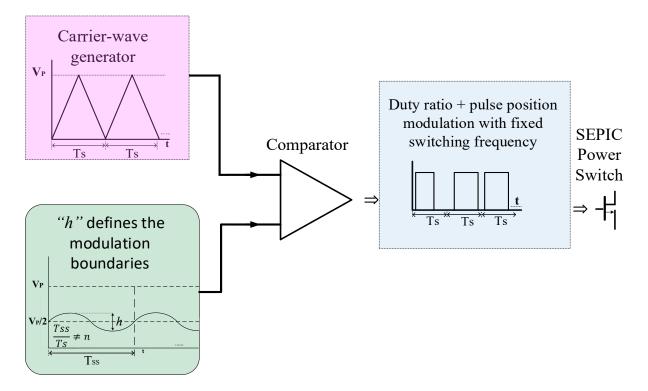

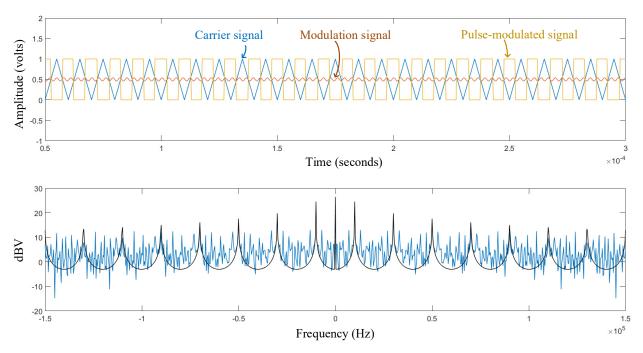

| Figure 3.1. Scheme showing generation of the aperiodic carrier signal                           |

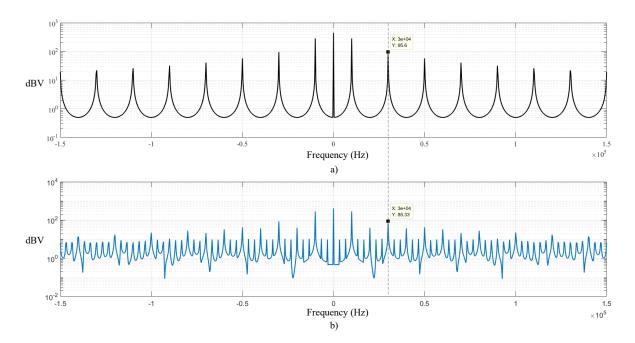

| Figure 3.2. Frequency spectrum of a) simple $qt$ and b) aperiodic $q(t)$                        |

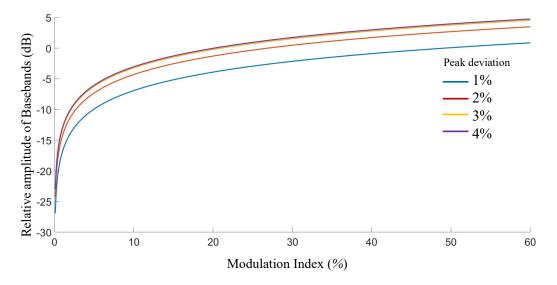

| Figure 3.3. Relative amplitude of basebands vs modulation index (%)                             |

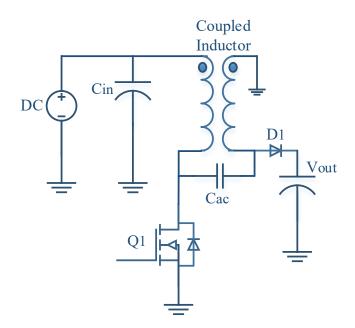

| Figure 3.4. Coupled-Inductor-based SEPIC converter for LED driver application                   |

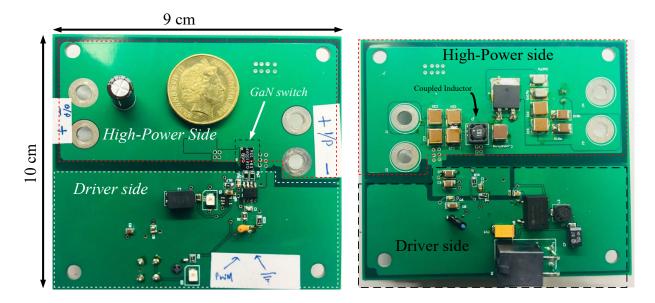

| Figure 3.5. 4-layer PCB layout showing isolated driver and power circuitry                      |

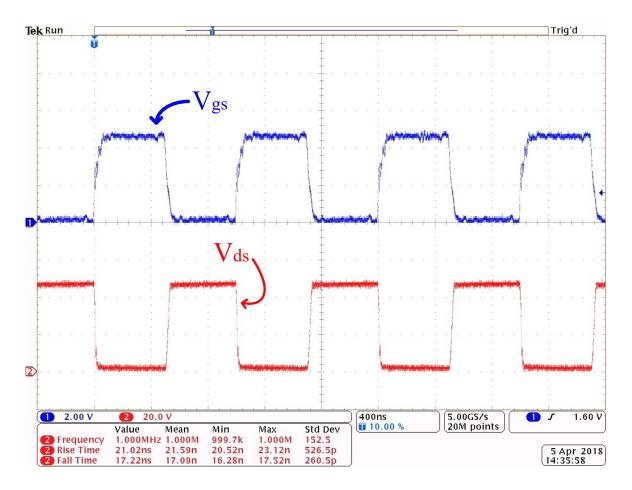

| Figure 3.6. Comparative preview of the gate driving signal with the drain-source voltage of     |

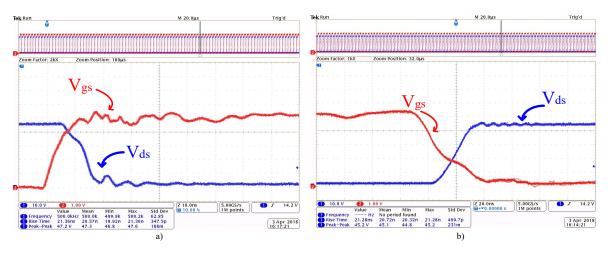

| GS61008P                                                                                        |

| Figure 3.7. Vds and Vgs for a) turn-on and b) turn-off transient                                |

| Figure 3.8. Aperiodic PWM signal generation framework for SEPIC converter                       |

| Figure 3.9. Fourier transform comparing the spectra of the periodic and aperiodic pulse modulations $\left( \frac{1}{2} \right)$ |

|----------------------------------------------------------------------------------------------------------------------------------|

| generated by a triangular carrier                                                                                                |

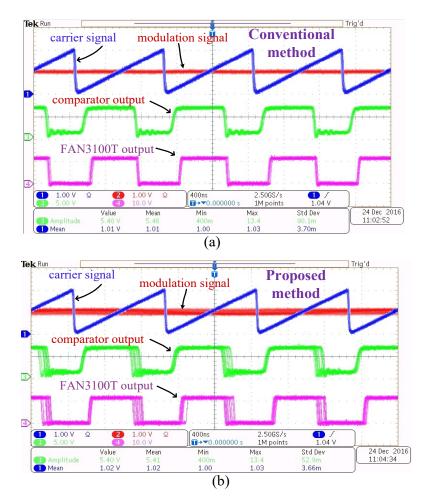

| Figure 3.10. Key waveforms illustrating generation of switching patterns using (a) conventional and                              |

| (b) sawtooth carrier-based proposed method47                                                                                     |

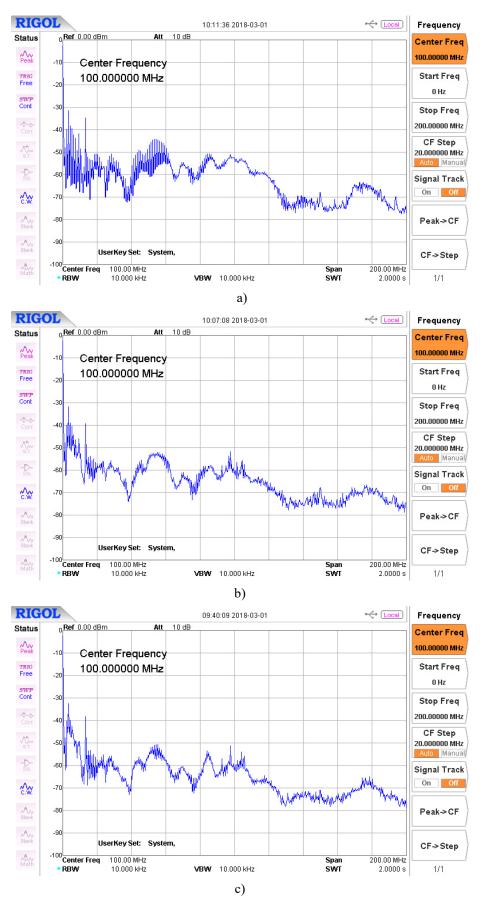

| Figure 3.11. Spectrum of conducted EMI (0 $\sim$ 200 MHz) for a) reference PWM, b) aperiodic                                     |

| modulation A and c) aperiodic modulation B                                                                                       |

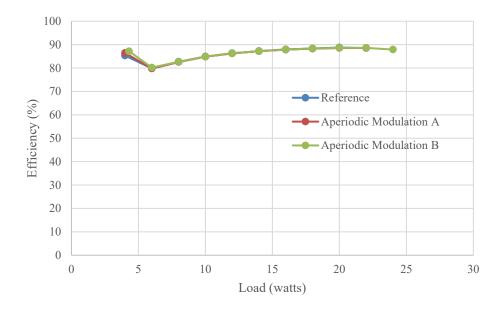

| Figure 3.12. Efficiency vs load index for the reference and proposed modulation schemes                                          |

| Figure 3.13. Voltage-gain index for the reference and proposed modulation schemes                                                |

| Figure 3.14. EMI spectra for various switching frequencies                                                                       |

| Figure 3.15. a) Envelope zoomed in to show b) its constituent harmonics                                                          |

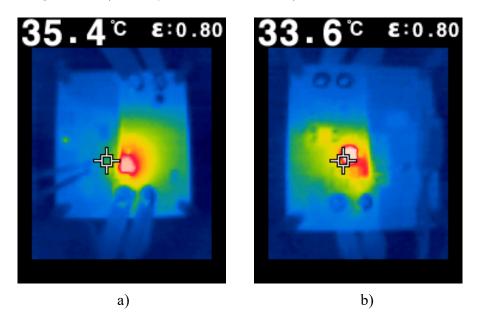

| Figure 3.16. Top thermal image capture for the SEPIC converter with a) reference and b) aperiodic                                |

| modulation scheme                                                                                                                |

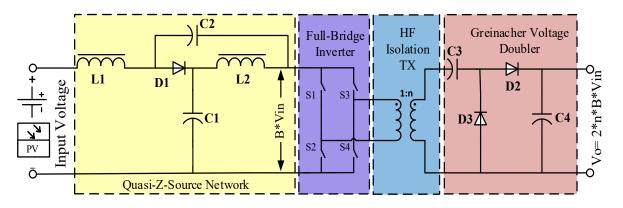

| Figure 4.1. An isolated qZS DC-DC converter [44]                                                                                 |

| Figure 4.2. Cascode hybrid-GaN structure [77]                                                                                    |

| Figure 4.3. Reference modulation schemes containing a) active and shoot-through states only [78],                                |

| and (b) active, zero and shoot-through states [74]60                                                                             |

| Figure 4.4. Block diagram to implement modulation scheme containing a) active and shoot-through                                  |

| states only, and (b) active, zero and shoot-through states                                                                       |

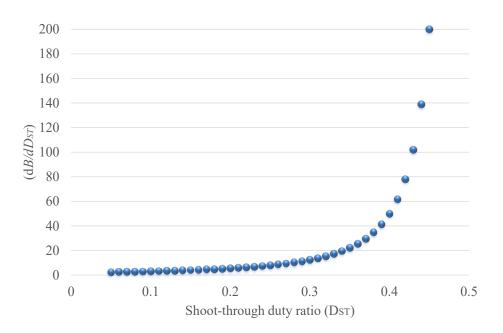

| Figure 4.5. Rate of change of gain w.r.t. shoot-through duty ratio for a quasi-Z-source [71]63                                   |

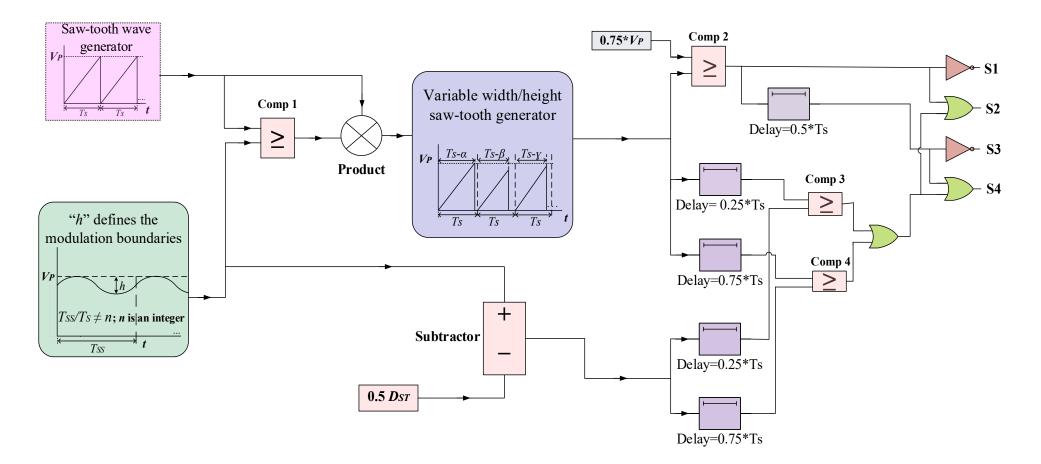

| Figure 4.6. Logic diagram to generate the aperiodic version of reference modulation scheme A [71].                               |

|                                                                                                                                  |

| Figure 4.7. Logic diagram to implement the aperiodic version of the improved modulation scheme                                   |

| B [44]                                                                                                                           |

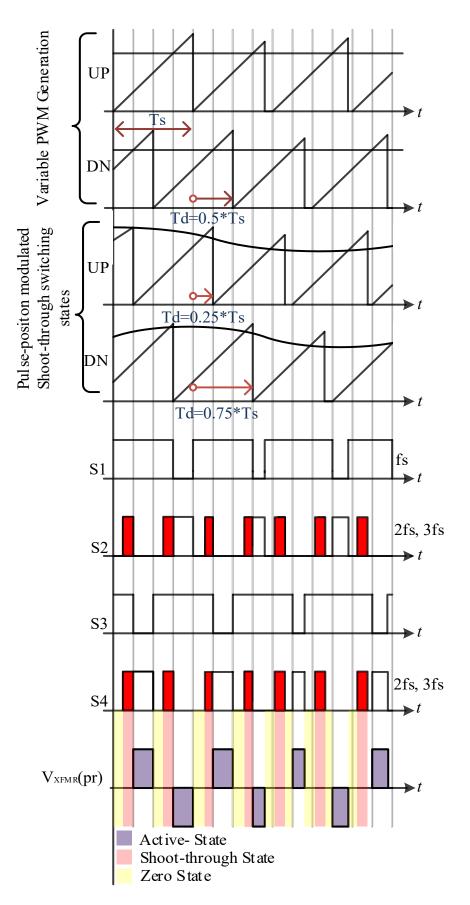

| Figure 4.8. Switching sequence for an aperiodic modulation scheme for a qZS DC-DC converter. 69                                  |

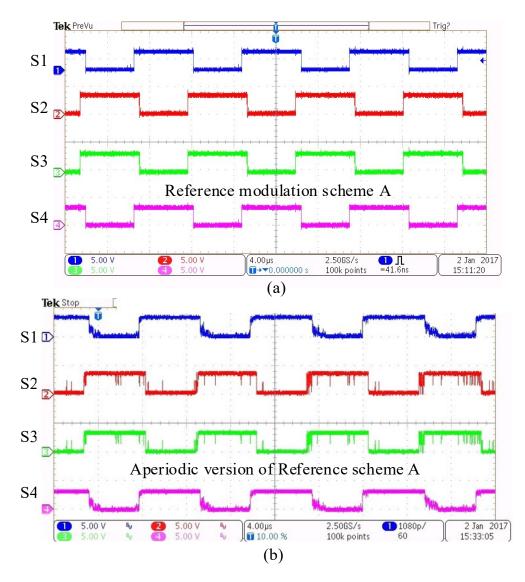

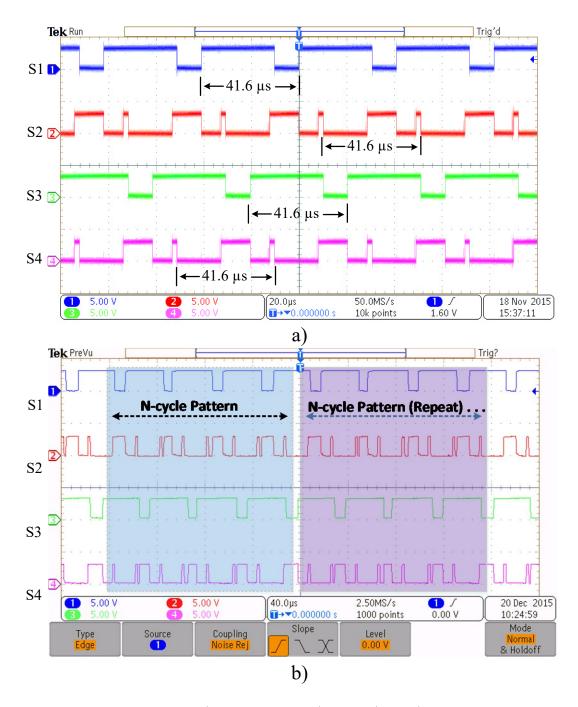

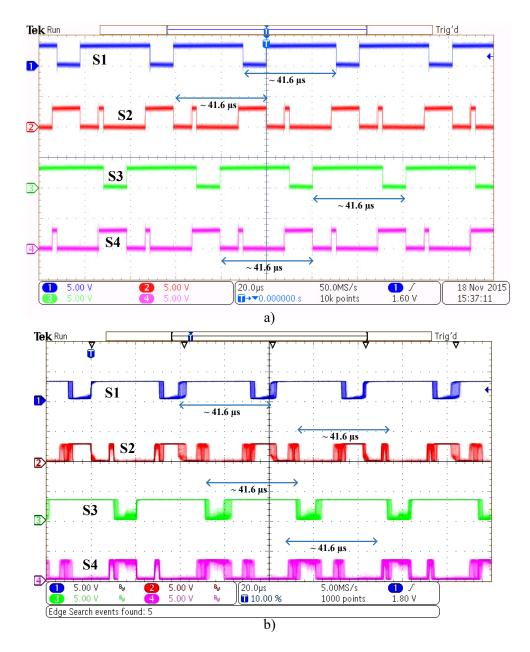

| Figure 4.9. Switching pattern for a) reference scheme A and b) its aperiodic version71                                           |

| Figure 4.10. Switching pattern for a) reference scheme (Fig. 5.3 b) and b) its quasi-periodic version.                           |

|                                                                                                                                  |

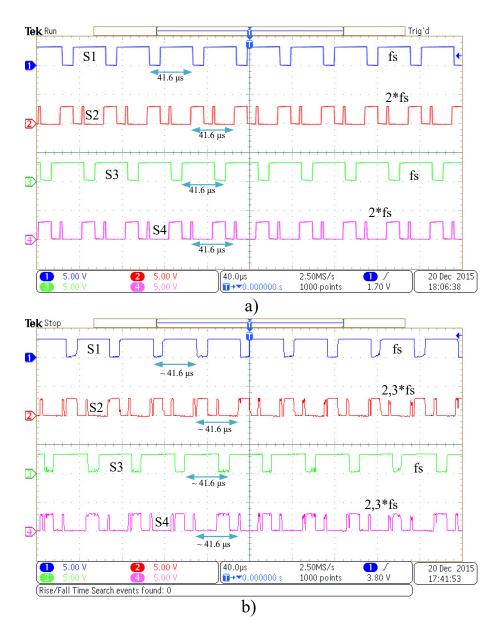

| Figure 4.11. Switching pattern for a) reference scheme B and b) its aperiodic version73                                          |

| Figure 4.12. Wider temporal representation of switching pattern for a) reference scheme B and b)                                 |

| its aperiodic version74                                                                                                          |

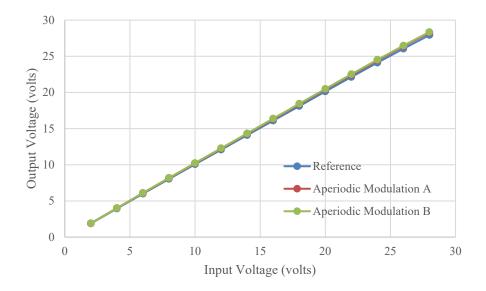

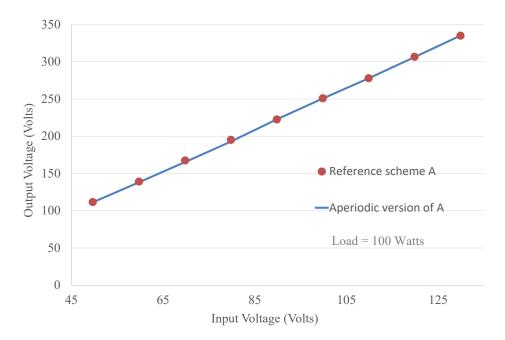

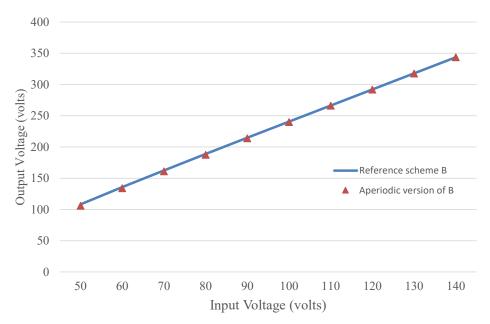

| Figure 4.13. Voltage gain index for reference modulation scheme A and its aperiodic version75                    |

|------------------------------------------------------------------------------------------------------------------|

| Figure 4.14. Voltage gain index for reference modulation scheme B and its aperiodic version76                    |

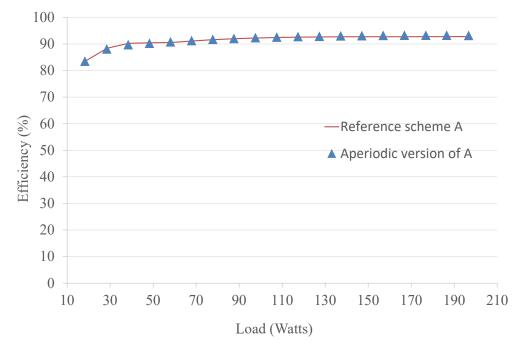

| Figure 4.15. Efficiency vs load index for reference modulation scheme A and its aperiodic version                |

| for fs=100 kHz76                                                                                                 |

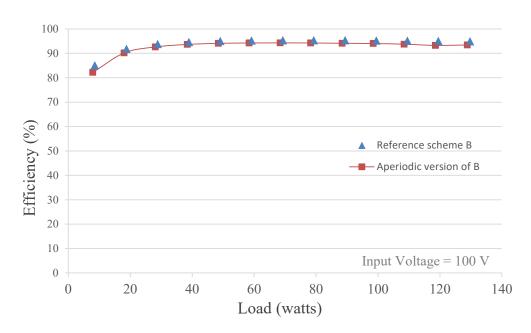

| Figure 4.16. Efficiency vs load index for reference modulation scheme B and its aperiodic version                |

| for fs=24 kHz                                                                                                    |

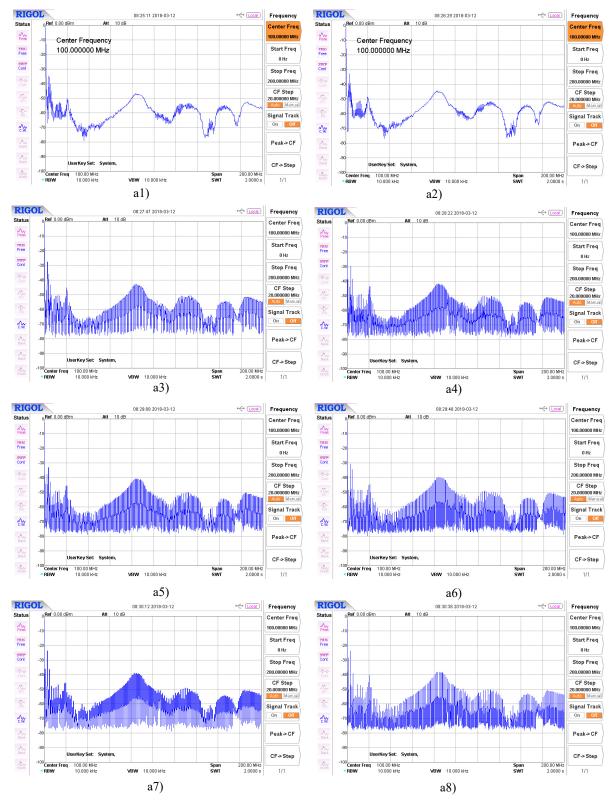

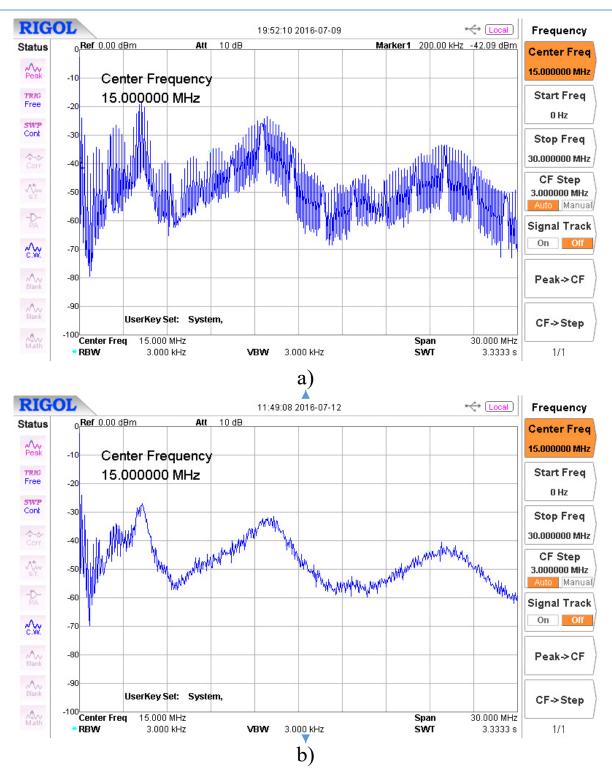

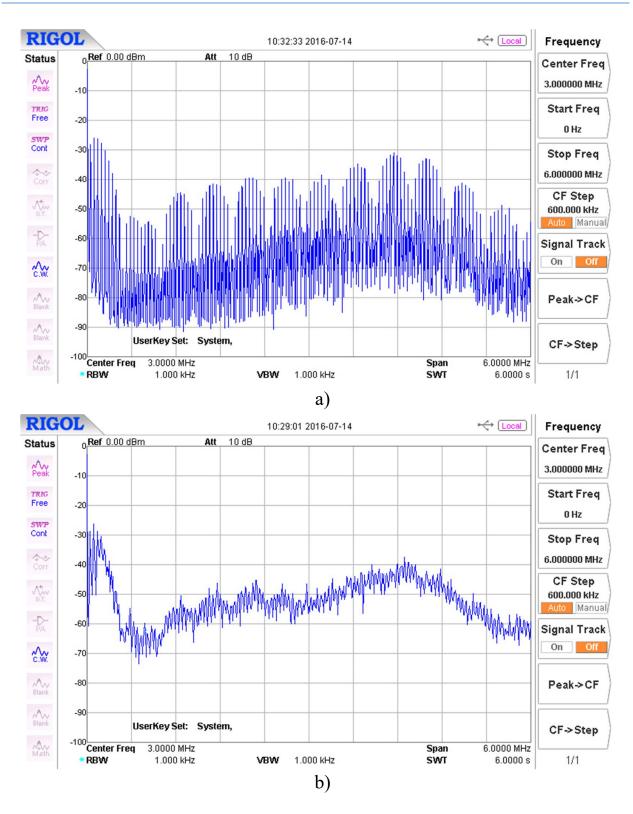

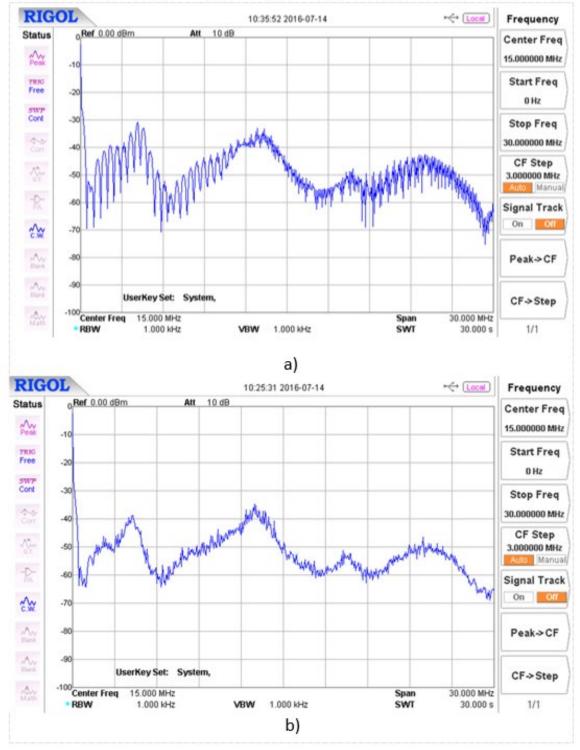

| Figure 4.17. Spectrum of conducted EMI $[0\sim 6~{\rm MHz}]$ for: a) Reference scheme A, and b) its aperiodic    |

| version                                                                                                          |

| Figure 4.18. Spectrum of conducted EMI [0 $\sim$ 30 MHz] for a) Reference scheme A, and b) its                   |

| aperiodic version                                                                                                |

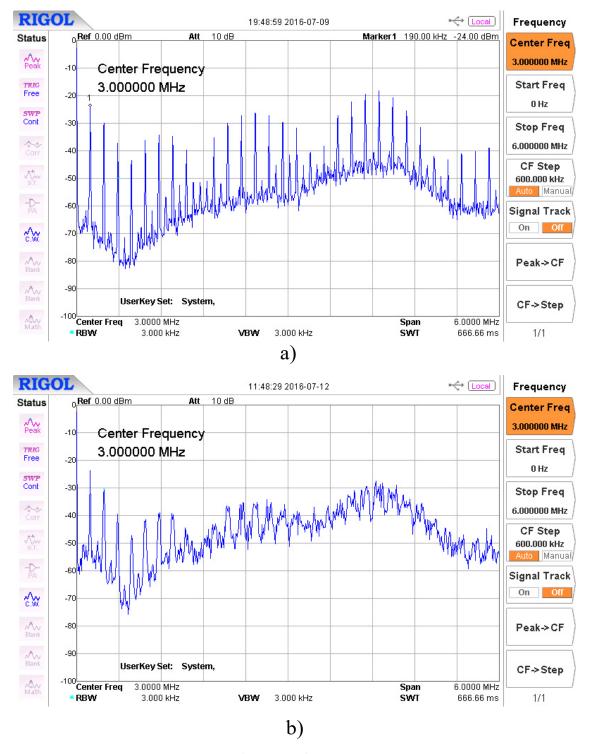

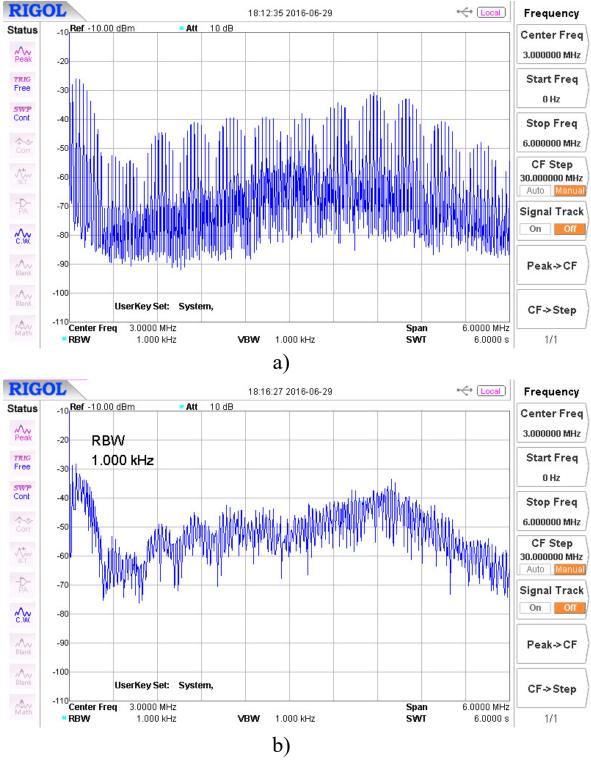

| Figure 4.19. Spectrum of conducted EMI $[0 \sim 6 \text{ MHz}]$ , for: a) Reference scheme B, and b) its quasi-  |

| periodic version                                                                                                 |

| Figure 4.20. Spectrum of conducted EMI $[0 \sim 30 \text{ MHz}]$ , for: a) Reference scheme B, and b) its quasi- |

| periodic version                                                                                                 |

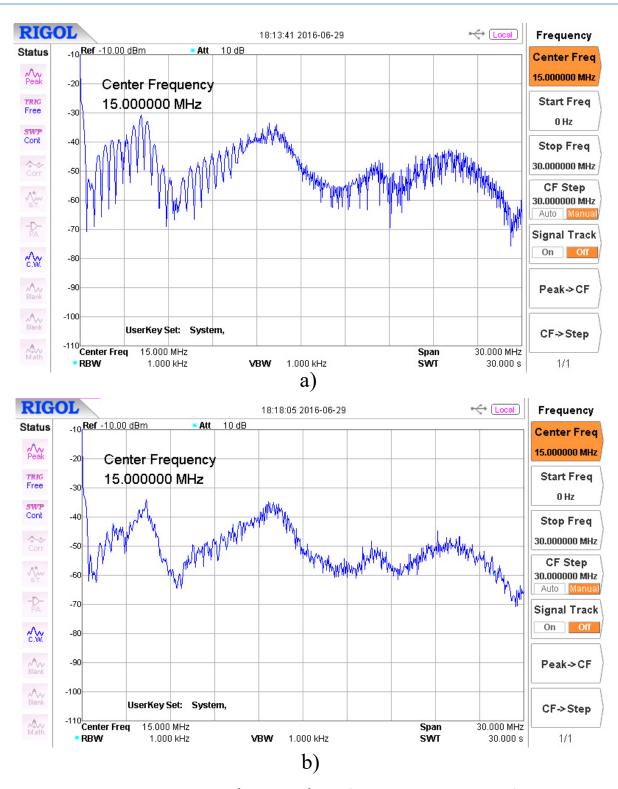

| Figure 4.21. Spectrum of conducted EMI $[0 \sim 6 \text{ MHz}]$ , for: a) Reference scheme B, and b) its         |

| aperiodic version                                                                                                |

| Figure 4.22. Spectrum of conducted EMI [0 $\sim$ 30 MHz], for: a) Reference scheme B, and b) its                 |

| aperiodic version                                                                                                |

| Figure 5.1. (a) Proposed transformerless common-ground topology and (b) corresponding unipolar                   |

| SPWM                                                                                                             |

| Figure 5.2. Charging of the virtual DC bus capacitor                                                             |

| Figure 5.3. Positive Cycle active state of the proposed topology                                                 |

| Figure 5.4. Positive Cycle zero state of the proposed topology                                                   |

| Figure 5.5. Negative Cycle active state of the proposed topology                                                 |

| Figure 5.6. Negative Cycle zero state of the proposed topology                                                   |

| Figure 5.7. Equivalent model for analysis of common-mode voltage and leakage current for the                     |

| proposed converter                                                                                               |

| Figure 5.8. PI control for the proposed topology                                                                 |

| Figure 5.9. Key simulated waveforms ( $VPV = 340$ VDC, $vav = 220$ V) a) with PI and b) without                  |

| PI control                                                                                                       |

| Figure 5.10. Simulated waveforms for output voltage and capacitor charging current a) with and b)     |

|-------------------------------------------------------------------------------------------------------|

| without PI control                                                                                    |

| Figure 5.11. a) Analysis of capacitor charging current; sub-classification of negative (active) state |

| when b) $SC$ is ON (active state 1) and c) $SC$ is OFF (active state 2)108                            |

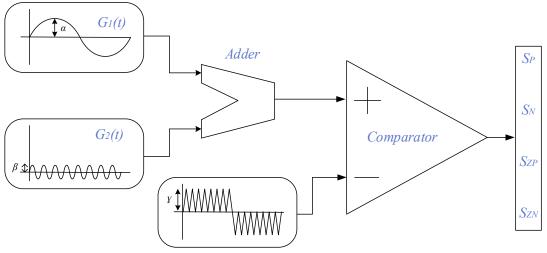

| Figure 5.12. Aperiodic implementation of SPWM                                                         |

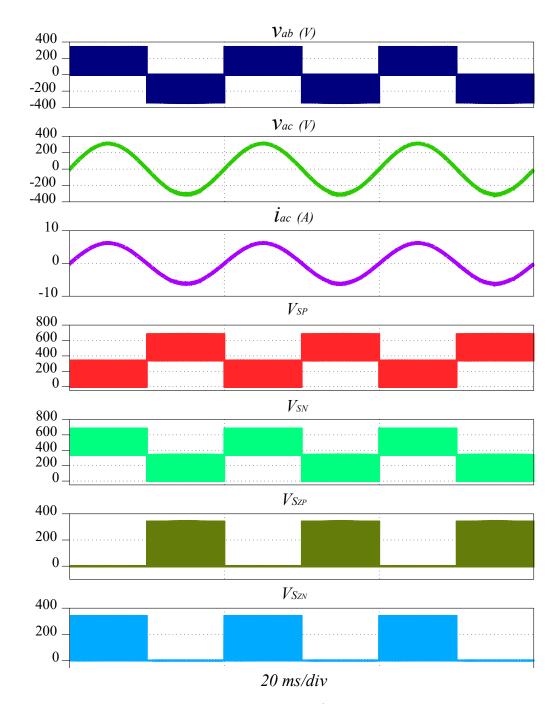

| Figure 5.13. Key simulated waveforms for output voltage/current, unipolar voltage across filter and   |

| switch stresses                                                                                       |

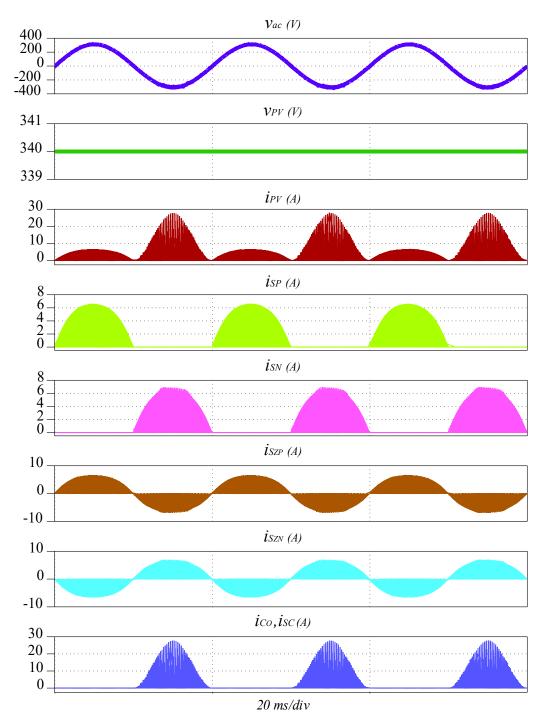

| Figure 5.14. Key simulated waveforms for current stress across various switches                       |

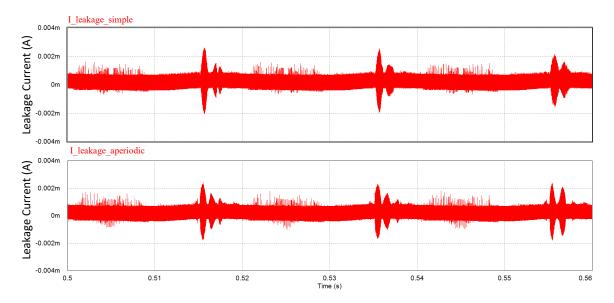

| Figure 5.15. Leakage current pattern for the proposed inverter topology for simple and aperiodic      |

| modulation schemes                                                                                    |

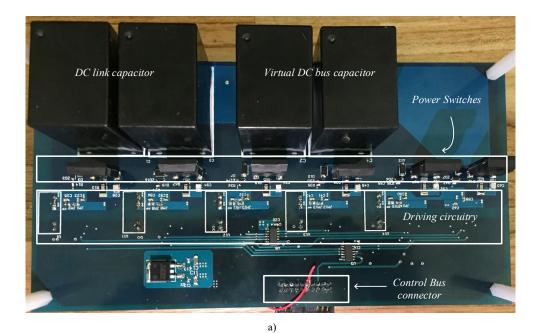

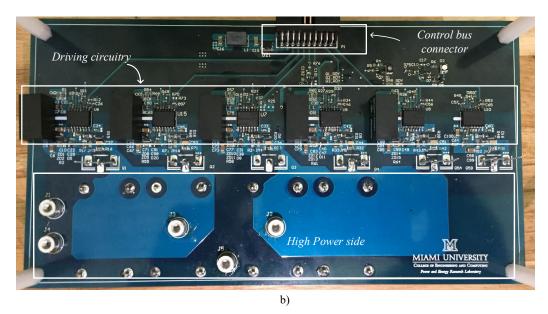

| Figure 5.16. Picture of both sides of the laboratory prototype of the proposed topology 115           |

| Figure 5.17. Key experimental results for the proposed topology                                       |

| Figure 5.18. Switch voltage stress for the switches operated in the SPWM manner                       |

| Figure 5.19. Key waveforms comparing operation of a) simple vs b) aperiodic SPWM117                   |

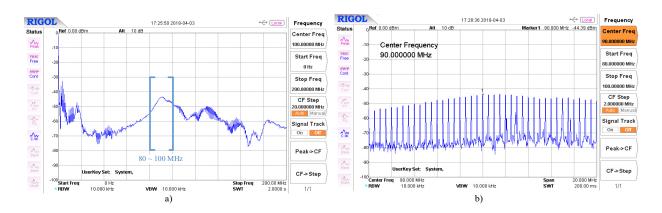

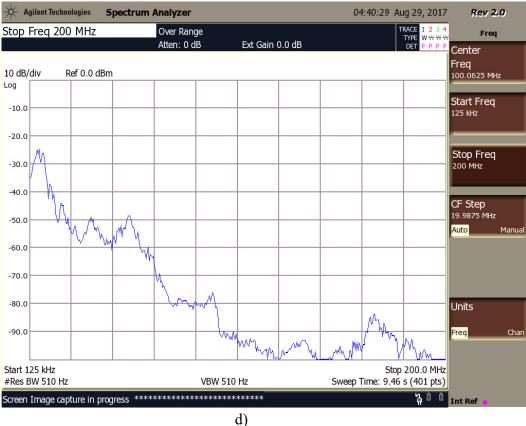

| Figure 5.20. Spectrum of conducted EMI for a) simple SPWM (125 kHz $\sim 100$ MHz), b) aperiodic      |

| SPWM (125 kHz $\sim 100$ MHz), c) simple SPWM (125 kHz $\sim 200$ MHz) and d) aperiodic SPWM (125     |

| $kHz \sim 200 \text{ MHz}$ )                                                                          |

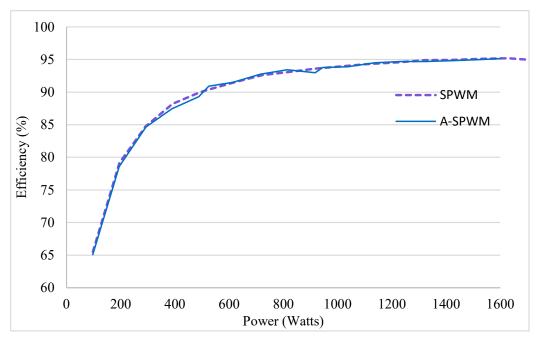

| Figure 5.21. Efficiency vs load performance comparison for simple vs aperiodic SPWM                   |

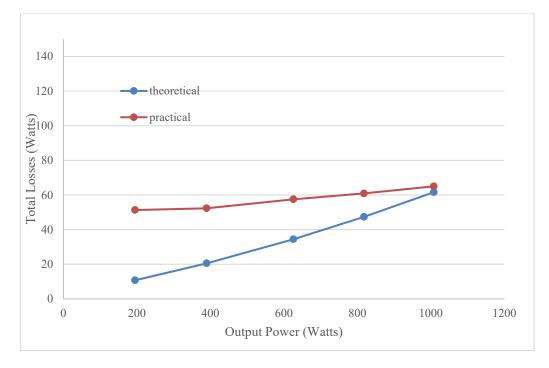

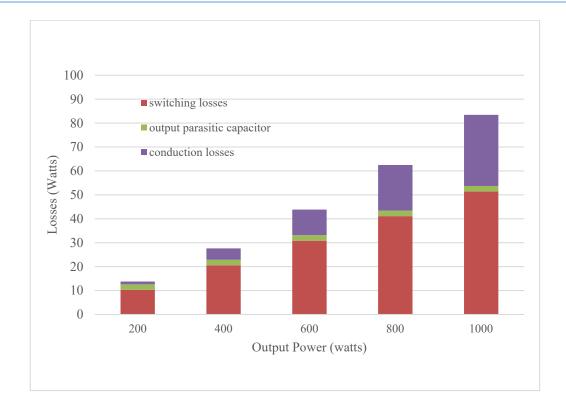

| Figure 5.22. Comparison of theoretical vs practical losses for different load values                  |

| Figure 5.23. Efficiency vs load performance comparison for simple vs aperiodic SPWM                   |

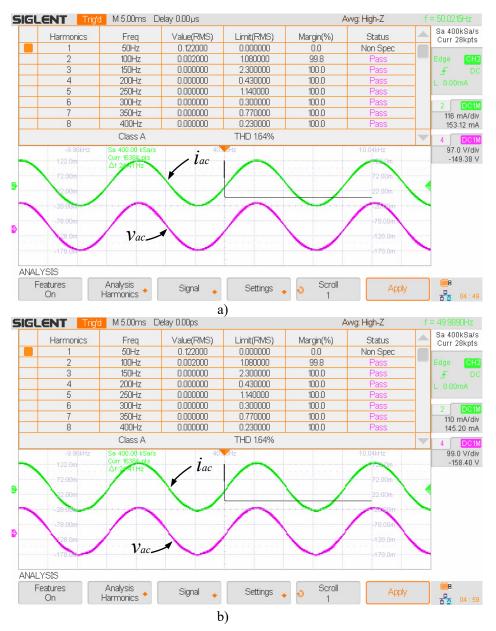

| Figure 5.24. THD measured for the output current waveform for a) simple SPWM and b) aperiodic         |

| SPWM                                                                                                  |

| Figure 6.1. Novel 5-level transformerless inverter topology [120]                                     |

## List of Tables

| Fable 2.1. Classification of various Spread-spectrum modulation methods                       | . 25 |

|-----------------------------------------------------------------------------------------------|------|

| Fable 2.2. Comparison of periodic, aperiodic and random signals                               | . 30 |

| Fable 3.1. Design Parameters for SEPIC converter                                              | . 41 |

| Table 3.2. Key Parameters for Periodic and Aperiodic switching signals                        | . 48 |

| Fable 3.3. Key Parameters for Periodic and Aperiodic PWM signals                              | . 51 |

| Fable 4.1. Parameters and components for qZS prototype                                        | . 70 |

| Table 4.2. Comparison of quasi-periodic and aperiodic modulation in terms of efficiency, volt | age  |

| gain, regulation and EMI suppression                                                          | . 84 |

| Fable 5.1. Summary of the switching states of the proposed topology                           | . 98 |

| Fable 5.2. Comparison of Proposed Topology with various other transformerless topologies.     | 101  |

| Fable 5.3. Parameters and Components Used in Simulation.                                      | 113  |

This page has been intentionally left blank

## List of Publications

#### Patents

1. S. U. Hasan and G. E. Town, "Modulation method and apparatus to reduce EMI in a power converter," AU patent WO2017120644 A1, Jan. 15, 2016.

#### **Refereed Journal Papers**

- S. U. Hasan and G. Town, "An Aperiodic Modulation Method to Mitigate Electromagnetic Interference in Impedance Source DC-DC Converters," in IEEE Transactions on Power Electronics, 2017 (early access). [Chapters 2 and 4]

- S. U. Hasan, H. A. Hassan, M. J. Scott, Y. Siwakoti and G. E. Town, "Common-Ground Transformerless Inverter with virtual DC bus concept for Single-Phase PV Systems", Journal of Emerging and Selected Topics in Power Electronics (JESTPE), 2018 (under review), Manuscript ID: JESTPE-2018-04-0386. [Chapter 5]

- 4. S. U. Hasan, H. A. Hassan and G. E. Town, "An aperiodic modulation strategy to reduce peak EMI in a high frequency Coupled Inductor based SEPIC converter". (In draft, to be submitted to JESTPE). [Chapters 2 and 3]

#### **Refereed Conference Papers**

- 5. S. U. Hasan and G. E. Town, "A Quasi-periodic modulation strategy to mitigate EMI for a GaN-based Quasi-Z-Source DC-DC converter", IEEE Energy Conversion Congress and Expo (ECCE), USA, 2016. [Chapters 2 and 4]

- S. U. Hasan and G. E. Town, "An FPGA-based aperiodic modulation strategy for EMI suppression in quasi-Z-source DC-DC converters", IEEE International Symposium on Circuits and Systems (ISCAS), USA, 2017. [Chapters 2 and 4]

- S. U. Hasan, Y. R. Kafle and G. E. Town, "Aperiodic pulse-modulation technique to reduce peak EMI in impedance-source DC-DC converters", IEEE Energy Conversion Congress and Expo (ECCE), USA, 2017. [Chapters 2 and 4]

- 8. S. U. Hasan, Y. R. Kafle and G. E. Town, "Simple spread-spectrum pulse-modulation technique for EMI mitigation in power converters", Australasian Universities Power Engineering Conference (AUPEC), Australia, 2017. [Chapters 2 to 4]

- S. U. Hasan, B. Shaffer, H. A. Hassan, M. J. Scott, Y. Siwakoti and G. E. Town, "Common-ground transformerless inverter for solar photovoltaic module", IEEE Applied Power Electronics Conference and Exposition (APEC), USA, 2018. [Chapter 5]

#### Other Co-authored Publications during PhD Candidature

- Y. R. Kafle, S. U. Hasan and G. E. Town, "A new PWM shoot-through control technique to reduce switching losses in impedance source DC/DC converters", IEEE Energy Conversion Congress and Expo (ECCE), USA, 2017.

- 11. Y. R. Kafle, S. U. Hasan, M. Kashif, J. Hossain and G. E. Town, "A new PWM Shoot-through control for voltage-fed quasi-Z-source DC/DC converters", IEEE International Telecommunications Energy Conference (INTELEC), Australia, 2017.

- B. Shaffer, H. A. Hassan, M. J. Scott, S. U. Hasan, G. E. Town and Y. Siwakoti, "A common-ground single-phase five-level transformerless boost inverter for photovoltaic applications", IEEE Applied Power Electronics Conference and Exposition (APEC), USA, 2018.

- Y. R. Kafle, G. E. Town and S. U. Hasan, "Quasi-Z-source based Bidirectional DC-DC Converter and its Control strategy", Journal of Power Electronics (JPE), 2018 (under review), Manuscript ID: JPE-18-04-096 (0001).

## Chapter 1 Introduction and Motivation

#### 1.1. Overview and Significance of the Research Topic

Given that global energy demands are ever-increasing and fossil fuels are no longer 'infinite', the scientific community has started utilizing renewable energy sources as power generation sources. It is thus timely to develop and implement sophisticated, efficient and cost-effective energy generation, provision and utilization systems. Power Electronics provides the key enabling infrastructure which continues to develop and be able to integrate in electric power generation and utilization. It is believed that more than 30% of the generated electric power flows through the power electronics, and this number is expected to increase up to 80% by the year 2030 [1].

In the last seven decades, the integration of a wide range of power electronic converters has been rapidly increasing in our daily lives as well as in industries. Starting from consumer products such as portable battery banks, laptop adapters, electric vehicles, and now public utilities, the power electronics field finds wide-ranging applications. Moreover, the semiconductor manufacturing industry has also boomed in recent decades and can now provide the most sophisticated products. This has undoubtedly increased our expectations regarding the size, efficiency, cost and compatibility of power converters.

Recent developments in the semiconductor manufacturing industry have pushed siliconbased semiconductor technology to its theoretical limits which is not enough for the modern power conversion applications and expectations. These requirements include lower on-state resistance ( $R_{DS(ON)}$ ), higher reverse blocking voltage, better thermal performance and ability to be switched at relatively higher switching frequencies, in the MHz range [2]. Wide Bandgap (WBG)-based power semiconductor materials such as Gallium Nitride (GaN) and Silicon Carbide (SiC) have been introduced to meet the aforementioned requirements. The advent of WBG semiconductor devices has triggered a new research stream leading to the utilization of planar magnetics, switched capacitors and resonance techniques to achieve soft-switching and optimized printed circuit board (PCB) design. It means utilizing this emerging technology in the best way possible.

Rapidly changing voltages and currents in a power converter lead to noise emissions and, as the integration of power converters keeps on increasing rapidly, we are now virtually surrounded by power electronics generated noise sources. This is in addition to some noise sources based on natural phenomena. Increased noise is a major concern associated with power converters and the presented research examines this aspect of power converters. Fig. 1.1 illustrates a typical noise environment.

Figure 1.1. Natural/man-made common sources of EMI.

#### **1.2.** Problem Statement and Research Motivation

Semiconductor switches are considered to be the heart of a power converter. These switches are properly selected and operated along with various other passive components (such as inductors and/or capacitors) to ensure optimal operation for a given application. In power electronic conversion, switching is utilized to achieve the required voltage(s) and current(s) in accordance with particular applications. In steady-state operation, the duty cycle and switching frequency are kept constant, which leads to voltage and current transitions, resulting in electromagnetic interference (EMI). The harmonic powers of the input current and output voltage, hence can be seen as concentrated on multiples of the switching frequency at which it is operated [3]. WBG materials on one hand help to attain better performance in terms of efficiency, thermal stability and high power density, but on the other hand, due to the higher switching speeds ( $\sim ns$ ) as compared to their silicon counterparts, a broadband harmonic power distribution can be seen. Hence, WBG power devices can be seen as a double-edged sword which can realize the most sophisticated power conversion practices, but on the other hand, increase the spectral peaks and its bandwidth [4], [5]. With more power electronics research and development underway, various electromagnetic compatibility (EMC) standards [6] have been defined by the standardization agencies worldwide. These have sort to keep the noise levels under defined thresholds. Therefore, with the emergence of WBG power conversion technology, addressing the EMI matter has become more crucial.

#### **1.3.** Objectives and Scope of Dissertation

This dissertation proposes a new approach to implementing an aperiodic modulation technique for driving the switch(es) in a power converter, leading to the suppression of the spectral peaks of the associated harmonic power. The proposed methodology is implementable flexibly via both analog and digital practices. Moreover, the proposed framework is compliantly extended and applied to single-switch and multi-switch power converters. This dissertation also investigates the core performance parameters of power converters such as efficiency, voltage gain etc. in relation to the applied modulation methodology. It is pertinent to mention here that a more heuristic approach is adopted for this dissertation to explore the engineering aspects of power converters. Nevertheless, the basic analyses of the spread-spectrum modulation techniques have been added to familiarize the reader with the related generalizations. Moreover the EMI measurements have not been compared with the typical EMC standards due to the laboratory setup constraints.

#### **1.4.** Dissertation Outline

This dissertation is organized into six chapters including the Introduction and motivation (Chapter 1). The contents of Chapters 2-6 are briefly described here:

Chapter 2 provides the background context of this work. The reader can get a general idea about EMI in power converters, the traditional techniques to suppress EMI noise in power converters and an overview of the various EMI measurement techniques.

**Chapter 3** presents a framework for implementing an aperiodically modulated switching signal which is then applied to a GaN high electron mobility transistor (HEMT)-based single-ended primary-inductor converter (SEPIC) to investigate the EMI suppression. The spectral analysis of the switching signal is also discussed to better understand the harmonics spreading phenomenon. Moreover, as the SEPIC converter is designed to be used as an LED driver and concur with a GaN switch, the converter is designed to be operated at high switching frequency, and hence various design guidelines/insights are also outlined in this chapter. Finally, experimental results such as efficiency and voltage-gain index are explained to justify the usefulness of the proposed technique.

**Chapter 4** extends the proposed aperiodic modulation methodology to generate a coordinated set of hybrid pulse-modulation signals for application to a cascode GaN HEMT-based quasi-Z-source (qZS) DC-DC converter. The characteristic shoot-thorough states are specifically considered in this case to ensure a constant gain. Both quasi-periodic and aperiodic modulation techniques are applied to investigate the EMI suppression. The voltage gain and efficiency index are also presented to analyze the proposed technique's performance.

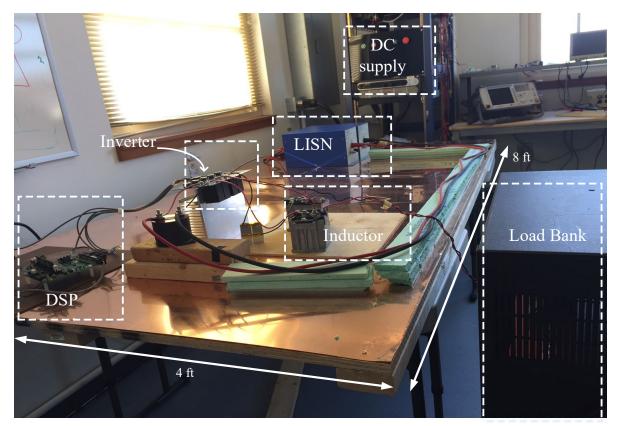

**Chapter 5** introduces a novel common-ground, transformerless inverter topology for photovoltaic (PV) systems, and various switching states and design insights are discussed. The proposed topology employs a double-charging process to charge a virtual DC bus capacitor through an inductor, hence making a topological contribution to EMI suppression. Additionally, an aperiodic modulation is compliantly applied to furthermore suppress the EMI. Finally, a comparison in terms of efficiency index, total harmonic distortion (THD) and various key waveforms is presented for a 1 kW prototype.

Finally, Chapter 6 concludes the dissertation and future work avenues are suggested.

Figure 1.2. Thesis outline

## Chapter 2

# An Overview of EMI and Its Suppression Techniques

This chapter is dedicated to the preliminary knowledge associated with EMI in power converters. A general overview of EMI along with its different types is discussed. Various EMC standards are also listed which confine the noise produced by various sources below specified limits in accordance with different applications. Moreover, the EMI measurement methods and techniques are discussed. Finally, an overview of EMI suppression techniques is given.

#### 2.1. EMI and EMC of Power Converters

All modern power converters can be viewed as a combination of reactive elements and power switches for energy storage and control respectively. The power switches are usually driven at a constant switching frequency with a constant or varying duty cycle, depending on the control strategy. Eventually, in the steady-state operation of a power converter, the duty cycle and frequency remain fixed and, due to their switching mode, the power converters are also referred to as switching power converters. Switching often results in large voltage and current transitions (high dv/dt and di/dt respectively), which in turn generate broadband electromagnetic emissions. This phenomenon is the basis of the EMI generated in power converters. Since high efficiency and high power density are major driving forces for modern power converters, the di/dt and dv/dt increase even more, and hence cause severe EMI problems.

Figure 2.1. A typical example of a distributed power system (DPS) with DC bus.

EMI is an unwanted disturbance caused by electrical and electronic devices which carry rapidly changing electrical (voltage and/or current) signals. EMI caused by any kind of source can affect (obstruct, interrupt or degrade) the operation of electronic equipment working nearby. A typical example of a distributed power system (DPS) with a DC bus is shown in Fig. 2.1. This architecture greatly facilitates the integration of a number of DC power sources and loads and so the system can have optimal operation. In such a DPS, since the various sources and loads are often connected in close proximity and each component can be regarded as an EMI source carrying voltage and current transitions, it is very important to minimize the interactions between the connected circuits. These can result from uncontrolled conducted or radiated EMI.

As more power electronic converters are being integrated and adopted in our daily lives, the emissions generated by any sort of source need to be kept under safe limits. This EMI consideration is not restricted to power converters, and various other issues have also been reported and researched. For example, the malfunctioning of an apnea monitor due to ambient EMI radiation [7]. A number of interesting and surprising issues have been reported in [8] including, military radios interfering with garage door openers, Russian satellite Geo-IK-2 possibly crashing due to external EMI and planes having inflight Wi-Fi facing more turbulence etc.

#### 2.1.1. Types of EMI

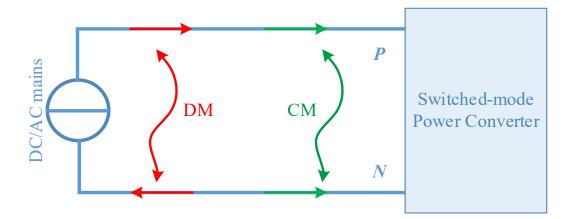

EMI can be classified on the basis of the way in which the electromagnetic field (produced by high di/dt and dv/dt) propagates. It is classified as conducted EMI and radiated EMI. The possible coupling modes are shown in Fig. 2.2.

#### i. Conducted EMI:

With conducted EMI, the propagation occurs via the physical conductors. Empirically, the conducted EMI has a frequency range from 10 kHz to 30 MHz [9], and it is further classified as common-mode noise or differential-mode noise. These two sub-classifications are based on the direction of the propagation. In the case of common-mode noise, the conduction occurs in the same direction through all the propagation paths. Common-mode (CM) noise always exists between the power line and the ground of a power electronic converter.

Figure 2.2. EMI coupling modes.

With differential-mode (DM) noise, the conduction is in different directions in two conduction lines. Differential-mode noise exists between the two power lines. The CM and DM noise are explained pictorially as follows:

Figure 2.3. Types of conducted EMI.

#### ii. Radiated EMI:

Radiated EMI is propagated without physical conductors. Radiated EMI is usually significant for the cases when a power converter is switched at a high frequency (>30 MHz). This is the case when various parts of a PCB may radiate the EMI, acting as an antenna [10]. There can be several high-frequency current loops in a power converter which can lead to radiated emissions [11], [12]. These include the main switch power loop, the gate drive loop, the loop across inductive components (inductor, coupled-inductor or transformer), loops across the rectifier etc.

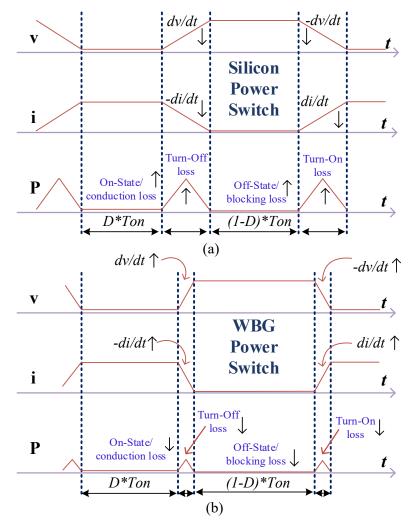

Figure 2.4. Comparative overview of switching transients between a) Silicon and b) wide-bandgap switching devices.

WBG power semiconductor devices, as compared to their silicon-based counterparts, with relatively low  $R_{DS(on)}$  and high reverse blocking capabilities, offer high-switching-frequency operation along with sharp switching transitions ( $t_{ON}$  and  $t_{OFF}$ ). These enable improved efficiency, lower conduction and switching losses, higher power density and small-sized passive filters. On the other hand, the sharp switching transients, though they reduce the switching losses, have larger di/dt and dv/dt as compared to ordinary silicon-based switches. Hence, the EMI issue becomes more severe in WBG-based power converters. Fig. 2.4 gives a pictorial view of how the switching transients are associated with the voltage and current alternations. A relative peak EMI behavior judgment can be made between a WBG-based power switch and a silicon power switch.

EMI is usually estimated with the power spectral density (PSD) of a signal (voltage and/or current) [13]. PSD gives the frequency distribution of the various constituent components of a signal. These components are also known as harmonics.

A Fourier-series expansion can be done to decompose a periodic signal into the sum of a set of sine and cosine functions. The general formula is given as:

$$f(t) = \frac{a_o}{2} + \sum_{m=1}^{\infty} (a_m \cos(m\omega t) + b_m \sin(m\omega t)), \qquad (2.1)$$

where

$$a_m = \frac{1}{\pi} \int_{-\pi}^{\pi} f(t) * \cos(mwt) dt , m = 0, 1, 2, 3, \dots$$

(2.2)

$$b_m = \frac{1}{\pi} \int_{-\pi}^{\pi} f(t) * \sin(mwt) dt, m = 0, 1, 2, 3, \dots$$

(2.3)

$\frac{a_o}{2}$  is the DC component and, other than this, the expression is a summation of sinusoidal functions. It is well known from the theory of Fourier analysis that, the more sinusoids are added up, the more exactly would their combination will add up to the original signal. In

the frequency domain, these sinusoids can be regarded as the harmonics. This implies that the more a signal has steep edges, the more broad its frequency band would be. Applying this concept to WBG-based power converters, the WBG switches make the voltage and current waveforms have steeper transitions, and hence a broadband spectrum is generated when high-speed WBG switches are used in a power converter. Moreover, as the switching frequency can be increased in WBG-based power converters, the spectral contents of the noise are also shifted to higher frequencies. Also, the noise magnitude depends on various additional factors such as operating power, the topology and type of applications etc. [4], [5].

### 2.1.3. EMI Measurement Methods

The EMC standards provide a set of attributes for the testing setup which may be difficult to replicate in a laboratory scale, therefore pre-compliance EMI testing is done for a product before it is sent for actual compliance testing. Since more than 50% of products fail EMC testing at the first time, the pre-compliance practice solves the hassle of re-sending a product for compliance testing and also saves money [14]. Depending on the EMI mode, i.e. conducted or radiated, various measurement procedures are followed. These are briefly described below:

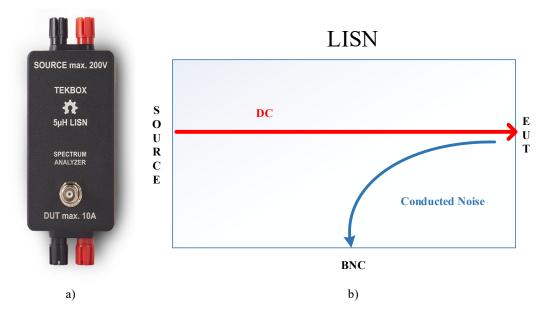

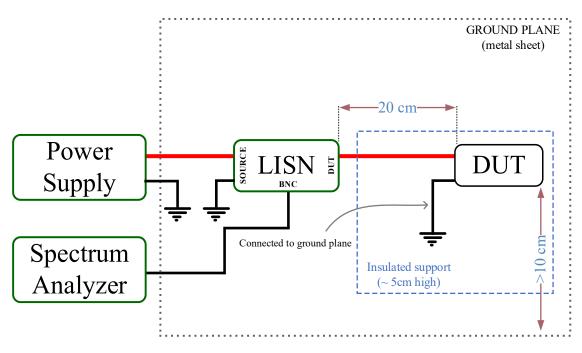

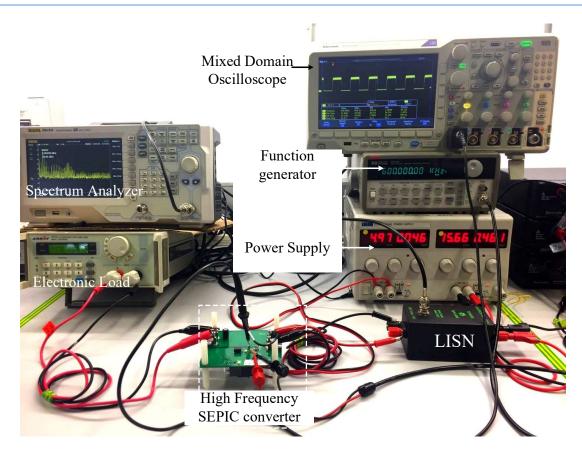

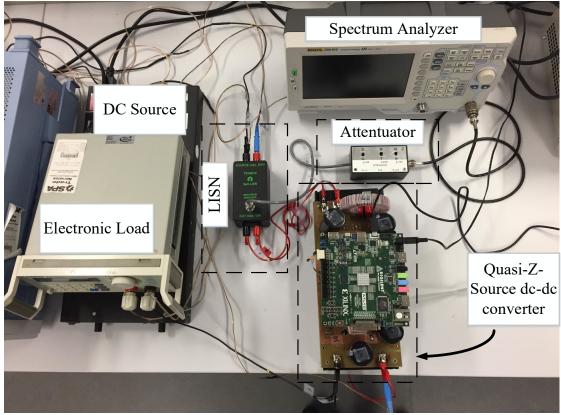

### 2.1.3.1. Line Impedance Stabilization Network (LISN)

A LISN device and its basic functionality are shown in Fig. 2.5. It is basically a coupling device to measure the conducted EMI present on the supply lines of a power converter. LISN is typically a low-pass filter inserted into the supply line of the equipment under test

(EUT) and hence the conducted noise present at the terminals of the EUT can be displayed and analyzed on a spectrum analyzer [15].

Figure 2.5. a) A LISN and b) its functionality [15].

A BNC connector output can be coupled to a spectrum analyzer with an appropriate attenuator (if required) to ensure safe operation of the spectrum analyzer. A typical setup for a conducted EMI measurement using a LISN as per the CISPR-25 standard is shown in Appendix A.1.

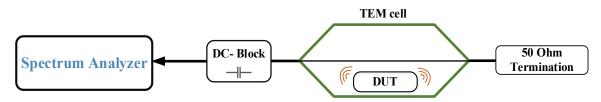

### 2.1.3.2. Transverse ElectroMagnetic (TEM)

An anechoic chamber is ideally used to analyze the radiated emissions of an EUT, and the standard compliance setup requires space, time, state-of-the-art equipment and similar resources. For this reason TEM cells are introduced to do the pre-compliance testing. A TEM cell is a stripline device which analyzes the radiated emissions of a EUT. It is not an ideal replacement for an anechoic chamber but, considering its feasible operation and comparatively low price, a TEM cell can be conveniently used to measure the radiated emission of a EUT for the pre-compliance testing. A setup for the radiated emission analysis is shown in Appendix A.2, where the EUT is placed inside a TEM cell, one of whose two ports is connected to a 50  $\Omega$  termination. The other port is then coupled to the spectrum analyzer to analyze the radiated emissions. The EUT placement directions and a look-up table are provided by the manufacturer of a TEM cell; this gives an idea about the potential success or failure of compliance testing [16].

### 2.1.3.3. Close Field Probes

Close field probes are also known as near field probes, and are specifically used for locating the origin of a source of noise emissions. For this reason, sometimes these probes are also called "sniffing" probes. These probes are offered by various manufacturers and are available in various frequency ranges. Since the electromagnetic field is the combination of an electric field (E-field) and a magnetic field (H-field), which are produced by voltage and current, respectively. Thus the close field probes are classified as E-field probes and H-field probes.

Typical sources of H-field emissions are power or signal cables, chipset pins, PCB traces or improperly grounded metal enclosures, therefore, H-field probes work on the principle of an inductively coupled coil which becomes energized when it arrives in the vicinity of the H-field. On the other hand, E-field emissions are based on high-impedance logic, example of which are unterminated cables and wires etc. The E-field probe is basically a small antenna [17].

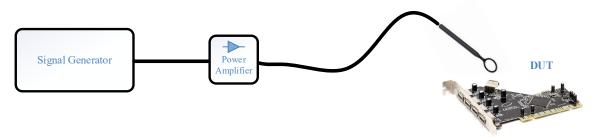

In brief, close field probes are a handy tool used for locating EMI sources in a device under test (DUT) or EUT. The probe can be moved around and aligned across different parts of a PCB to ensure that the EMI source is well located and can be shielded. Moreover, these probes can be used in the opposite manner, i.e. utilizing these probes as a signal source to localize a section of a DUT or EUT susceptible to various types of signals. Such a testing setup is shown in Appendix A.3.

### 2.1.4. EMC Standards

All the above-mentioned EMI measurement/observing techniques help to detect, locate and measure the EMI noise of an EUT or DUT. The EMI can be suppressed/handled according to various EMC standards. According to the International Electrotechnical Commission (IEC), EMC is defined as "The ability of an apparatus or system to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances to anything in that environment" [18]. In other words, an apparatus shall have enough "robustness" to work in an electromagnetic environment and keep its own emissions under the threshold limits as defined by various EMC standards.

With the widespread incorporation of power electronics worldwide, the relative EMI noise levels have increased to harmful levels. International standardization communities have agreed on various EMC standards which regulate/restrict the noise levels to continue the smooth operation of various equipment. In Europe, the organization designated to look after the EMC standards is the International Special Committee on Radio Interference, or CISPR. In the USA, it is the Federal Communications Commission (FCC), while in Australia the relevant organization is the Australian Communications and Media Authority (ACMA). Principally, EMC standards have the same goal, i.e. to ensure that a product complies with the defined noise levels. Eventually, there are different standards and requirements for different products, and these standards also vary in accordance with the geographical area like Australia, USA, Europe and Japan, etc. This also means that the manufacturers of various products which are specifically designed to be exported to other regions have to pass the relevant EMC compliance tests to get approval from its importing country/region. Further information regarding noise threshold levels for various applications are reported in [19]–[21]. Several EMC standards are offered by the standardization organizations and are used in the industry based on type of applications, and for this reason some of these standards are briefly described as follows:

- FCC Class A and Class B: FCC divided digital electronic equipment into commercial and personal categories which are categorized as classes A and B, respectively. Of course, class B has relatively stricter limits for conducted and radiated EMI because such equipment (computers, calculators etc.) is more likely to be used in close proximity to other electronic devices.

- CISPR 22: Similar to FCC, CISPR 22 provides separate limits for class A and class B equipment. However, CISPR provides more detailed limits/classifications, e.g. further division to frequency ranges, specifying the detection mode such as 'quasi-peak' and 'peak'. Generally, the threshold levels offered by CISPR 22 are within a few dB of the FCC-specified limits (though for CISPR, the units are in  $dB\mu V$  and  $\mu V$  for FCC, but appropriate conversion can be done). Using either of these will not compromise the accuracy of the measurement and EMC endorsement.

- **CISPR 16:** A series of 16 publications covering several appliances and apparatus, which specify the equipment and methods for measuring disturbances and also defining the immunity thresholds for frequencies > 9 kHz up to the GHz range.

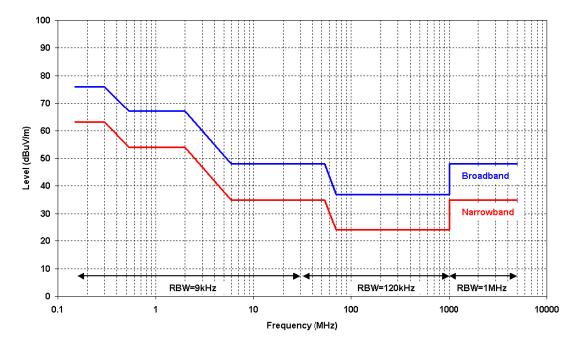

Figure 2.6. Generic limits based on CISPR-25 [22].

- CISPR 25: This has been designed to assure good performance for applications, for instance boats or vehicles, and provides limits for both conducted and radiated emissions. The procedures for measuring disturbances and limits ranging from 150 kHz to 1000 MHz frequency range are defined. An illustration of the threshold limits in shown in Fig. 2.6 [22].

- CISPR 32:2015: This is comparatively relevant and newer EMC standard. This standard covers a frequency range of 9 kHz to 400 GHz and it specifies the noise levels for the multimedia equipment which are powered by an AC or DC power supply up to 600 V (r.m.s or DC respectively) [23].

# 2.2. An Overview of EMI Suppression Techniques

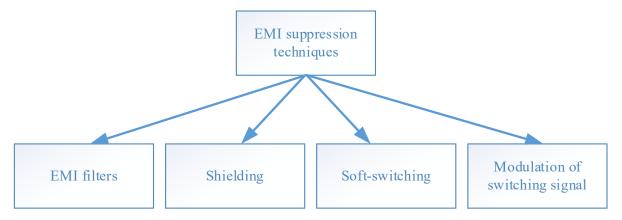

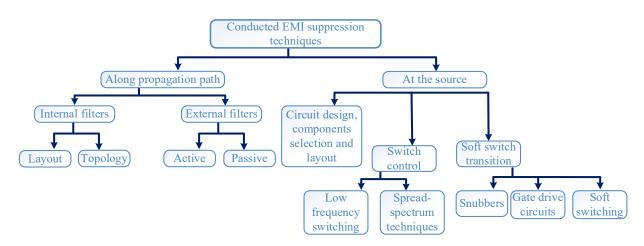

Figure 2.7. A broad classification of EMI suppression techniques.

Figure 2.8. A classification of Conducted EMI suppression techniques.

A number of EMI mitigation techniques have been developed in order to keep EMI noise emissions (conducted and radiated) under the specified limits suggested by the EMC standards. These EMI techniques can be broadly classified into four categories, shown in Fig. 2.7 and explained later. Since this dissertation is focused on conducted EMI mitigation techniques, Fig. 2.8 gives a more detailed classification of conducted EMI mitigation techniques [24].

### 2.2.1. EMI Filters

Traditionally, a combination of passive electronic devices is used to suppress the conducted EMI of a power converter. Principally, an EMI filter is designed as a low-pass filter to impede the high-frequency noise, shorting it to ground [13]. Some insights into the design guidelines for EMI filters are reported in [25]–[27]. Although EMI filters are helpful to attenuate conducted EMI under the standardized thresholds, there are some major drawbacks that cannot be overlooked. The size and volume become a major concern in the case of portable products. As well, the narrow frequency range of filter limits the applicability of this solution. Various active/hybrid EMI filters have also been reported to partially overcome the limitations of passive EMI filters and to further suppress the EMI at lower component count but additional control complexity and limited frequency range [28], [29].

### 2.2.2. Electromagnetic Shielding

Electromagnetic shielding is one of the most effective, but expensive solution which keeps the noise emissions inside an enclosed chamber. Traditionally, metallic materials such as steel, aluminum and copper were shaped to enclose the EMI source but, since these materials are rigid, various flexible materials are used such as metal wires, foams and screens. More recently, particle-filled silicones [28] are used flexibly as an effective EMI shielding material. The conductive shield acts as a barrier to block the electromagnetic fields into "outer space". Nevertheless, EMI shielding is an expensive solution and discouraged especially for portable products. Additionally, various leakages may occur at intakes, outlets and displays, etc., which undermine the performance.

### 2.2.3. Soft Switching

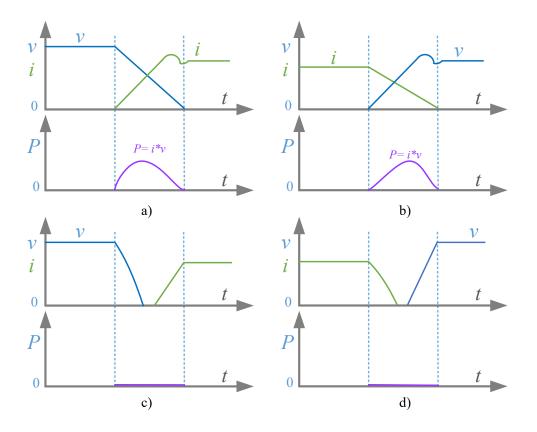

Figure 2.9. The switching process for hard switching (a and b), and soft switching (c and d).

The realization of high switching frequency operation of power converters enables to achieve many advantages such as compactness, easy filtering requirements and better waveforms. On the other hand, it adds to switching power losses and increased EMI due to the steeper edges offered by the power semiconductor devices. Soft-switching [30]–[32] is an indispensable solution for improving efficiency in power converters switched at high frequency. Primarily, zero-voltage and zero-current switching (ZVS and ZCS) are used to minimize the switching losses as shown in Fig. 2.9.

Soft-switched power converters have superior efficiency and EMI performance as compared to their hard-switched operation [33]. As hard-switched converters face higher dv/dt and di/dt, the EMI scenario becomes more crucial for the case of WBG-based hardswitched power converters. Unlike this, soft-switching may require auxiliary circuitry and may add to complicating the control aspect.

### 2.2.4. Modulation of Switching Signal(s)

The modulation of one or more parameters of the switching signal(s) to spread the spectrum of the switching harmonics over a wide range of frequencies has been extensively researched, classified and reported with respect to different applications and implementations [5], [9], [13], [24], [34]–[36]. The foundation of this dissertation is based on achieving EMI suppression through the modulation of switching signals. A detailed relevant discussion is presented in more detail below:

### 2.2.4.1. The Switching Function

In a practical power converter, the required voltage and current are achieved using power switches. Ideally, these power switches have only two states, ON and OFF. This switching sequence/operation can be associated with binary function (q(t)) which is defined as follows:

$$q(t) = \begin{cases} 1, & \text{when the switch is "on",} \\ 0, & \text{when the switch is "off"} \end{cases}$$

(2.4)

q(t) is defined for all values of time, and there are two discrete values associated with it. Therefore, q(t) can also be called the switching function.

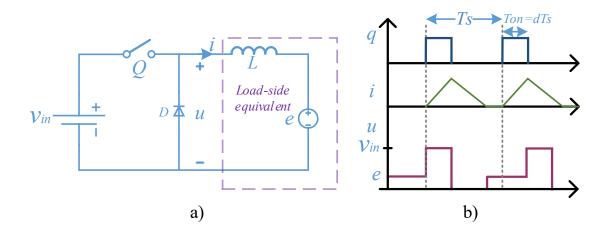

An example of a classic buck converter has been chosen to explore the switching function in more detail. It is noted that the basic operation a buck converter is controlled by the switching function q(t), i.e. when q(t) = 1, the output voltage before the filter (u) is clamped to  $v_{in}$  and when q(t) = 0, 'u' may be equal to 'e' or 'u' depending on the current conduction mode of the filter inductor. Moreover, the duty ratio comes into consideration which also has an impact on the value of the output voltage. The duty ratio may be defined as follows:

$$d = \frac{1}{T} \int_{t_0}^{t_0 + Ts} q(t) dt \tag{2.5}$$

Figure 2.10. A classic buck converter and its associated waveforms.

In case of dc-dc converters, the duty cycle (d) and hence the output voltage is constant in steady-state operation. However, in case of dc-ac inverters, the duty cycle(s) varies periodically to synthesize the alternating output voltage. Furthermore, it can be noted that essentially, the voltage and current transitions are directed by the switching function q(t). Yet in fact, many more parameters are involved in impacting on the way in which the voltage and current transitions (dv/dt and di/dt) occur. Such parameters are numerous and not limited to the conduction mode of the inductor (*CCM or DCM*), the parasities of the PCB, the operating switching frequency, the power converter topology etc.

Figure 2.11. A generic switching signal used to drive the switches of a power converter.

Finally, since q(t) is the fundamental driving force behind di/dt and dv/dt, spectral analysis of a variety of switching functions have been reported to analyze and predict the expected noise emissions of power electronic converters [3], [39]–[43].

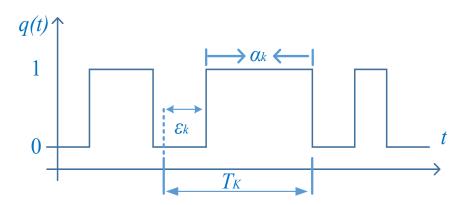

In the following sub-sections, a broad classification of various modulation schemes is given. A discussion is presented so the reader can understand a variety of perspectives which can help achieve EMI reduction in power converters. A general switching signal q(t) for the driving of the power switch(es) in a power converter is shown in Fig. 2.11. Such a signal consists of one pulse per switching cycle, each of which is defined by three parameters:  $\varepsilon_k$  is the delay from the start of the  $k^{th}$  switching cycle to the switch turn-on time,  $\alpha_k$  is the pulse duration in the  $k^{th}$  switching cycle, and  $T_K$  is the total duration of the  $k^{th}$  switching cycle [44]. In terms of these parameters the duty ratio of the  $k^{th}$  switching cycle may be defined as  $D_k = \frac{\alpha_k}{T_k}$ .

| Modulatio                        | Scheme                                          | Sub-<br>classificati -<br>on      | Pulse modulation parameters                 |                                                      |                                                 | Duty<br>ratio<br>- $(\alpha_K/T_K)$ | References               |

|----------------------------------|-------------------------------------------------|-----------------------------------|---------------------------------------------|------------------------------------------------------|-------------------------------------------------|-------------------------------------|--------------------------|

| n Style                          |                                                 |                                   | Switching<br>cycle<br>duration<br>$(T_{K})$ | Pulse width $(\boldsymbol{\alpha}_{\boldsymbol{K}})$ | Pulse position $(\boldsymbol{\varepsilon}_{K})$ | )                                   |                          |

|                                  | PWM                                             |                                   | Fixed                                       | Variable                                             | Fixed                                           | Variable                            | Basic                    |

|                                  | PPM                                             |                                   | Fixed                                       | Fixed                                                | Variab<br>le                                    | Fixed                               | [37]                     |

| Periodic<br>OR                   | DRM +<br>PPM +<br>fixed<br>carrier<br>frequency |                                   | Fixed                                       | Variable                                             | Variab<br>le                                    | Variable                            | Presented<br>work, [36]* |

| Aperiodic<br>(pseudo-<br>random, |                                                 | CFM with<br>fixed duty<br>cycle   | Variable                                    | Synchro-<br>nized                                    | Fixed                                           | Fixed                               | [36], [38]*              |

| chaotic,<br>determin-<br>istic)  | CFM                                             | CFM with<br>varying<br>duty cycle | Variable                                    | Fixed or<br>Variable<br>(not<br>synched)             | Fixed                                           | Variable                            | [34], [36]*              |

| OR<br>Random*                    | CFM +<br>PPM +<br>fixed duty<br>ratio           |                                   | Variable                                    | Variable<br>(synched)                                | Variab<br>le                                    | Fixed<br>(synched)                  | [36]*                    |

|                                  | CFM +<br>PPM +<br>DRM                           |                                   | Variable                                    | Variable                                             | Variab<br>le                                    | Variable                            | [36]*                    |

$\label{eq:PWM} PWM = Pulse \mbox{ Width Modulation, PPM} = Pulse \mbox{ Position Modulation, DRM} = Duty \mbox{ Ratio Modulation, CFM} = Carrier \mbox{ Frequency Modulation}$

\*All the techniques reported in [36] assumed random modulation of the pulse parameters.

Based on variation of the aforementioned parameters, many spread-spectrum pulse modulation techniques may be defined, as summarized in Table 2.1. The technique of spreading of harmonics through the modulation of one or more of the above-mentioned signal parameters is readily applied to single-switch converter topologies. However, there are very few reports concerning their application in converters with multiple switches, as the coordination of multiple switching signals can be difficult, especially if the switching cycle duration varies. The modulation of different parameters of the switching signal q(t) also adds up to the suppression of EMI as well as the complexity of the implementation of such modulation schemes. The modulation styles can be sub-classified into periodic, aperiodic and random. These are explained below:

## 2.2.4.2. Periodic Modulation

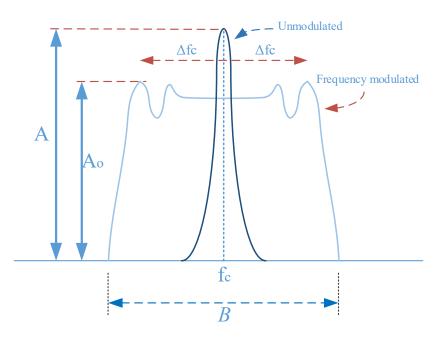

The periodic modulation of one or more parameters of the switching signal q(t) is classified as periodic modulation [45], [46]. A comparison of the frequency-domain spectrum for an unmodulated and a frequency-modulated signal is depicted in Fig. 2.12. Clearly, the spectrum envelope shows a reduction in the peaks, which is the basis of EMI suppression.

Figure 2.12. Spectrum of an unmodulated signal compared with a frequency-modulated sinusoidal signal [45].

It can be noted that the initial energy of the harmonic is spread and thus produces a wider spectrum of frequencies, 'B', with lower amplitudes. While Fig. 2.12 illustrates the spreading phenomenon of a single harmonic, in fact each individual harmonic is spread into a certain frequency band. Mathematically, a frequency-modulated signal may be represented as:

$$F(t) = A.\cos[2\pi f_c t + \theta(t)], \qquad (2.6)$$

where A is the amplitude of the original (unmodulated signal) and  $f_c$  is the unmodulated carrier frequency. Moreover,  $\theta(t)$  is the phase angle defined as

$$\theta(t) = \int_0^t k_w \cdot v_m(\tau) d\tau, \qquad (2.7)$$

where  $v_m(\tau)$  can be regarded as a periodic function of frequency  $f_m$  and  $k_w$  is a factor designated to control the peak-frequency deviation. This gives a further insight into two more parameters, namely the 'modulation index', defined as  $m_f = \frac{\Delta f_c}{f_m}$  and 'rate of modulation' =  $\frac{\Delta f_c}{f_c}$ , where  $\Delta f_c$  is the peak-frequency deviation and  $f_m$  defines the frequency of modulation. Different modulation styles can be produced [47], in this case a periodic frequency modulation is considered. Nevertheless the following conclusions can be made:

1. The energy of each fundamental component is spread into a wide band B', given as:

$$B = 2. f_m \cdot (1 + m_f) = 2. (\Delta f_c + f_m).$$

(2.8)

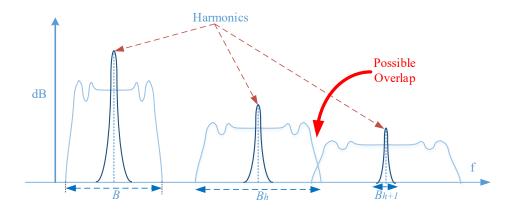

- 2. The bandwidth  $(B_h)$  will eventually increase with an increase in the number of harmonic order (h) as per  $B_h = 2. f_m \cdot (1 + m_f h)$ . In other words, at higher harmonic order, the spread harmonics might overlap and end up increasing the peak envelope. This is pictorially explained in Fig. 2.13.

- 3. Increasing  $\Delta f_c$  leads to an increase in spreading and subsequently suppression of spectral peaks, but on the other hand the fundamental operations (voltage gain, efficiency, current/voltage ripple etc.) of a power converter might be affected. There is always a trade-off in the amount of frequency deviation (leading to harmonic suppression) and the robustness of a power converter.

Figure 2.13. Spreading of harmonics leading to overlap.

Generally, this idea correlates with the frequency-modulation concept in telecommunications, in which two sidebands are generated when a signal is frequency modulated. This is also the reason for denoting the modulation techniques as spreadspectrum techniques which is a core concept in communications [48].

### 2.2.4.3. Aperiodic (Pseudo-random, Chaotic or Deterministic) Modulation

The term "aperiodic" refers to the opposite of periodic. Pseudo-random signals can be referred to as aperiodic signals. Though pseudo-random signals have a mathematical basis, they are not purely random and so cannot be categorized as periodic signals [44]. Another type of aperiodic signals are the "chaotic" signals. These signals carry the properties of a random signal, but since these signals have a mathematical basis, they cannot be categorized as random, so chaotic signals are categorized as aperiodic [9]. Chaotic signals can be implemented by both by analog and digital methods. A chaotic carrier generator or Chua's oscillator is reported in [49], [50] which can be utilized to implement chaotic characteristics in a signal. Nevertheless, chaotic signals are aperiodic in nature and strongly depend on the initial conditions, which makes long-term predictions of chaotic signals impossible, despite their deterministic nature [51]. Considering chaotic modulation from the prospect of the operation of power converters, the control complexities increase due to the lack of any 'prediction' factor. Moreover, numerous parameters are to be considered for the practical implementation of the chaotic-based modulation [52]. Nevertheless, there is a need to come up with an aperiodic modulation methodology which is easy to implement via both analog and digital techniques in addition to owning the deterministic nature.

### 2.2.4.4. Random Modulation

Random modulation can be regarded as the superset of deterministic modulation and there can be numerous ways to implement randomness, i.e. there is no end to the ingenuity of the approaches by which 'randomness' can be achieved [42]. Random modulation refers to the technique of randomly modulating one or more parameters of the switching signal q(t). There are various complications which are related with the usage of random signals to implement random modulation. Firstly, strictly speaking, an actual or purely random signal is difficult to generate and secondly, the parameter design and estimation of various other parameters becomes difficult when using random modulation [13]. For example, the duty ratio of a power converter is usually associated with the output voltage generated. If random modulation is implemented, it may cause complexities in terms of filter design, control loop characteristics and parameter design of the power converter etc.

Finally, an appropriate modulation style would have the properties of being "random" in addition to controllability. In this way there would be more choice of design parameters, implementation of a control loop and filter design in a power converter.

Table 2.2 highlights the similarities and difference between periodic, aperiodic and random signals. The focus of this thesis is on aperiodic pulse width modulation methods.

| Modulation<br>Style | Controllab<br>ility of | Digital/Analo<br>g | Repetition * | Mathematic<br>al | Deterministi<br>c |

|---------------------|------------------------|--------------------|--------------|------------------|-------------------|

|                     | parameter              | Implementatio      |              | expression       | description       |

|                     | s                      | n                  |              |                  | (TD)              |

| Periodic            | Yes                    | Yes                | Yes          | Yes              | Yes               |

| Quasi-periodic      | Yes                    | Yes                | No           | Yes              | Yes               |

| Aperiodic           | Yes                    | Yes                | No           | Yes              | Yes               |

| Chaotic             | Yes                    | Yes                | No           | Yes              | No                |

| Random              | No                     | No                 | No           | Yes (FD only)    | No                |

Table 2.2. Comparison of periodic, aperiodic and random signals

\* Repeat in each switching cycle, FD= Frequency domain, TD= Time domain

# 2.3. Chapter Summary

This chapter provides preliminary information for obtaining insight into EMI produced by power converters. EMI behavior, being a natural phenomenon associated with power converters, can sometimes be difficult to predict accurately due to the number of noise sources (di/dt and dv/dt) present at various localities of a power converter. Active components such as power switches and diodes are the main noise sources which develop the voltage and current transitions. Nevertheless, a number of factors are also associated and cannot be overlooked. These include parasitic ringing voltages and currents, the power converter topology, modulation scheme, PCB design, load power and voltage/current values. Furthermore, not only is fairly accurate model needed to predict accurate ringing behavior, overshoots and rising/falling transients, but also an equivalent electrical circuit of the PCB is also needed. As this thesis is inclined to comment on the impact of modulation schemes to reduce the EMI in power converters, a basic discussion on spectral analysis of the modulated and unmodulated pulses is given in the next chapter. Furthermore, the proposed modulation strategy is applied to a single-switched power converter and the relevant results are discussed.

# Chapter 3

# EMI Suppression for a High-Frequency GaN-based SEPIC Converter

In this chapter, a high-frequency GaN-based SEPIC converter is presented and an aperiodic modulation is applied to analyze the EMI suppression behavior. The methodology to implement the aperiodic modulation is simple and implementable via both analog and digital techniques. The small rise and fall times (in the order of nanoseconds), offered by the GaN switch allow sharper voltage and current transitions (dv/dt and di/dt respectively), so a broadband EMI emissions can be expected. It is interesting to note that the WBG devices such as GaN and SiC on one hand help to attain low weight, high efficiency and better thermal stability. However, on the other hand, these devices have the potential to produce higher EMI levels [4], [44]. Therefore GaN power switches are used in the hardware prototype.

Firstly, the procedure to generate an aperiodic carrier signal is introduced which is further utilized to generate an aperiodically modulated pulse-position switching signal. This PPM signal is used to drive the GaN switch in a SEPIC converter. An introduction to the SEPIC converter is given in relation to the related applications, and the motivation to choose various parameters. Moreover, the design steps for the high-frequency layout of the PCB are presented and include high-frequency design insights. To support the proposed modulation, various experimental results such as voltage gain and efficiency vs load index of the SEPIC converter are presented along with EMI suppression outcomes.

# 3.1 Aperiodic Switching Function

A simple methodology for generating an aperiodic version of the switching signal q(t) is presented in this section. The proposed methodology is believed to be generically adopted for the generation of aperiodic switching signals to realize the essential operation of power converters along with the achievement of EMI reduction. Specifically, in this chapter, the application is focused on a single-switched power converter, and a SEPIC converter is built and tested as a prototype.

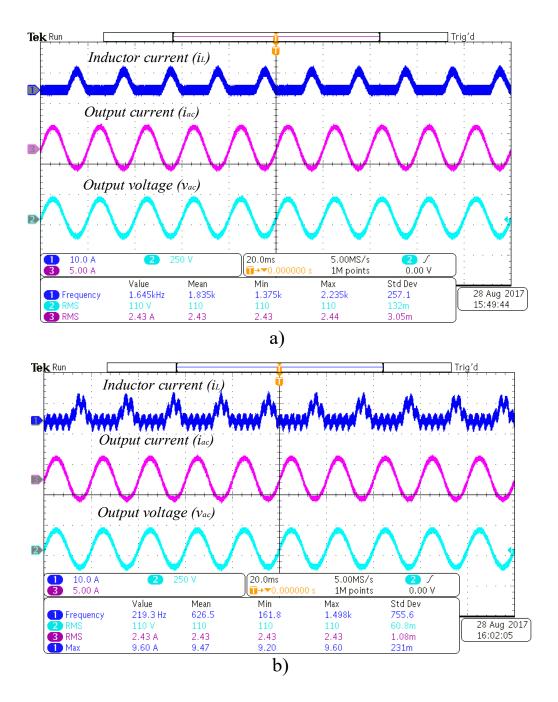

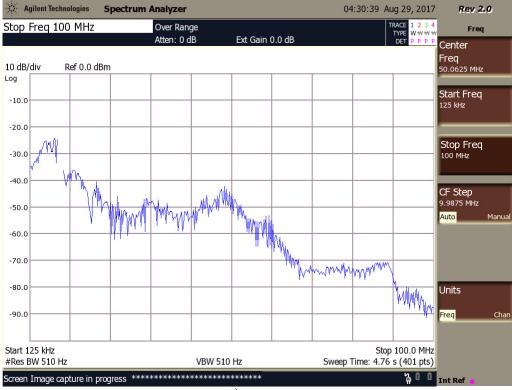

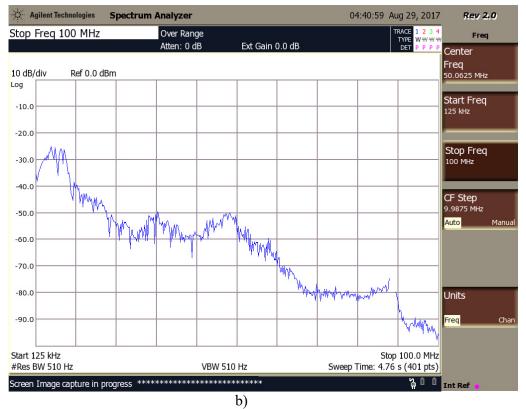

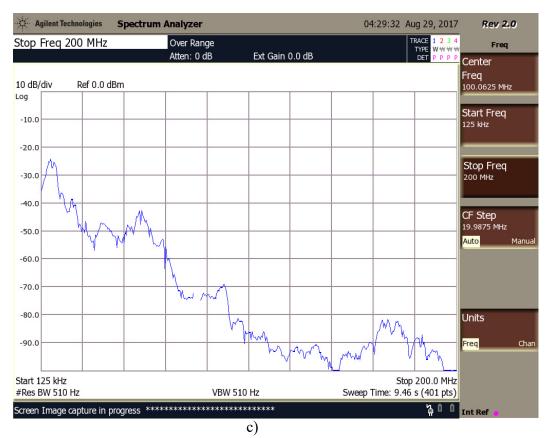

### 3.1.1 Framework for the Implementation of an Aperiodic Switching Signal