# Long-Term Degradation Effects in Power Amplifiers: Analysis, Modelling and Remedies

A thesis for the Master of Research degree

By

Hossein Eslahi

Student ID: 45034532

Supervised By

Dr. Sourabh Khandelwal

Macquarie University Department of Science and Engineering

November 2018

The work presented in this thesis was carried out at the Department of Engineering, Macquarie University, Sydney, Australia, between February and November 2018. This work was principally supervised by Dr. Sourabh Khandelwal. To the best of my knowledge, the materials presented in this thesis, which are considered as thesis's novelty, are original and has not been submitted in whole or part for a degree in any other university or institution other than Macquarie University. The whole information obtained from other publications are all referred in the text and corresponding references are mentioned at the end of thesis.

Hossein Eslahi

# Acknowledgments

I would like to express my deepest and sincerest gratitude to my principal supervisor, Dr. Sourabh Khandelwal, for his excellent support and quality supervision during this research work. I highly acknowledge his invaluable guidance and encouragement for successful and timely completion of this milestone.

I would also like to acknowledge Macquarie University for awarding me the Macquarie University Research Excellence Scholarship (iMQRES).

I will always be grateful for the support and encouragement that I received from my colleagues in our research group. I am thankful to all of them for providing a healthy and friendly work environment. Especially, I cannot forget the help and encouragement I got from Dr. Ali Al-Bahrani and Mr. Dhawal Mahajan.

# **List of Publications**

- H. Eslahi, A. Bahrani, D. Mahajan, S. Khandelwal, "An Analytical and Theoretical Age model to Predict Reliability of Classic Power Amplifiers", *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, 2018 (Submitted).

- H. Eslahi, A. Bahrani, D. Mahajan, S. Khandelwal, "A Tuneable Input-Impedance Matching Approach for Long-term Degradation effects of Power Amplifier", *IEEE International RF and Microwave Conference (RFM)*, Penang, Malaysia, 2018.

- D. Mahajan, A. Bahrani, H. Eslahi, S. Khandelwal, "A Study of Hard Switching Characteristics of GaN-based DC-DC Boost Power Converter using ASM-GaN Compact Model," *Australian Universities Power Engineering Conference (AUPEC)*, Auckland, New-Zealand, 2018.

# Abstract

The wireless communication systems seen with an impressive progress over the last decades. To continue this progress and reach better performance, device dimensions should be down-scaled and this downward trend causes several effects which lead to less reliable systems. The reliability problems are more severe in high frequencies which degrades performance. To address this looming challenge this thesis proposed a new concept of "Reliability-Aware Design". This thesis shows that there exist trade-offs between performance and reliability. If reliability is considered from the beginning of the design phase, intelligent sweet-spots can be identified which deliver both reasonable performance and reliability. Among different RF circuits, power amplifier (PA) is more vulnerable to degradation since it must deliver high power to a load. Therefore, we focus our work on PA's. The aim of this thesis is to describe physical and analytical model for PA reliability which clearly shows the trade-offs with performance in the design phase of PAs.

# Contents

| Acknowledgments                                |

|------------------------------------------------|

| List of Publications                           |

| Abstractiv                                     |

| Contentsv                                      |

| List of Figures                                |

| Chapter 1 1                                    |

| Introduction1                                  |

| 1.1 Background1                                |

| 1.2 Motivation and Objectives                  |

| 1.3 Thesis Structure and Outcomes              |

| Chapter 2                                      |

| Degradation Mechanisms                         |

| 2.1 Chapter Abstract                           |

| 2.2 Introduction                               |

| 2.3 Hot-Carrier Injection                      |

| 2.4 Bias Temperature Instability (BTI)         |

| 2.5 Comparison between BTI and HCI             |

| 2.6 Circuit Degradation due to HCI and BTI10   |

| 2.6.1 LNA Degradation                          |

| 2.6.2 Reliability in Power Amplifier           |

| 2.7 Conclusion                                 |

| Chapter 3                                      |

| Physical Models to Describe Device Degradation |

| 3.1 Chapter Abstract                           |

| 3.2 Introduction                               |

| 3.3 Power Law and Quasi-Static Approach        |

| 3.3.1 HCI-based Models                         |

| 3.3.2 BTI-based model                                            | 21 |

|------------------------------------------------------------------|----|

| 3.3.3 Sub-threshold modelling                                    | 22 |

| 3.4 Conclusion                                                   | 24 |

| Chapter 4                                                        | 27 |

| Analytical Age Model for Power Amplifiers                        | 27 |

| 4.1 Chapter Abstract                                             | 27 |

| 4.2 Introduction                                                 | 27 |

| 4.3 Methodology                                                  | 29 |

| 4.3.1 Lucky-Electron Mode1                                       | 29 |

| 4.3.2 Substrate Current                                          | 29 |

| 4.3.3 Age Equation for Power Amplifier                           |    |

| 4.3.4 Approximations                                             |    |

| 4.4 Validation of Age Model                                      |    |

| 4.4.1 DC Analysis                                                |    |

| 4.4.2 AC Analysis                                                |    |

| 4.5 Reliability versus Conduction Angle: Results and Discussion  |    |

| 4.6 Conclusion                                                   |    |

| Chapter 5                                                        | 41 |

| Modification of Long-Term Degradation Effects of Power Amplifier | 41 |

| 5.1 Chapter Abstract                                             | 41 |

| 5.2 Introduction                                                 | 41 |

| 5.3 Power-Amplifier Design                                       | 42 |

| 5.4 Modified Power-Amplifier Structure                           | 43 |

| 5.4.1 Gain                                                       | 44 |

| 5.4.2 Input Impedance                                            | 44 |

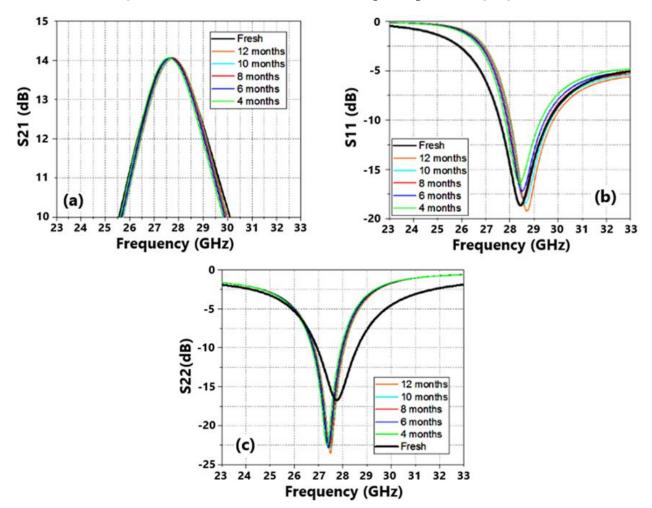

| 5.5 Results and Discussion                                       | 45 |

| 5.6 Conclusion                                                   | 47 |

| Chapter 6                                                        | 49 |

| Conclusion and Future Work                                       | 49 |

| 6.1 Conclusion                                                   | 49 |

| 6.2 Future work                                                  |    |

| References                                                       | 53 |

# **List of Figures**

| 2.1  | a) Drift of main DC parameters and $C_{gd}$ as a function of $V_{gs}$ and time, b) drift of other small-<br>signal parameters vs $V_{gs}$ . The symbols in (b) represent parameters after devices correction<br>[23]                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | small-signal parameter degradation under stress [3]7                                                                                                                                                                                                                                         |

| 2-3  | Simulation result showing that the HCD cannot be recovered after removing stress [7]7                                                                                                                                                                                                        |

| 2.4  | Comparison between DC and AC stress-induced degradation of DC and small-signal parameters [10]                                                                                                                                                                                               |

| 2-5  | a) Degradation of threshold voltage and recovery for NBTI stress (stress voltage $V_{gs} = -4.5 V$ ) at various temperatures [2], b) the threshold voltage degradation after RF NBTI stress as a function of stress time for a 90 nm p-MOSFET with channel length equal to 100 nm [22]       |

| 2.6  | Hot-carrier induced degradation of a) $V_{th}$ and b) $I_{D(sat)}$ , and $V_{th}$ degradation plotted against the frequency for c) a 90 nm p-MOSFET and d) 130 nm p-MOSFET devices after RF NBTI stress as functions of frequency (the dashed lines are meant as a guide to the eye) [22]    |

| 2.7  | HCD/BTI degradation ratio for a) P-FinFET and b) N-FinFET [7]10                                                                                                                                                                                                                              |

| 2.8  | Degradation of a) supply current versus HC stress time, b) drain current versus drain voltage for various stress time, c) transconductance versus gate voltage and d) noise figure of LNA studied in [1]                                                                                     |

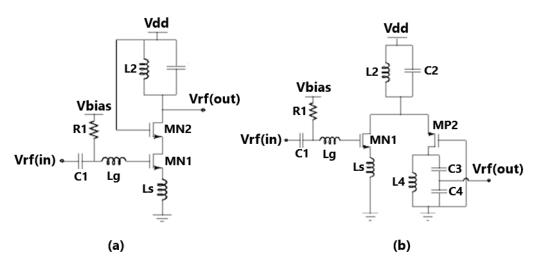

| 2.9  | (a) Cascode and (b) Folded Cascode LNA structures considered in [9]13                                                                                                                                                                                                                        |

| 2.10 | Degradation of NF and gain for folded-cascode over ageing [9]13                                                                                                                                                                                                                              |

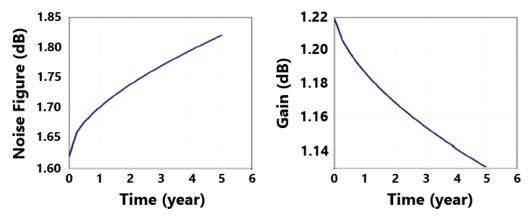

| 2.11 | Cascode class-E PA proposed in [5]14                                                                                                                                                                                                                                                         |

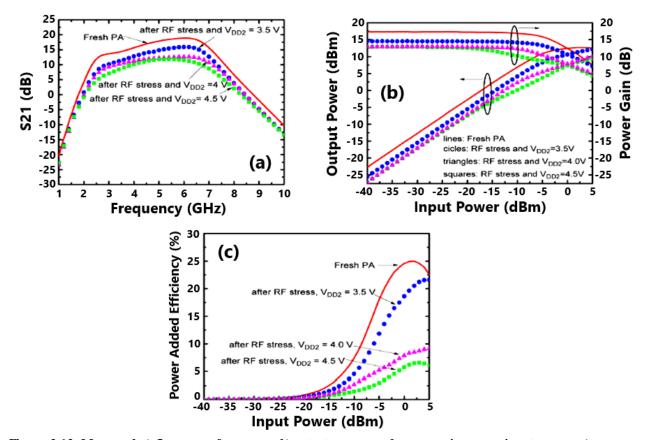

| 2.12 | Measured a) $S_{21}$ versus frequency, b) output power and power gain versus input power, c) power-added efficiency versus input power before and after RF stress for PA presented in Figure 2.11. During the RF stress, $P_{in}$ is at 0 dBm and $V_{dd2}$ was kept at 3.5, 4, or 4.5 V [5] |

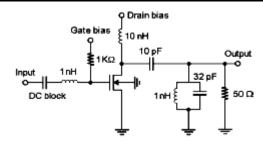

| 2.13 | Class-AB PA mentioned in [10] for reliability studies16                                                                                                                                                                                                                                      |

| 2.14 | a) PAE and b) output power and IM3 degradation due to AC stress for Class-AB power amplifier in Figure 2.13 [10]16                                                                                                                                                                           |

| 3.1  | Comparison of predicted and experimental data for a) pFinFET ( $V_g$ -dependence), b) pFinFET ( $V_d$ -dependence), c) nFinFET ( $V_g$ -dependence), d) nFinFET ( $V_d$ -dependence) [7]                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2  | a) Illustration of GIDL and DIBL leakage currents in Sub-Threshold region, b) TTF (10% degradation of $I_{d,sat}$ ) for different $V_g - V_d$ configurations in the sub-threshold area [4] 23           |

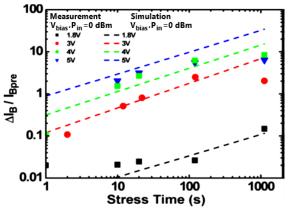

| 3.3  | Comparison of predicted and measured RF stress-induced $\Delta I_B$ , scaled by predicted base current $I_{B,pre}$ [40]24                                                                               |

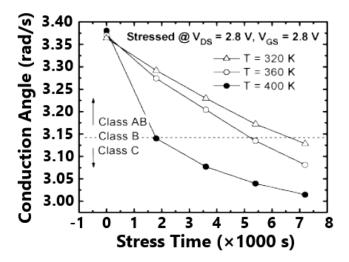

| 4.1  | Variation of conduction angle as a function of stress time [6]                                                                                                                                          |

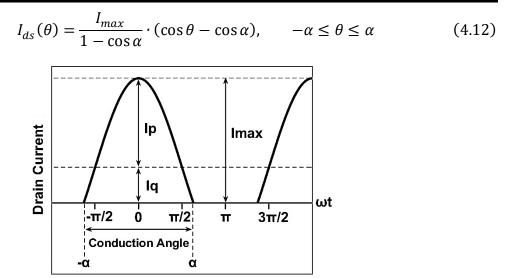

| 4.2  | Illustration of DC and AC parts of PA's drain current based on conduction angle                                                                                                                         |

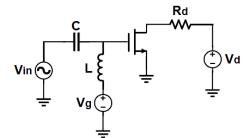

| 4.3  | Proposed test bench to validate age model                                                                                                                                                               |

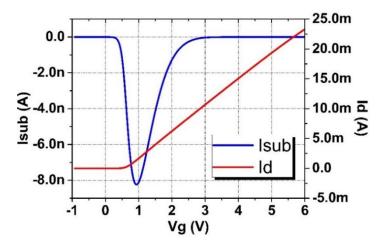

| 4.4  | $I_{sub} - V_g$ and $I_d - V_g$ characteristics of transistor used in Figure 4.3                                                                                                                        |

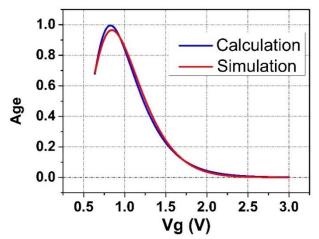

| 4-5  | Calculation and simulation age results versus gate voltage                                                                                                                                              |

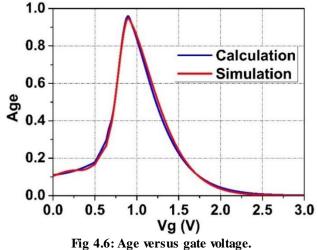

| 4.6  | Age versus gate voltage                                                                                                                                                                                 |

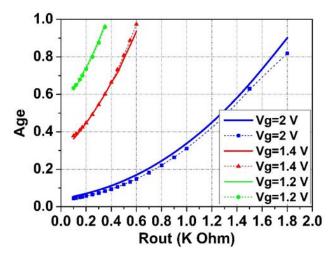

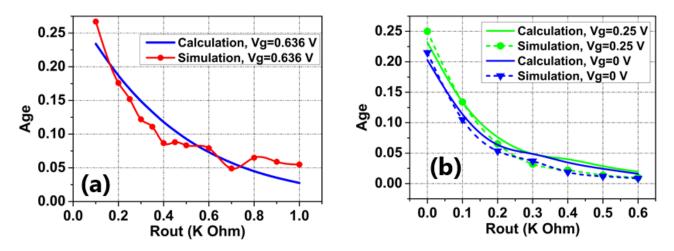

| 4.7  | Simulation and calculation age results versus output resistor for three class-A modes extracted under AC and DC stresses (solid and dashed lines show calculation and simulation results, respectively) |

| 4.8  | Simulation and calculation age results versus output resistor for a) class-B and b) two class-C modes extracted under AC and DC stresses                                                                |

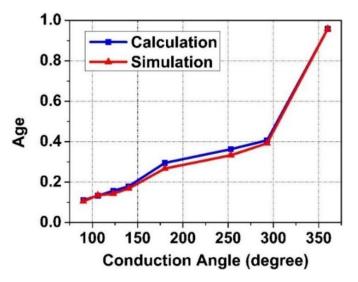

| 4.9  | Age versus conduction angle from 90° to 360°37                                                                                                                                                          |

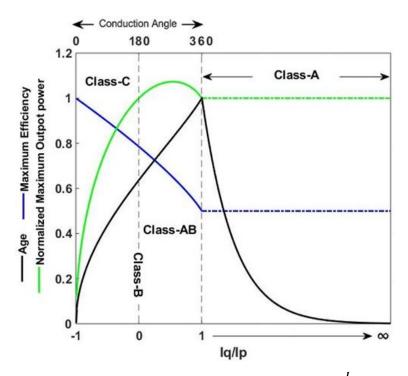

| 4.10 | Trade-off between maximum efficiency, normalized maximum output power, and age as functions of conduction angle                                                                                         |

| 4.11 | variation of three PA design criteria versus $\frac{l_q}{l_p}$ ratio                                                                                                                                    |

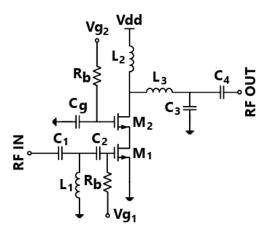

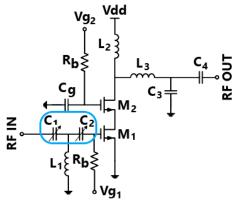

| 5.1  | The n-MOS power amplifier proposed in [46] and used in in this thesis for reliability studies                                                                                                           |

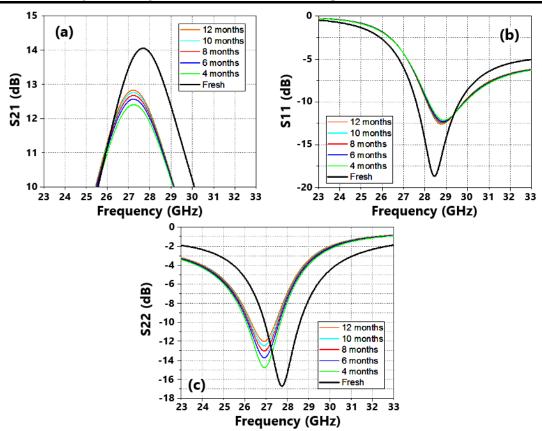

| 5.2  | Simulation results for the fresh and degraded a) $S_{21}$ , b) $S_{11}$ , and c) $S_{22}$ for 4, 6, 8, 10, and 12 months of ageing time                                                                 |

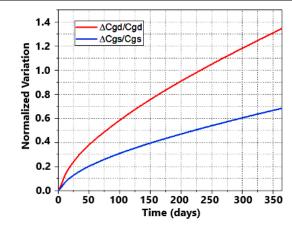

| 5.3  | Normalized variation $C_{gd}$ and $C_{gs}$ for 45 nm RFSOI model considered in this research44                                                                                                          |

| 5.4  | The proposed degradation-immune PA45                                                                                                                                                                    |

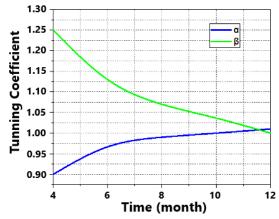

| 5.5  | The variation of the normalized $C_1$ and $C_2$ with the ageing time                                                                                                                                    |

| 5.6  | Simulation results for the degradation of a) $S_{21}$ , b) $S_{11}$ , and c) $S_{22}$ after proper tuning of the varactors used in the input matching network                                           |

viii

# Chapter 1

# Introduction

#### 1.1 Background

Wireless communication systems have made impressive progress over the last decades. Hardly a month goes without a new report about new applications of integrated circuits (ICs) published in the media. To continue this ever-growing progress, reach better performance (like greater speed, better frequency response), and integrate all the different parts of a transceiver into a single chip, down-scaling of device dimensions is inevitable as predicted by Moore's law. However, this downward trend in devices dimension causes them to face several challenges such as short-channel effects, higher electric field on a transistor's channel, trapping charges into gate insulator, breakdown, etc. The overall performance, as a consequence, will degrade. So, device reliability has become a complex problem during the design and modelling process [1-4].

It is anticipated that radio-frequency (RF) circuit performance also degrades after device degradation due to scaling, stress and ageing. To further clarify this, note that circuit performance (noise figure, linearity, gain, matching, etc.) are all functions of device DC parameters such as the threshold voltage  $(V_{th})$ , mobility  $(\mu_0)$ , transconductance  $(g_m)$ , and small-signal characteristics like gate-source  $(C_{gs})$  and gate-drain  $(C_{gd})$  capacitors. Therefore, device degradation imposes degradation of circuit performance. This unwanted degradation will be more catastrophic when the devices work at radio frequencies where they operate under both DC and AC stresses [1-3].

The most important physical mechanisms responsible for device degradation are Hot-Carrier Injection (HCI) due to a high lateral field in short-channel devices, Time-Dependent Dielectric Breakdown (DB) favoured by a high vertical field in thin oxide layers, and Bias Temperature Instability (BTI). The former is becoming a first-order concern for RF applications, which can also accelerate breakdown phenomena [3, 5-10].

Among RF circuits, power amplifiers (PAs) are more vulnerable to hot-electron effects. This is because, due to the necessity of delivering high power to a load, the drain voltage in PAs can experience unusual peak values, even more than twice the supply voltage [5-7, 11]. Degradation of a power amplifier, being a main part of a transceiver chain, can also affect the overall performance of a transceiver. However, none of the research, published in the literature, has compared the classic classes of PA in terms of reliability. Those studies are restricted to three main fields, namely (i) DC/RF stress effects on device and circuit reliability, (ii) high-temperatures effects, and (iii) a circuit modification approach to mitigate long-term degradation in RF devices and circuits [6, 12-20]. Therefore, analytically modelling reliability in power amplifiers could be an innovative research topic. In addition, if reliability is considered at early steps of a design phase, intelligent sweet-spots can be identified, reasonable performance and reliability can be delivered, and looming challenges can be addressed.

Two main steps in reliability evaluation in RF circuits are to analyse degradation mechanisms and then to find a precise age model to predict the degradation of devices. It is valuable to solve these models and analytically investigate circuit reliability without repeating time-consuming simulations by the RelXpert simulator. All reliability models, therefore, should be solved using numerical solutions, as is performed in the RelXpert simulator. The aim of this thesis is to describe a physical and analytical age model for PA degradation which clearly shows the trade-offs with PA performance. This predictive model is a function of conduction angle and, therefore, it is valid for the different classes of PAs. Based on the results shown in this thesis, it is claimed that reliability must be considered as one of the key design parameters and, therefore, a new concept of "Reliability-Aware Design" is formed.

#### **1.2 Motivation and Objectives**

The automotive industry has recently become one of the main areas for making use of RF integrated circuits (RFICs). Almost all electrical systems in smart cars, such as engine controllers, air bags and assistance systems utilise ICs. In addition, safety and convenience are two important issues that should be met in this new generation of cars so automotive electronics requires a high level of reliability. Air bags, for instance, are critical for occupant safety, making their reliability vital. This problem becomes more critical when an inordinate number of cars are fabricated annually and a simple failure in device operation, induced by ageing and/or stress, may cause

heavy economic-loss. Clearly, considering device and circuit reliability during the design process can enhance the quality of products and decrease the economic losses. Besides, since there is little research in the field of circuit reliability modelling, it seems clear that much further research is needed on this topic.

#### **1.3 Thesis Structure and Outcomes**

This dissertation is divided into six chapters, the first of which is this introductory chapter, and it will be terminated by a conclusion of the whole thesis in Chapter 6. The other chapters forming the main body of the thesis are organised as follows.

A brief overview of the most well-known device degradation mechanisms (HCI, BTI, TDDB), their origin, and their effects on device performance will be presented in Chapter 2.

In Chapter 3 some models developed in the literature to predict device degradation due to static (DC) and dynamic (AC/RF) stresses are presented. Using static models leads to wrong results, as reliability is supposed to be studied under time-varying bias conditions. Therefore, a "Quasi-Static" approach is introduced as a good approximation to create AC models based on DC counterparts. However, at the end of this chapter, one can conclude that none of the current models are applicable to predict reliability in PAs as a function of conduction angle, since they are developed at the device level.

Chapter 4 addresses this problem by describing a new degradation model which can precisely forecast PA ageing. This model is a strong function of conduction angle and can be applied to all classes of power amplifiers. A new trade-off between reliability and PA performance is introduced which helps designers to meet the needs of suitable efficiency, high output power, and reliability at the same time.

The question may come into mind whether there exist solutions to mitigate long-term degradation after the design steps. A circuit-design approach is, therefore, introduced in Chapter 5 based on variable capacitors. This approach, despite its simplicity, can be a good idea to compensate for transistor ageing and enhance circuit performance even after design process.

Three publications which have been extracted from this work are:

H. Eslahi, A. Bahrani, D. Mahajan, S. Khandelwal, "An Analytical and Theoretical Age model to Predict Reliability of Classic Power Amplifiers", *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, 2018 (Submitted).

- H. Eslahi, A. Bahrani, D. Mahajan, S. Khandelwal, "A Tuneable Input-Impedance Matching Approach for Long-term Degradation effects of Power Amplifier", *IEEE International RF and Microwave Conference (RFM)*, Penang, Malaysia, 2018.

- D. Mahajan, A. Bahrani, H. Eslahi, S. Khandelwal, "A Study of Hard Switching Characteristics of GaN-based DC-DC Boost Power Converter using ASM-GaN Compact Model," *Australian Universities Power Engineering Conference (AUPEC)*, Auckland, New Zealand, 2018.

# Chapter 2

# **Degradation Mechanisms**

#### 2.1 Chapter Abstract

Recognition of the physical mechanisms responsible for device degradation is important before reliability modelling. This chapter, therefore, represents a brief overview of the main degradation mechanisms as the first step of a reliability study. Then, the correlation between circuit degradation and device degradation will be explained.

#### 2.2 Introduction

In addition to Hot-Carrier Injection (HCI), Time-Dependent Dielectric Breakdown (TDDB), and Bias Temperature Instability (BTI) which are considered as prominent mechanisms causing device degradation [3, 7-10], new materials, higher temperatures, high currents, electro-migration phenomena, and sub-threshold leakage currents are other mechanisms can lead to reliability issues [4, 9, 11, 21]. However, these factors do not impose as catastrophic failures as the first three mechanisms on device operation. In addition, it is repeated in several references that *TDDB may not have a significant impact on RF circuits in nominal operating conditions* [6, 9, 22]. Therefore, only HCI and BTI degradation mechanisms are evaluated in detail in this chapter.

#### 2.3 Hot-Carrier Injection

Hot-Carrier Injection (HCI) is a classic problem for all technologies like CMOS transistors, and is a consequence of both DC (static) and AC/RF (dynamic) stress conditions. The aggressive

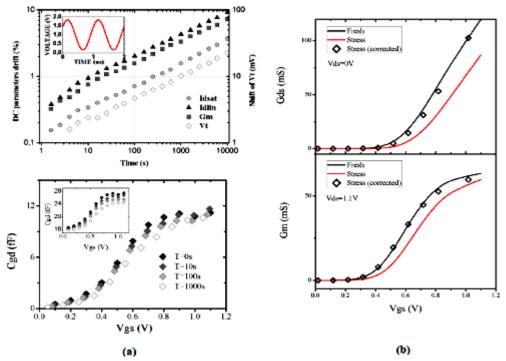

down-scaling of the channel length of CMOS devices results in a higher electric field being experienced by the electrons in the channel. Then, these electrons become highly energetic and some of these energetic electrons (called hot electrons) can reach and get trapped within the oxide layer, raising the threshold voltage  $(V_{th})$  of these devices and reducing the effective mobility, yielding a decrease in the drain current  $(I_d)$  and transconductance  $(g_m)$ . The increase in  $V_{th}$  and degradation of  $g_m$  and  $I_d$  can also degrade other DC characteristics, like linear  $(I_d(lin))$  and saturated  $(I_d(sat))$  currents ,and small-signal elements such as gate-source and gate-drain capacitances ( $C_{gs}$  and  $C_{gd}$ ) [3, 5, 6, 8, 9, 23]. Some examples of these degradations are shown in Figures 2.1 and 2.2 [3, 23].

Figure 2.1: a) Drift of main DC parameters and  $C_{gd}$  as a function of  $V_{gs}$  and time after applying supply voltage  $V_{ds} = 1V$  and bias voltage  $V_{gs} = 1.8 V$  to a nMOSFET with gate length L = 40 nm, total gate width W = 57.6 um and number of fingers N = 10. b) drift of other small-signal parameters vs  $V_{gs}$ . The symbols in (b) represent parameters after devices correction [23].

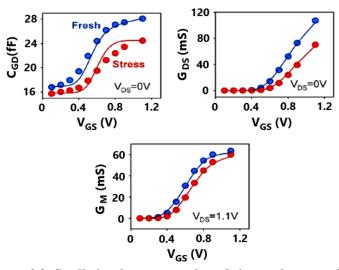

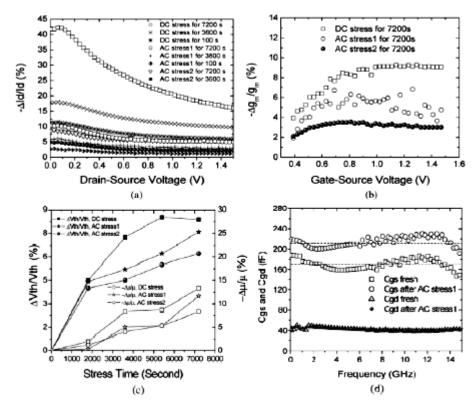

From Figure 2.3 representing simulation results for a nFinFET, hot-carrier degradation (HCD) is an irreversible phenomenon even after removing stress [7]. In [10] the results for the degradation of the DC parameters,  $C_{gd}$ , and  $C_{gs}$  as a function of stress time and frequency, which are obtained after applying DC and AC stress to a BSIM3V3 model, are represented (see Figure 2.4). These data explain that the drain-current degradation due to DC stress is worse than that due to AC (dynamic) stress, but all the drain currents shift downward after stress. A summary of the parameter shifts in a BSIM3v3 after DC and AC stresses is also expressed in Table 2.1.

Figure 2.2: Small-signal parameter degradation under stress [3].

Figure 2.3: Simulation result showing that the HCD cannot be recovered after removing stress [7].

Figure 2.4: Comparison between DC and AC stress-induced degradation of DC and small-signal parameters [10].

| Parameter         | DC st      | DC stress (%) |            | ess (%)     |

|-------------------|------------|---------------|------------|-------------|

| Shift             | For 1 hour | For 2 hours   | For 1 hour | For 2 hours |

| $\Delta C_{gs}$   | 23         | 32            | 14.31      | 26.47       |

| $\Delta C_{db}$   | 12.38      | 26            | 12.6       | 17.90       |

| $-\Delta R_{db}$  | 15.86      | 27            | 13.8       | 20.00       |

| $-\Delta R_{dsb}$ | 14.12      | 25.68         | 15         | 20.00       |

| $\Delta R_d$      | 11.98      | 16.78         | 8.34       | 12.50       |

| $\Delta R_g$      | 12.17      | 18.56         | 9.36       | 14.08       |

| $-\Delta R_s$     | 42.86      | 56.00         | 36         | 50.00       |

| $\Delta V_{th}$   | 7.98       | 8.52          | 5.50       | 8.06        |

| $-\Delta\mu$      | 8.00       | 12.28         | 5.00       | 11.8        |

| $\Delta NFactor$  | 4.62       | 5.58          | 2.89       | 3.08        |

| $-\Delta K1$      | 0.83       | 1.67          | -0.76      | 1.26        |

| $-\Delta U_a$     | 12.21      | 19.92         | 3.61       | 5.27        |

| $\Delta V_{off}$  | 4.31       | 5.73          | 1.68       | 2.29        |

Table 2.1: Parameter degradation for BSIM3V3 model after DC and AC stress [10].

#### 2.4 Bias Temperature Instability (BTI)

A transistor shows changes in its characteristics initiated by temperature and bias-voltage variation over the long term. This effect is termed bias temperature instability (BTI) and can gradually degrade  $V_{th}$  [2, 9, 22, 24]. The effectiveness of BTI is different for P- and N-type FETs and it is proved that at Nano-scale, NBTI (N-type BTI) in PMOSFETs is more critical than PBTI (P-type BTI) for NMOSFETs [2, 22]. Although BTI reliability in both cases (NBTI and PBTI) has been well understood in planar devices, these phenomena can affect non-planar FETs in some cases like geometry, structure and technology. Therefore, they must be investigated in detail but there is little research about, for example, NBTI effects in PMOSFETs [22].

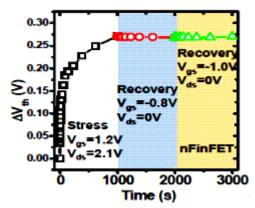

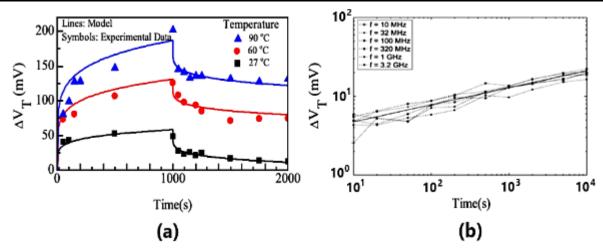

It is proved that the BTI is a recoverable degradation-mechanism [2, 7, 9]. As an example, Figure 2.5 (a) shows such behaviour for threshold voltage variation after NBTI degradation. It is also seen from this figure that BTI is temperature-dependent [2]. In the next chapter, relevant age models will be presented which quantify this recoverable behaviour. Finally, several simulations were performed in [22] to evaluate the time dependency of NBTI degradation under RF and DC stress. The results are shown in Figure 2.5 (b) for RF stress and the same results can be obtained after DC stress. It is clear from this figure that there is no significant difference in the time exponent between DC and RF NBTI degradations.

Figure 2.5: a) Degradation of threshold voltage and recovery for NBTI stress (stress voltage  $V_{gs} = -4.5 V$ ) at various temperatures [2], b) the threshold voltage degradation after RF NBTI stress as a function of stress time for a 90 nm p-MOSFET with channel length equal to 100 nm [22].

#### 2.5 Comparison between BTI and HCI

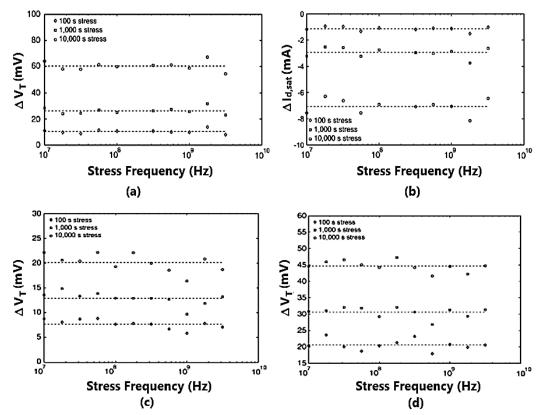

Similarly to hot-carrier degradation, NBTI induced parameter shift follows a power law (which will be discussed in the next chapter) and both get worse with rising temperature. Another similarity between BTI and HCI is their frequency dependency. Some researchers believe that no frequency dependence should be found based on the reaction–diffusion model [22, 25]. The results presented in Figure 2.6, obtained under HCI and NBTI stresses, clarify this concept. As shown in this figure, no frequency dependence exists in the amount of  $V_{th}$  and saturation current,  $I_{D(sat)}$  degradation. However, there are some controversial claims in the other references. For instance, it is argued in [26, 27] that the recovery mechanism can completely or partly be attributed to the detrapping of holes in deep oxide traps and, under this assumption, some frequency dependence may be expected.

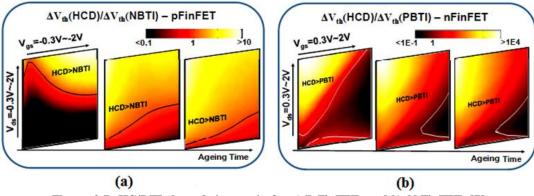

One of the differences between HCI and BTI is their behaviour during and after stress. It was shown that BTI, unlike HCI, exhibits a peculiar property of recovery when stress is removed, and device parameters can recover towards their initial unstressed value [2, 9, 22]. In terms of degradation rate, Figure 2.7 (a) shows a map displaying the HCI/NBTI degradation ratio in a P-FinFET over the whole  $V_{gs}/V_{ds}$  region. The results show that HC degradation will become larger and more catastrophic than NBTI when  $V_{ds}$  is increased. Moreover, HCI will gradually overtake NBTI as time increases, due to different degradation rates. The same results can be obtained for an N-FinFET (Figure 2.7 (b)), except that PBTI degradation is actually very small in FinFET technology [7]. Eventually, a comparison between the effects of HCI and BTI stresses on the main parameters of an InGaAs n-MOSFET is presented in Table 2.2 [24].

Figure 2.6: Hot-carrier induced degradation of a)  $V_{th}$  and b)  $I_{D(sat)}$ , and  $V_{th}$  degradation plotted against frequency for c) a 90 nm p-MOSFET and d) 130 nm p-MOSFET devices after RF NBTI stress as functions of frequency (the dashed lines are meant as a guide to the eye) [22].

Figure 2.7: HC/BTI degradation ratio for a) P-FinFET and b) N-FinFET [7].

#### 2.6 Circuit Degradation due to HCI and BTI

All the building blocks in a receiver chain (LNA, power amplifier, Mixer, Oscillator, etc.) are designed with their own figure of merit. For example, gain, linearity, input and output return loss, overall noise figure (NF), minimum noise figure ( $NF_{min}$ ), and power consumption measure LNA performance while power-added efficiency (PAE), drain efficiency ( $\eta$ ), ACPR, NPR, maximum power delivered to load, and linearity are considered as Power Amplifier (PA) performance measures [16, 28, 29, 30]. These figures of merit are defined by device DC and small-signal characteristics. To put it another way, the overall gain in a cascode topology is a product of the

effective transconductance of the first stage and the output impedance, while both are calculated by small-signal  $(g_m, g_{ds}, C_{gs}, C_{gd}, ...)$  elements. The degradation of DC parameters like the threshold voltage and mobility also change the overall drain current and, consequently, the effective transconductance. Therefore, there is a strong correlation between device and circuit degradation. In the following sub-sections this correlation is discussed more clearly in LNAs and PAs.

| Unstressed                                                                                     | $V_{th}$ [V] *                       | $DC - g_{max}$<br>[mS/µm] *          | $max f_t  [GHz] *$ |  |  |  |

|------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|--------------------|--|--|--|

| $L_{gate} = 50 nm$                                                                             | $-0.04\pm0.14$                       | $0.98 \pm 0.14$                      | $163 \pm 40$       |  |  |  |

| $L_{gate} = 100 \ nm$                                                                          | $0.05\pm0.04$                        | $0.95 \pm 0.03$                      | 156 ± 21           |  |  |  |

| $L_{gate} = 2000 \ nm$                                                                         | $0.12\pm0.01$                        | $0.79\pm0.01$                        | $100 \pm 11$       |  |  |  |

| <b>PBTI</b> $V_G = V_{stress}, V$                                                              | $V_D = V_S = 0 \text{ V}, 150$       | 00 s, 25 °C, <i>L<sub>gate</sub></i> | = 50 <i>nm</i>     |  |  |  |

| V <sub>stress</sub> [V]                                                                        | $\Delta V_{th}$ [V]                  | $\Delta g_{max}$<br>[mS/µm]          | $\Delta f_t$ [GHz] |  |  |  |

| 2                                                                                              | +70                                  | -0.08                                | +2                 |  |  |  |

| 3                                                                                              | +84                                  | -0.19                                | **0.r.             |  |  |  |

| <b>NBTI</b> $V_G = V_{stress}, V$                                                              | $V_D = V_S = 0 \text{ V}, 150$       | 00 s, 25 °C, <i>L<sub>gate</sub></i> | = 50 <i>nm</i>     |  |  |  |

| V <sub>stress</sub> [V]                                                                        | $\Delta V_{th}$ [V]                  | $\Delta g_{max}$<br>[mS/µm]          | $\Delta f_t$ [GHz] |  |  |  |

| -2.5                                                                                           | -306                                 | -0.15                                | +10                |  |  |  |

| -3                                                                                             | -403                                 | -0.19                                | +6                 |  |  |  |

| <b>NBTI</b> $V_G = V_{stress}, V$                                                              | $V_D = V_S = 0 \text{ V}, 150$       | 00 s, 25 °C, <i>L<sub>gate</sub></i> | = 200 <i>nm</i>    |  |  |  |

| V <sub>stress</sub> [V]                                                                        | $\Delta V_{\rm th} \left[ V \right]$ | Δg <sub>max</sub><br>[mS/µm]         | $\Delta f_t [GHz]$ |  |  |  |

| -3                                                                                             | -273                                 | -0.13                                | -1                 |  |  |  |

| <b>HCI</b> $V_G = V_{stress}$ , $V_D = 1$ V, $V_S = 0$ V, 1500 s, 25 °C, $L_{gate} = 100 \ nm$ |                                      |                                      |                    |  |  |  |

| V <sub>stress</sub> [V]                                                                        | $\Delta V_{th}$ [V]                  | $\Delta g_{max}$<br>[mS/µm]          | $\Delta f_t$ [GHz] |  |  |  |

| 1                                                                                              | +209                                 | +0.09                                | +16                |  |  |  |

Table 2.2: Key-parameter shift after HCI and BTI stresses [24].

\* Maximun measured  $f_t$  and extrinsic DC- $g_{max}$  at  $V_D = 0.525$  V are given \*\* Maximun  $f_t$  outside S-parameter measurement range (0.1 V to 0.8 V)

#### 2.6.1 LNA Degradation

The degradation of LNA characteristics can be expressed as functions of the device characteristics. For example, an analytical equation for the minimum noise figure and its sensitivity to HCI-induced threshold voltage and mobility shift was presented in [1]. This equation, developed to show the hot-carrier injection stress effects on a three-stage low-noise amplifier (65 nm silicon-based technology), is written as:

$$\frac{\Delta NF_{min}}{\Delta NF_{min} - 1} = \frac{\Delta V_{th}}{V_{th}} \cdot \frac{V_{th}}{2(V_{GS} - V_{th}) + 3b(V_{GS} - V_{th})^2 + b^2(V_{GS} - V_{th})^3} - \frac{1}{2}\frac{\Delta\mu_n}{\mu_n}$$

(2.1)

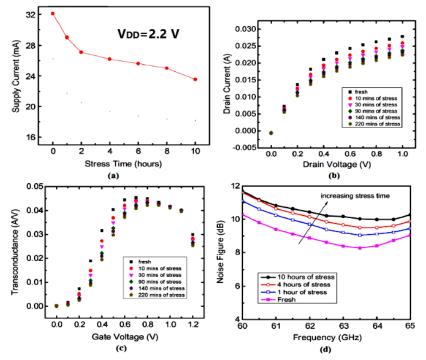

where *b* accounts for the mobility degradation due to the vertical electrical field from the gate. From (2.1), when the threshold voltage increases ( $\Delta V_{th} > 0$ ) and/or electron mobility decreases ( $\Delta \mu_n < 0$ ), the normalised minimum noise figure will increase. The degradation of supply current, drain current, transconductance, and input matching network (all caused by hot carriers) and their catastrophic effects on  $NF_{min}$  are shown in Figure 2.8.

Figure 2.8: Degradation of a) supply current versus HC stress-time, b) drain current versus drain voltage for various stress-times, c) transconductance versus gate voltage and d) noise figure of LNA studied in [1].

In [9] the impacts of transistor ageing on CMOS technology are evaluated by comparing the extracted results for an RF single-ended cascode LNA and an LC folded-cascode LNA (Figure 2.9). The degradation of the overall gain and noise figure are represented by equations (2.2) and (2.3) based on transconductance and gate-source capacitor, indicating that the NF and overall gain will degrade after  $g_m$  decreases and  $C_{gs}$  increases due to both BTI and HCI mechanisms. In (2.2), A is a function of is the parasitic resistance of the inductor at the input ( $R_l$ ), the internal resistance of the signal source ( $R_s$ ), and the gate resistance of the input. Figure 2.10 shows the simulation results for the gain and NF degradations caused by ageing in a folded-cascode LNA. Both degradations are significantly worse than those for the cascode LNA (see Table 2.3) because the supply voltage is shared by two transistors in cascode LNA. Consequently, the drain-to-source voltage stress affecting the input transistor is reduced [9]. A similar conclusion is reported in [5].

$$\frac{\Delta NF_{LNA}|_{ageing}}{NF_{LNA} - A} \approx -\frac{\Delta g_m}{g_m} + \frac{\Delta C_{gs}}{C_{gs}}$$

(2.2)

Degradation Mechanisms

$$\frac{\Delta G}{G}\Big|_{ageing} = \frac{\Delta g_m}{g_m} - \frac{\Delta C_{gs}}{C_{gs}}$$

(2.3)

#### 2.6.2 Reliability in Power Amplifier

In order to analyse and predict reliability in PAs, accurate modelling and testing are required, since the reliability of a power amplifier is crucial for a transceiver and its degradation can directly affect the whole receiver performance [11]. In some articles, such as [5], the effect of the oxide thickness of a cascode transistor on alleviating oxide stress in PAs is studied. It was shown that there is a trade-off between increase in thickness and output voltage swing. However, these studies have been done based on gate-oxide stress not on HC stress.

Figure 2.9: (a) Cascode and (b) Folded-Cascode LNA structures considered in [9].

Figure 2.10: Degradation of NF and gain for folded-cascode over ageing [9].

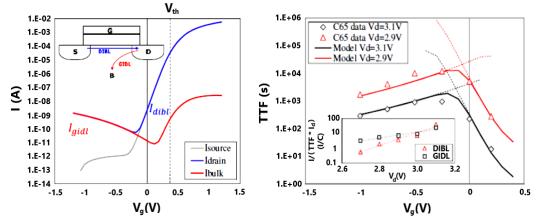

A cascode class-E power amplifier (PA) operating at 5.2 GHz has been designed in [5] using Advanced Design System (ADS) simulation to evaluate the hot-electron effect on class-E PA degradation. Here, again, RF circuit performance such as the output power and power-added efficiency before and after DC (increase in  $V_{dd}$ ) and RF stresses have been experimentally investigated. The proposed class-E PA is shown in Figure 2.11.

| -              | ogy and<br>rmance | Nominal<br>Value | Average<br>Degradation (%) |

|----------------|-------------------|------------------|----------------------------|

| Cascode        | NF (dB)           | 1.1925           | +0.6                       |

| LNA            | $NF_{min}$ (dB)   | 1.0190           | +0.7                       |

|                | Gain (dB)         | 11.905           | -1                         |

| Folded-        | NF (dB)           | 1.6198           | +13                        |

| Cascode<br>LNA | $NF_{min}$ (dB)   | 1.0424           | +13.7                      |

|                | Gain (dB)         | 12.453           | -8.6                       |

Table 2.3: Comparison between two various LNA topologies due to Degradation [9].

Figure 2.11: Cascode class-EPA proposed in [5].

Figure 2.12: Measured a)  $S_{21}$  versus frequency, b) output power and power gain versus input power, c) poweradded efficiency versus input power before and after RF stress for PA presented in Figure 2.11. During the RF stress,  $P_{in}$  is at 0 dBm and  $V_{dd2}$  was kept at 3.5, 4, or 4.5 V [5].

It can easily be seen that the cascode transistor  $(M_3)$  tolerates more voltage stress at its drain than the main transistor  $(M_2)$ . On the other hand, at high input power, the cascode transistor could suffer from the hot-electron effect when gate-source and drain-source voltages are high during switching transients. Figure 2.12 (a) shows the measured small-signal gain,  $S_{21}$ , versus frequency after applying stress. From this figure, it is proved that the larger the stress is at high  $V_{dd2}$ , the more the  $S_{21}$  degrades over a wide range of frequencies. What is more, the measured output power, power gain and power-added efficiency before and after the RF stress are also plotted in Figure 2.12 (b) and (c). These curves prove that the PA performance decreases after RF stress, particularly when the  $V_{dd2}$  stress level is increased, and this is attributed to the hot-electron effect on the output transistor. Table 2.4 summarises the small-signal gain  $S_{21}$  at 5.2 GHz, output power at the input power of 0 dBm, power gain at the input power of -20 dBm, and maximum power-added efficiency before and after RF stress for the Class-E PA presented in Figure 2-11. Their normalized parameter shifts  $(\Delta S_{21}/S_{21}, \Delta P_{out}/P_{out}, \Delta (P_{out}/P_{in})/(P_{out}/P_{in}), \Delta \eta_{added}/\eta_{added} \times 100\%)$  are also presented, indicating considerable degradation due to hot-electrons.

| RF parameter     | $S_{21}$ at 5.2 GHz | $P_{out}$ at $P_{in} = 0$ dBm | gain at $P_{in} = -20$ dBm | PAE    |

|------------------|---------------------|-------------------------------|----------------------------|--------|

| Fresh            | 18.2 dB             | 12.5 dB                       | 17.3 dB                    | 25%    |

| After RF stress1 | 15.2 dB             | 10.6 dB                       | 14.5 dB                    | 21.6%  |

| After RF stress2 | 12.3 dB             | 7.9 dB                        | 12.9 dB                    | 9.1%   |

| After RF stress3 | 11.9 dB             | 7.3 dB                        | 12.9 dB                    | 6.6%   |

| Change1          | -16.5%              | -15.2%                        | -16.2%                     | -13.6% |

| Change2          | -32.4%              | -36.8%                        | -25.4%                     | -63.6% |

| Change3          | -34.6%              | -41.6%                        | -27.7%                     | -73.6% |

Table 2.4: Degradation of PA performance designed in [5] after RF stress.

RF stress 1:  $P_{in} = 0$  dBm,  $V_{dd2} = 3.5$  V for 10 hours, RF stress 2:  $P_{in} = 0$  dBm,  $V_{dd2} = 4.0$  V for 10 hours

RF stress3:  $P_{in} = 0$  dBm,  $V_{dd2} = 4.5$  V for 10 hours

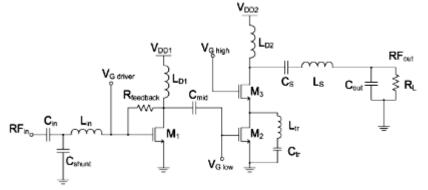

The reliability concept in a single-stage class-AB PA was investigated in [10], the simplified schematic of which is shown in Figure 2.13. Simulation results for the power-added efficiency (PAE), third-order intermodulation, and output power degradation as a function of the input power are given in Figure 2.14, showing an increase in third-order intermodulation (IM3) and a decrease in the output power after stress. Eventually, the simulation results extracted before and after AC stress for ACPR (adjacent-channel power ratio) and NPR (noise power ratio) are summarised in Table 2.5 [10]. These results prove that both parameters are degraded after AC stress.

Figure 2.13: Class-AB PA mentioned in [10] for reliability studies.

Figure 2.14: a) PAE and b) output power and IM3 degradation due to AC stress for Class-AB power amplifier in Figure 2.13 [10].

| Table 2.5: Results indicating | the degradation | of ACPR and NPR for | class-AB PA after | AC stress [10]. |

|-------------------------------|-----------------|---------------------|-------------------|-----------------|

|                               |                 |                     |                   |                 |

| Output power<br>(dBm) | ACPR (dBm) |          | Input power | NPR (dBm) |          |  |

|-----------------------|------------|----------|-------------|-----------|----------|--|

|                       | Fresh      | Stressed | (dBm)       | Fresh     | Stressed |  |

| -20                   | 69.11      | 62.30    | -40         | 53.50     | 47.87    |  |

| -10                   | 64.59      | 57.92    | -30         | 39.39     | 34.39    |  |

| 0                     | 43.50      | 38.38    | -20         | 17.53     | 13.14    |  |

| 10                    | 23.68      | 19.58    | -10         | 13.66     | 12.49    |  |

| 20                    | 17.82      | 13.62    | 0           | 12.94     | 9.13     |  |

#### **2.7 Conclusion**

Two physical-degradation mechanisms in silicon-based devices, called Hot-Carrier Injection (HCI) and Bias Temperature Instability (BTI), were studied in this chapter. Then, these mechanisms were compared, and it is concluded that HCI will make more destructive effects on device DC and small-signal characteristics. Because of device degradation, RF circuits will experience performance degradation, and this unwanted change was illustrated by comparing LNA and PA performance before and after stress. This information is necessary, as the first step, to find reliability models predicting device ageing during the design process. The next chapter will discuss how to model ageing mechanisms and will present some analytical models published in the literature, which can provide us with a clear path to find our final age model for power-amplifier ageing.

# Chapter 3

# **Physical Models to Describe Device Degradation**

#### **3.1 Chapter Abstract**

After identification of the main ageing/degradation mechanisms, developing theoretical models able to predict degradation is now the second step toward design modification to improve reliability. Each model is expected to predict degradation under both DC and RF stresses. So, the concept of the Quasi-Static approach is, then, explained to change static (DC) models into RF counterparts.

#### **3.2 Introduction**

All degradation models consist of items describing physical mechanisms initiating degradation in devices. For example, due to holes generated via impact ionisation, there is a correlation between the hot-carrier rate and the substrate current in NMOS. So, an age model can be extracted as a function of the substrate current in n-type MOSFETs. For PMOS, charge trapping into the oxide layer is responsible for the degradation and this degradation can also be modelled by using the gate current [4, 31, 33-36]. In addition, DC stresses ( $V_{gs}$  and  $V_{ds}$ ) may be defined as determinative factors in models. Finally, a model is expected to cover recoverable behaviour after removing BTI stress. In this chapter the Power Law, as the basis of almost all ageing models, and its derivatives for HCI and BTI under DC and AC bias conditions, are explained. Then, some examples of such predictive age-models will be represented and summarised in a table.

#### 3.3 Power Law and Quasi-Static Approach

Reliability models, irrespective of whether they predict device degradation due to either HCI, BTI, or other mechanisms, are expressed in the form of a Power Law which has been empirically verified as equation (3.1) [3, 7]:

$$\Delta P = A \cdot t^n \tag{3.1}$$

where *P* is a device electrical parameter,  $\Delta P$  is the degradation of the parameter *P* from its original value under stress, *A* is a pre-factor obtained according to the technology used, and *t* is the stress time. In [3], three main criteria were mentioned which can affect the pre-factor *A*: (i) Single Vibrational Excitation (SVE), (ii) Electron-Electron Scattering (EES), and (iii) Multiple Vibrational Excitation (MVE). However, in [7] it is indicated that the power law is based on HC transport mechanisms including single-carrier events (SCE) and multi-carrier events (MCE). Power *n* represents the degradation rate, the value of which varies between 0.1 and 1 dependant on the technology used in the design. Based on RelXpert parameters for BSIM4 model, *n* is 0.344.

The power law in the form of (3.1) only works to describe device degradation under DC or lowfrequency stress (static mode). However, transistors in actual circuits usually operate under timevarying bias conditions (such as those in local oscillators and power amplifiers). Therefore, the conventional form of power law should be extended into an AC/RF or dynamic one, otherwise the evaluation will be inaccurate. This conversion is executable if history effects are neglected and the "Quasi-Static" approximation is considered as a sequence of DC conditions [3, 20, 30, 31, 32, 37-39]. The final formalism for the power law in the RF domain, after applying this approximation, can be written as (3.2) called "age function" [3].

$$\Delta P = \left[ \int_{0}^{t} A^{\frac{1}{n}}(t) dt' \right]^{n}$$

(3.2)

Based on these two cases, all mechanisms are modelled, and their effects are predicted. The following sub-sections represents models developed to predict the ageing due to HCI, BTI, TDDB, and sub-threshold leakage currents in both static and dynamic modes.

#### 3.3.1 HCI-based Models

HC models are based on carrier-transport mechanisms and can be written in the form of (3.1) or of a saturation power law as (3.3), where  $N_0$  is density of dangling bonds [3, 7]:

$$\Delta P = N_0 \times [1 - exp(-A, t^n)]$$

(3.3)

Some references expand (3.1) for a specific DC parameter. For instance, (3.4) presents a static model to predict the HC-induced threshold-voltage degradation in CMOS transistors where  $n_{HC} \approx 0.5$  represents the time exponent and  $\alpha_3$  and  $\alpha_4$  are technology-dependent voltage-scaling parameters [9]. The effect of  $V_{qs}$  and  $V_{ds}$  on the degradation is also modelled in this equation.

$$\Delta V_{th} \approx \frac{1}{\sqrt{L}} e^{(\alpha_3 V_{gs})} \cdot e^{(\alpha_4 V_{ds})} \cdot t^{n_{HC}}$$

(3.4)

Another derivative of the power law is introduced based on the substrate current  $I_{sub}$ , or the impact-ionisation current  $I_{ii}$ , as a consequence of the correlation between the number of HCs and the number of holes generated via the impact-ionisation effect, as mentioned before. In these models,  $\frac{I_{sub}}{I_d}$  or  $\frac{I_{b,ii}}{I_d}$  is used as a criterion representing probability that a single carrier has sufficient energy to start device degradation [34]. A physical model describing the worsening of the saturated current,  $I_{d,sat}$ , over time is, for instance, expressed as [3, 4]:

$$-\Delta I_{d,sat}\% = \left[K_{HC} \frac{I_d}{W} \left(\frac{I_{b,ii}}{I_d}\right)^m t\right]^n$$

(3.5)

where W is the channel width and m represent the ratio between the critical energy that an electron must have in order to create an interface trap ( $\varphi_{it}$ ) and the minimum energy that a hot electron must have in order to create an impact ionisation ( $\varphi_i$ ) [31].

Recently, it has been found that HCD can follow an apparent two-stage law under some stress conditions in planar devices because of generating more than one kind of trap. So, the traditional approaches to evaluate HC effects can be faced with several challenges during the scaling process. Additionally, self-heating effects can aggravate the FinFET operation due to its narrow structure and HCD study is faced with great challenges for FinFETs [7]. Therefore, in [7] hot-carrier degradation was studied for this technology from a trap-based approach rather than using a conventional carrier-based approach (equations (3.1)-(3.5)) so that, for the first time, considers the self-heating issue. The proposed trap-based HC model, which was verified in both n- and p-type FinFETs, improves the design margin and is introduced for threshold-voltage degradation as follows [7]:

$$\Delta V_{th} = N_0 \times [1 - exp(-AR_1 t^n)] + AR_1 \times log(1 + C_1 t) + AR_2 \times log(1 + C_2 t) + k.BTI$$

(3.6)

with

$$k = 1 - 0.5 \left(\frac{V_{ds}}{V_{gs}}\right), AR = A \left(V_{gs} - V_{th}\right)^m exp\left(\frac{-b}{V_{ds} - V_{dsat}}\right)$$

(3.7)

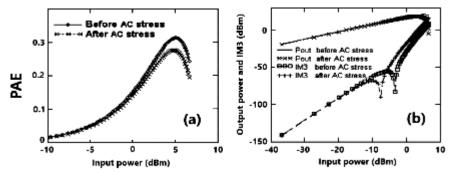

where AR is the age rate and b is a factor. Refer to [7] for more information and finding equations required to calculate  $AR_1$  and  $AR_2$ . Only a portion of BTI should be counted in the total degradation because BTI is measured under  $V_{ds} = 0V$ , while under HCD bias conditions, nonzero  $V_{ds}$  can raise the potential and decrease the BTI near the drain side. The comparison between predicted and experimental results for nFinFETs and pFinFETs using the model expressed in (3.6) is presented in Figure 3.1, indicating acceptable agreement between the two cases.

Figure 3.1: Comparison of predicted and experimental data for a) pFinFET ( $V_g$ -dependence), b) pFinFET ( $V_d$ -dependence), c) nFinFET ( $V_g$ -dependence), d) nFinFET ( $V_d$ -dependence) [7].

#### 3.3.2 BTI-based model

The BTI is best modelled based on the threshold-voltage degradation under AC stress [2, 7, 9]:

$$\Delta V_{th} \approx e^{(\alpha_1 V_{gs})} t^{n_p} + V_{qs}^{\alpha_1} [C_R + n_R \log t]$$

(3.8)

Here,  $\alpha_1$  and  $\alpha_2$  are voltage-scaling factors and  $n_p$  and  $n_R$  are time exponents. All these parameters, along with  $C_R$ , are all technology dependent. The first part of (3.8) shows the degradation during the stress time and the second one accounts for the relaxation or recovery of the BTI degradation after the stress is removed. Another stress and recovery NBTI model is presented in [2] for a field-effect transistor using a range of stress voltage, time, and temperature. Since parasitic series resistance and capacitance play an important role in nano-scale circuit performance, the model mentioned in this article also includes scalable geometry-dependent

parasitic capacitance and resistance of the nano-wire FET. The complete threshold-voltage degradation model presented in [2] is:

$$\Delta V_{th} = A e^{\beta E_{ox}} e^{-E_a/KT} t^n + \Delta V_{th0} [1 - \alpha (t - t_0)^n]$$

(3.9)

where A and  $\beta$  are constants including technology-dependent effects such as gate dielectric, gate metal and other related processes,  $E_{ox}$  is the oxide field at the  $Si - SiO_2$  interface,  $E_a$  shows the activation energy, k is the Boltzmann constant and T refers to the temperature. Also,  $\Delta V_{th0}$  is the degradation at the end of the stress period or at the beginning of the recovery period,  $t_0$  indicates the stress period, and  $\alpha$  is a proportionality constant. Refer to Figure 2.5 (a) to see how this equation predicts the recoverable nature of BTI degradation.

#### 3.3.3 Sub-threshold modelling

The increase of leakage current in deep sub-micrometre MOS transistors, operating below threshold, is also becoming a reliability concern. Prediction of RF stress-induced leakage is important since several RF elements are used to design a PA and they multiply the leakage current, indirectly affecting the circuit degradation. In some papers it is illustrated that hot carriers can also be generated when the transistor is turned-off. In addition, at high frequencies and when the gate voltage goes below the threshold voltage, the lateral field can change the device and circuit specifications [4, 40, 41].

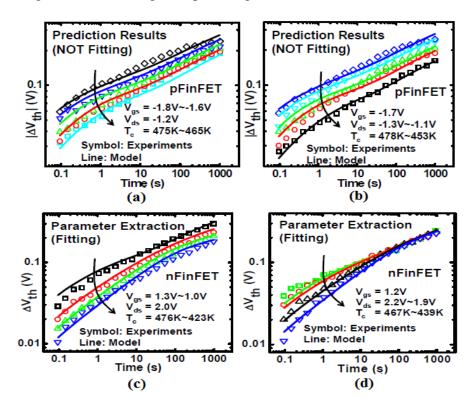

As depicted in Figure 3.2 (a), two main leakage currents are present below  $V_{th}$ : the gate-induced drain-leakage (GIDL) current which equals the bulk current when  $V_g < 0$  and the drain-induced barrier-lowering (DIBL) current which equals the drain current when  $0 < V_g < V_{th}$ . GIDL and DIBL respectively refer to the *whole current* and the *enhanced electron channel current* flowing in the Sub- $V_{th}$  region due to the reduction of  $V_{th}$  at high  $V_{ds}$ . There are other mechanisms affecting the gate leakage current, but their degradation effects are negligible and have rarely been taken into account in the literature [4, 42].

One of the frailties of conventional DC Hot-Carrier models is that they do not consider the degradation occurring in the sub-threshold region  $(V_g < V_{th})$  [3, 4]. In [4] a new DC degradation model valid for this area was proposed which is also suitable for being extended to high frequencies. By means of RF stress measurements in this reference, the frequency dependency of the sub-threshold region is also evaluated, and the Quasi-Static sum is validated. Additionally, it is possible to replace the current ratio  $(\frac{I_{b,ii}}{I_d})$  in equation (3.5) with a more empirical power function of drain voltage  $V_d$  in order for the model to be extended into the sub- $V_{th}$  region (until the OFF-

state point  $V_g = 0$ ). The proposed degradation model and its extension to the RF domain are introduced as (3.10) and (3.11), respectively:

$$-\Delta I_{d,sat} \% = \left[ \left( D \frac{I_s}{W} V_d^{m_1} + G \frac{I_b}{W} V_d^{m_2} \right) t \right]^n$$

(3.10)

$$-\Delta I_{d,sat}\% = \left[\int_0^t \left(G\frac{I_b(t)}{W}V_d^{m_2}(t)\right)dt\right]^n$$

(3.11)

Figure 3.2: a) Illustration of GIDL and DIBL leakage currents in Sub-Threshold region, b) TTF (10% degradation of  $I_{d,sat}$ ) for different  $V_q - V_d$  configurations in the sub-threshold area [4].

The DIBL contribution is neglected in (3.11) since no current is flowing along the channel and the whole degradation will be due to GIDL stress. Figure 3.2 (b) shows the simulation results for 10% degradation of  $I_{d,sat}$  (TTF<sup>1</sup>) for several  $V_g$  and  $V_d$  values. The simulation results for the contribution of each term are plotted by dotted lines. It is revealed from Figure 3.2 (b) that in the sub- $V_{th}$  region (when  $V_g > 0$ ), DIBL degradation is predominant, but below  $V_g = 0$  the GIDL current reduces drastically the time to failure, de-escalating the device performance.

Eventually, the authors in [40, 41] quantified the behaviour of the stress-induced leakage current in terms of the stress experienced by a Heterojunction Bipolar Transistor (HBT) under RF operating conditions. The damage characteristics observed during RF operation, particularly the base leakage and collector-base (CB) junction failure, are investigated in detail using DC stress methods. The model predicting RF degradation, and the total leakage lifetime, are given as (3.12) and (3.13), respectively:

$$\Delta I_B \propto \sqrt{I_E \cdot e^{-\frac{\beta}{(V_{CB} + V_{bi})^{1/2}}} \cdot t}$$

(3.12)

$$\Delta I_{B,lifetime} = \Delta I_{B,dev} \cdot n \cdot \sqrt{t \cdot d}$$

(3.13)

<sup>&</sup>lt;sup>1</sup> Time to Failure

where  $\beta$  is a factor close to 0.53,  $V_{CB}$  is the collector-base voltage,  $I_E$  is the emitter current,  $\Delta I_{B,dev}$  represents the leakage from a single device in one second, *n* shows, here, the total number of parallel devices, *d* refers to the duty cycle, and  $V_{bi}$  is input bias voltage. With various bias voltages, the predicted excess base currents are in reasonable agreement with the RF stress results, as shown in Figure 3.3 [40].

Figure 3.3: Comparison of predicted and measured RF stress-induced  $\Delta I_B$ , scaled by predicted base current  $I_{B,pre}$  [40].

Table 3.1 summarises several models proposed in the literature to model device reliability under different kinds of stresses. As is easily seen, HCI is considered as the most important phenomenon affecting all DC and small-signal parameters and, consequently, device RF performance. Clearly, BTI is the next physical mechanism which can degrade the performance of a device. However, there is no direct model to predict the degradation induced by time-dependent breakdown mechanisms, and the simple power law in (3.1) is the only equation available to model TDDB.

#### **3.4 Conclusion**

Reliability is becoming an undeniable part of RF device and circuit design. A correct and precise reliability evaluation contains two main steps: (i) identification of physical mechanisms accelerating device ageing and, then, (ii) introducing analytical models for these mechanisms to predict degradation of device parameters. This chapter provides us with an overview of reliability models for HCI, BTI, and sub- $V_{th}$  induced degradation. It is theoretically shown in Table 3.1 that hot carriers impose damaging effects on all parameters and HCI is, therefore, considered as the most severe degradation phenomenon. However, all models have been developed at the device level. If these device-level models are combined with circuit-design concepts, more dependable circuits are implemented using the new generation of reliability models. One state-of-the-art age model for PA design will be developed in the next chapter, combining device and circuit characteristics.

| Mechanism      |                                                                                                                                                                                                                          | ected De<br>Parameter  |                                          | Stress   | Model                                                                                                                                         | Device                                                                         | Deferrer                          |                 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------|-----------------|

| Witchamsm      | DC                                                                                                                                                                                                                       | Small                  | RF                                       | 511033   | DC                                                                                                                                            | Quasi-Static                                                                   | Device                            | Reference       |

|                |                                                                                                                                                                                                                          | -<br>signal            |                                          |          |                                                                                                                                               |                                                                                |                                   |                 |

|                | I <sub>dsat</sub>                                                                                                                                                                                                        | C <sub>gd</sub> ,      | $f_t$ ,                                  | Ageing   | 1-DC Power Law [22]<br>2 Al $- A(t) t^{n}$ [2]                                                                                                | $1 - \Delta I_{ds(lin)} = \left[\int_0^t A(t)^{\frac{1}{n}} dt'\right]^n, [3]$ | 1- Global<br>Foundaries 45 nm     |                 |

|                | I <sub>dlin</sub>                                                                                                                                                                                                        | C <sub>gs</sub> ,      | f <sub>max</sub> ,                       | DC       | $2 - \Delta I_{ds(lin)} = A(t) t^{n}, [3]$ $2 - \frac{\Delta NF_{min}}{\Delta NF_{min}} = -\frac{1}{2} \frac{\Delta g_{m}}{\delta g_{m}} [1]$ |                                                                                | RFSOI                             |                 |

|                | $V_{th}$                                                                                                                                                                                                                 | G <sub>m</sub> ,       | NF <sub>min</sub>                        | RF       | $3 - \frac{\Delta NF_{min}}{NF_{min} - 1} = -\frac{1}{2} \frac{\Delta g_m}{g_m}, [1]$                                                         | $2\Delta I_{d,sat} \% =$                                                       | 2- nMOSFET (Si)                   | F1 41           |

|                | U0                                                                                                                                                                                                                       | G <sub>ds</sub> ,      | Gain                                     | AC       | $4-\Delta g_m = \frac{\partial g_m}{\partial v_{th}} \Delta V_{th} + \frac{\partial g_m}{\partial \mu_n} \Delta \mu_n, [1]$                   | $\left[\int_0^t \left(G \frac{I_b(t)}{W} V_d^{m_2}(t)\right) dt\right]^n [4]$  | 3-pMOSFET (Si)<br>4-CMOS (160 nm) | [1-4]<br>[6-10] |

|                | SS**                                                                                                                                                                                                                     | G <sub>db</sub> ,      | IIP3                                     | Dynamic  | 5- $\Delta V_{th} \approx \frac{1}{\sqrt{L}} e^{(\alpha_3 V_{gs})} \cdot e^{(\alpha_4 V_{ds})} \cdot t^{n_{HC}}, [9]$                         |                                                                                | 5- CMOS (65 nm)                   | [22-24]         |

|                |                                                                                                                                                                                                                          | $R_d$ ,                |                                          |          | $6-\Delta I_{d,sat}\% = \left[ \left( D \frac{I_s}{W} V_d^{m_1} + G \frac{I_b}{W} V_d^{m_2} \right) t \right]^n [4]$                          |                                                                                | 6- CMOS (28 nm)<br>7- MOSFET      |                 |

| HC             |                                                                                                                                                                                                                          | R <sub>s</sub> ,       |                                          |          | 7-<br>$\Delta V_{th} = N_0 \times [1 - exp(-AR_1, t^n)] + AR_1 \times log(1 + C_1 t)$                                                         |                                                                                | (InGaAs)                          |                 |

|                |                                                                                                                                                                                                                          | $R_{g}$ ,              |                                          |          | $ AR_2 \times log(1 + C_1t) + kBTI $                                                                                                          |                                                                                | 8- FinFET                         |                 |

|                |                                                                                                                                                                                                                          | $R_{db}$               |                                          |          | $k = 1 - 0.5 \left(\frac{V_{ds}}{V_{as}}\right), AR = A \left(V_{gs} - V_{th}\right)^m exp\left(\frac{-b}{V_{ds} - V_{dsat}}\right), [7]$     |                                                                                | 9- SiGe HBT                       |                 |

|                |                                                                                                                                                                                                                          | <i>Λ</i> <sub>db</sub> |                                          |          |                                                                                                                                               |                                                                                |                                   |                 |

|                |                                                                                                                                                                                                                          |                        |                                          |          | $8-\Delta I_B \propto \sqrt{I_E \cdot e^{-\frac{\beta}{(V_{CB}+V_{bi})^{1/2}}} \cdot t}, \text{ for HBT, [41]}$                               |                                                                                |                                   |                 |

|                |                                                                                                                                                                                                                          |                        |                                          |          | 8- $\Delta I_B \propto \sqrt{I_E \cdot e^{-(t_E \cdot t_B)}} - t$ , for HB1, [41]                                                             |                                                                                |                                   |                 |

|                | I <sub>dsat</sub>                                                                                                                                                                                                        | G <sub>m</sub> ,       | $f_t$ ,                                  | Dynamic  | 1- DC power law [22]                                                                                                                          | 1                                                                              | 1- MOSFET                         |                 |

| BD/            | V <sub>th</sub><br>U0                                                                                                                                                                                                    | G <sub>ds</sub>        | f <sub>max</sub> ,<br>N <sub>min</sub> , | DC<br>RF |                                                                                                                                               |                                                                                | 2- nMOSFET (90<br>and 130 nm)     | [1]<br>[6,8]    |

| TDD8*          | 00                                                                                                                                                                                                                       |                        | Gain                                     |          |                                                                                                                                               |                                                                                | 2- CMOS (160 nm)                  | [10]            |

|                |                                                                                                                                                                                                                          |                        | IIP3                                     |          |                                                                                                                                               |                                                                                | 3- CMOS (28 nm)                   | [22]            |

|                | $V_{th}$                                                                                                                                                                                                                 | G <sub>m</sub>         | Gain                                     | RF       | 1- DC power law [22]                                                                                                                          |                                                                                | 1- GlobalFoundaries               | [2]             |

| BTI<br>(NBTI,  | I <sub>dsat</sub>                                                                                                                                                                                                        |                        | NF<br>$f_t$                              | AC<br>DC | $2 - \Delta V_{th} \approx e^{(\alpha_1 V_{gs})} t^{n_p} + V_{gs}^{\alpha_1} [C_R + n_R \log t], [9]$                                         |                                                                                | 45nm RFSOI<br>2- MOSFET (90       | [2]<br>[9]      |

| PBTI)          |                                                                                                                                                                                                                          |                        | Jt                                       | [12,14]  | $3 - \Delta V_{th} = A e^{\beta E_{ox}} e^{-E_a/KT} t^n + \Delta V_{th0} [1 - \alpha (t - t_0)^n], [2]$                                       |                                                                                | and 130 nm)                       | [22]            |