# Chapter 1 Introduction

This chapter introduces the research topic by delineating the technological background and motivating factors. An overview of the structure and content of the thesis is then described, including the original contributions of this work.

# 1.1 Background

Advances in SiGe BiCMOS technology has caused a revolution in low-cost MMIC design. Until recently, III-V compound semiconductors<sup>1</sup>, namely Gallium Arsenide (GaAs) or Indium Phosphide (InP), have dominated Silicon (Si) based technologies in millimeter-wave (mmwave) applications due to their superior electron velocity and mobility. Transistors fabricated in these materials can operate at extremely high frequencies with high gain and power, and comparatively low noise generation. However, manufacturing costs of these technologies in terms of materials and complexity are excessive in comparison to standard silicon wafer fabrication, and they do not enable efficient integration of digital logic and high-speed analog circuitry in a full System-on-Chip (SoC) approach. The relatively lossy substrate (with resistivity 1-20 $\Omega$ cm compared to 1000 $\Omega$ cm for GaAs [1]) and poor transistor performance in the mm-wave band renders current standard Radio Frequency (RF) Complementary Metal Oxide Semiconductor (CMOS) processes impracticable for the design of MMICs, therefore paving the way for SiGe innovation.

The addition of high-speed SiGe HBTs to commercial bulk CMOS processes has realised devices with transition frequency<sup>2</sup>,  $f_t$  up to 300GHz [2, 3]. Thus, combating the presence of the lossy silicon substrate and leveraging the economic benefits and high density SoC

<sup>&</sup>lt;sup>1</sup>Extrinsic semiconductors containing group II, IV or VI dopant atoms to alter electron and hole carrier concentrations at thermal equilibrium.

<sup>&</sup>lt;sup>2</sup>Transistor unity short circuit current gain frequency.

### 1.2 Motivation

integrability to yield an ideal technology for high volume, low-cost RF and mixed-signal applications.

The catalysts for increased interest in SiGe BiCMOS include the availability of unlicensed Industrial, Scientific and Medical (ISM) frequency bands in combination with the proliferation of high frequency devices such as mobile phones, Wireless Local Area Networks (WLANs), Bluetooth devices, UWB communications and so on. Traditional mm-wave applications in industry and military such as satellite communications, microwave point-to-point links and radar could also benefit from higher levels of integration and reduced product Bill Of Materials (BOM).

# **1.2 Motivation**

The motivation for this thesis has been sculptured not only by the potential to advance the field of low-cost SiGe MMIC design, but also by the realistic constraints of technology availability for prototype fabrication, funding, facilities, and of course, time. The material presented in this thesis is the result of a one year research scholarship to the Institute for Electronics (IfE) at the Swiss Federal Institute of Technology Zürich (ETHZ). During this time, research goals were defined by the opportunity to combine collaborative work on existing projects with the emerging field of automotive radar – specifically, the development of SiGe circuits for frequency synthesis. The two motivating themes are detailed in the following subsections.

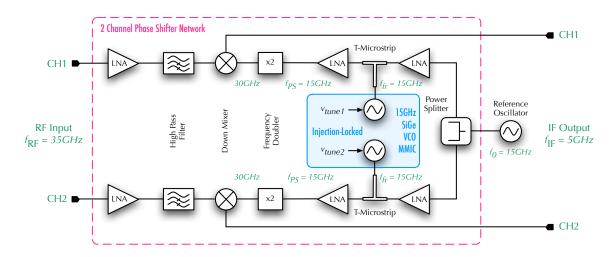

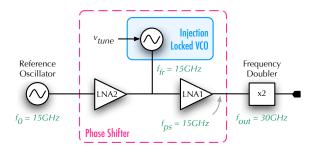

# 1.2.1 15GHz Injection-Lockable VCO

The first task was the design and fabrication of a single-ended injection lockable VCO operating at 15GHz for application in a 30GHz continuously tunable phase shifter [4]. The resultant phase shifter shall be implemented in the next revolution of the active electronic Ka-Band<sup>3</sup> antenna beam-forming network of [5], depicted in Figure 1.1. The VCO topology shall be modelled on the original topology similar to that presented in [6] and updated from the IBM SiGe BiCMOS6HP technology ( $f_t = 47$ GHz) to the faster IBM SiGe BiCMOS7WL technology ( $f_t = 60$ GHz).

VCO performance targets include accurate 15GHz output synthesis and optimised linear tuning range. Oscillator quality factor (Q) and phase noise are less critical since the slave injection locked VCO adopts similar performance to the high Q reference VCO signal. Thus

<sup>&</sup>lt;sup>3</sup>Microwave frequency band 26.5–40GHz.

Figure 1.1. Block diagram representation of the active electronic Ka-Band antenna beam-forming phaseshifting network based on the injection-locked local oscillators developed in this thesis.

in a locked state, the VCO signals are constant in frequency and exhibit excellent phase noise. A continuous tuning characteristic of the free-running VCO is vital as it defines the phase tuning continuity of the phase shifter.

The achievable phase shift of the injection-locked VCO relative to the reference oscillator is controlled by the tuning voltage  $(v_{tune})$  and can be expressed as,

$$\Delta \phi = \arcsin\left(\frac{2 \cdot (f_0 - f_{fr}(v_{tune}))}{\Delta f_{locking}}\right) \tag{1.1}$$

$$\approx \arcsin\left(\frac{(f_0 - f_{fr}(v_{tune}))}{f_0} \cdot \sqrt{\frac{P_{VCO}}{P_{inj}}} \cdot Q_{ext}\right),\tag{1.2}$$

where  $f_0$  is the reference signal frequency,  $f_{fr}$  is the free running VCO frequency,  $P_{VCO}$  is the VCO output power,  $P_{inj}$  is the injected power and  $Q_{ext}$  is the VCO external quality factor. The VCO is locked to the reference when  $f_{fr}$  is within the locking range approximated by,

$$\Delta f_{locking} = \left(\frac{2f_0}{Q_{ext}} \cdot \sqrt{\frac{P_{VCO}}{P_{inj}}}\right) \tag{1.3}$$

and resulting in the locking limits,  $f_{min,max} = f_0 \pm \Delta f_{locking}/2$ . It follows from Eq. (1.1) that a maximum phase shift of 180° is achievable when  $f_{fr}$  is within the locking range,  $f_{min} \leq f_{fr} \leq f_{max}$ .

### 1.2.2 24GHz Circuits for Short Range Automotive Radar

Vehicular radar has been identified as the next major step forward in intelligent comfort and safety systems to greatly reduce injury and fatality rates in road accidents. While luxury

# 1.2 Motivation

brands such as Mercedes-Benz and BMW are now introducing such systems, the development of low-cost radar solutions, driving broad adoption of the technology into low-end automotive markets, is still in its infancy.

SiGe BiCMOS technology has been identified as the ideal marriage between performance and cost constraints for high volume automotive radar production [7, 8]. Figure 1.2 illustrates the concepts of automotive radar and its division into the facets of Long Range Radar (LLR) and SRR.

Figure 1.2. Application of SiGe MMIC technology to automotive radar. LLR (red) at 76-77GHz penetrates up to 150m and is used for distance measurement/warning and Autonomous Cruise Control (ACC) systems. SRR (yellow) with a range up to 30m at 24GHz perform velocity measurement, collision warning and mitigation, extending ACC to include advanced stop-and-go functionality. Additional encircling SRR sensors (blue) provide safety and comfort functions including blind spot detection, parking assist, lane change assist and pre-crash readying.

A worldwide regulation has been established for the operation of automotive LRR in the 76-77GHz band, however frequency allocation for UWB SRR has not yet reached international harmony. Despite the Federal Communications Commission's (FCC) adoption of the 24GHz UWB radar sensor approach, the European Communications Committee (ECC) has granted only temporary introduction of vehicular SRR at 24Hz, transitioning to 79GHz by 2013. The Strategic Automotive Radar frequency Allocation (SARA) Group is a consortium of automotive and component manufacturers supporting the standardised development of SRR devices in the 24GHz range and recognises the operational modes described in [9].

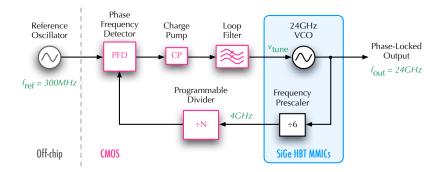

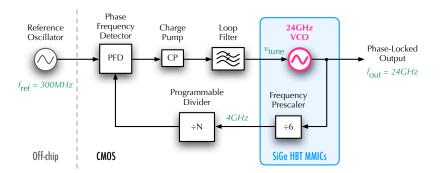

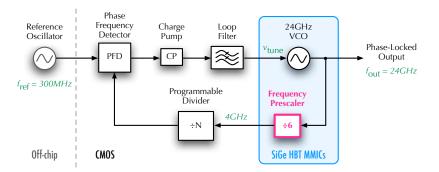

In this light, the second task of the thesis was the design of a 24GHz differential VCO and 1/6 frequency divider (or prescaler) in IBM  $0.18\mu$ m SiGe BiCMOS technology, capable of extending the operational range of an existing 4GHz CMOS phase-locked loop (PLL) to 24GHz for potential SRR applications. The existing PLL was developed for UWB radio communications as part of a concurrent IfE project [10]. Figure 1.3 shows the system level

integration of the SiGe MMICs designed in this thesis, with the CMOS components of the original work to form the SRR PLL.

**Figure 1.3.** System level block diagram of the 24GHz PLL suitable for UWB automotive SRR applications. The contributions of this thesis include the 24GHz VCO and 1/6 frequency prescaler.

# **1.3 Thesis Overview and Contributions**

This thesis has two distinct motivations; firstly, an active electronic Ka-band antenna beamforming network, and secondly, 24GHz UWB automotive SRR. The common thread that defines the scope of work carried out with respect to these two topics, is the rigorous development of low-cost SiGe circuits for frequency synthesis in millimeter-wave devices.

On a practical level, this research has achieved the MMIC design, simulation, fabrication and measurement of two 15GHz single-ended injection-lockable VCOs, a 24GHz differential cross-coupled VCO and a 24GHz synchronous 1/6 static frequency divider.

The original contributions and thesis structure are organised as follows.

Chapter 1 - Introduction This chapter provides the topical background and research motivation including current developments, along with a summary of the structure and original contributions presented in this thesis.

**Chapter 2** – **Design Theory and Process Technology** This chapter summarises the relevant theory of frequency synthesis pertaining to PLL implementation. In particular, it presents comprehensive treatment of the oscillator and frequency divider PLL subcomponents in terms of topologies, circuit analysis, and functionality. A system level view of phase noise mechanisms and models is also given. Finally, attributes of the IBM SiGe technology used for MMIC prototyping are discussed.

Chapter 3 - 15GHz Oscillator Implementations This chapter documents the rigorous design, layout and simulation of four potential 15GHz single-ended SiGe VCOs for future

implementation in the 30GHz continuous tunable phase shifter described in [4]. Two separate topologies; the emitter-tuned (E-tuned) and base-tuned (B-tuned) are investigated, and their performance characteristics compared.

The main contribution of this chapter is the application of negative resistance theory to the analytical design of single-ended SiGe VCOs at 15GHz.

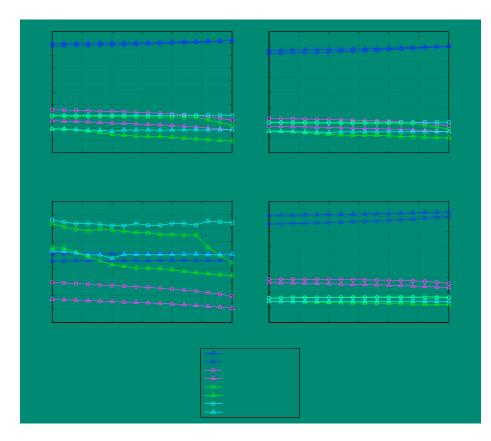

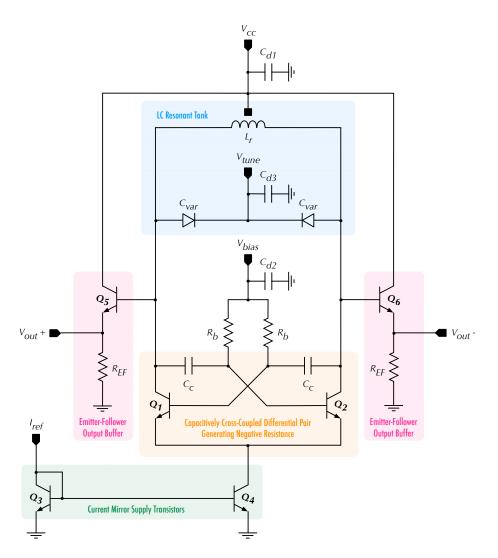

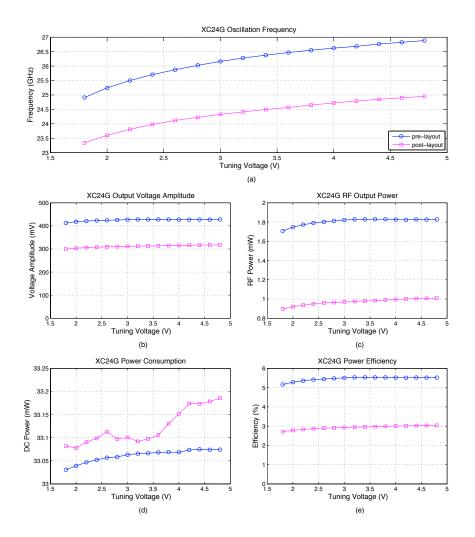

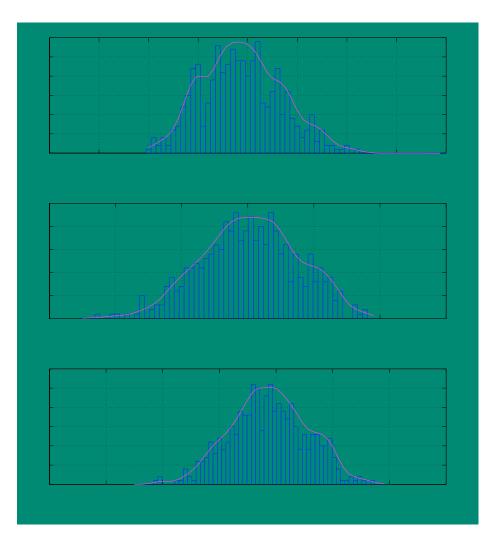

Chapter 4 - 24GHz Oscillator Implementation This chapter documents the rigorous design, layout and simulation of a 24GHz differential cross-coupled SiGe VCO suitable for frequency synthesis applications in UWB automotive SRR systems. The effects of process variation and device mismatch on critical performance metrics and fabrication yield are also investigated through Monte Carlo simulation.

The main contributions of this chapter are the application of negative resistance theory to the analytical design of differential cross-coupled SiGe VCOs at 24GHz and the investigation of the effects of wafer manufacturing variations on VCO performance – a necessary aspect of commercial, high volume MMIC design almost always neglected in the literature.

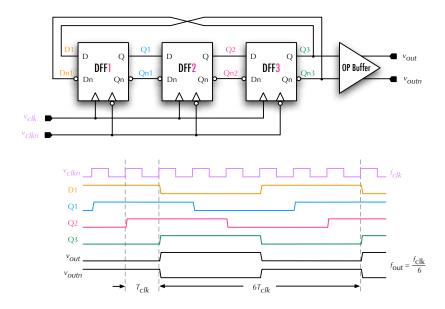

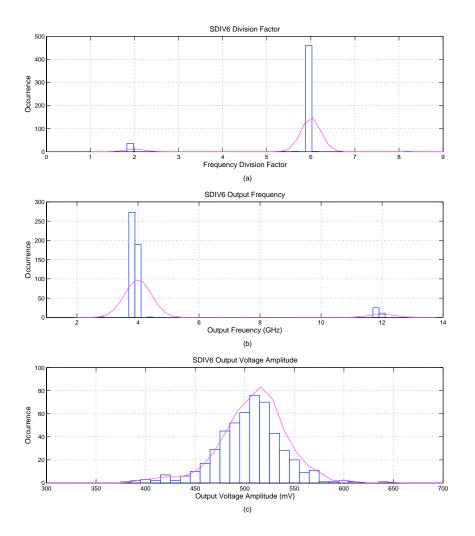

**Chapter 5** – **Frequency Prescaler Implementation** This chapter documents the rigorous design, layout and simulation of a synchronous SiGe Emitter Coupled Logic (ECL) based static 1/6 frequency divider operating at 24GHz, suitable for frequency synthesis applications in UWB automotive SRR systems. The effects of process variation and device mismatch on critical divider performance metrics are again investigated through Monte Carlo simulation.

The main contributions of this chapter are the successful implementation of a multi-stage synchronous static frequency divider topology at 24GHz in a SiGe technology with moderate  $f_t = 60$ GHz, for minimal PLL phase noise contribution – a design approach yet to be explored in the literature, and the investigation of the effects of wafer manufacturing variations on divider performance – a necessary aspect of commercial, high volume MMIC design almost always neglected in the literature.

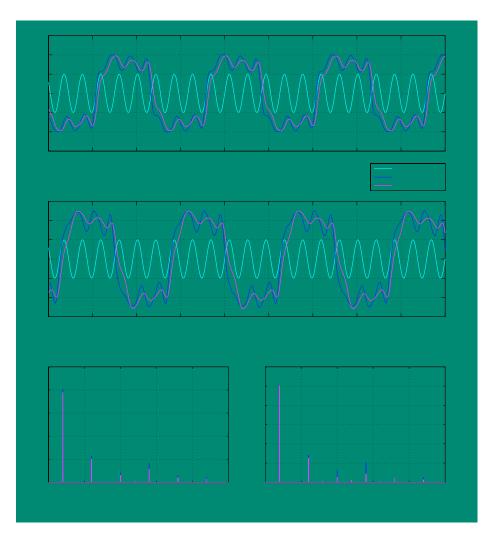

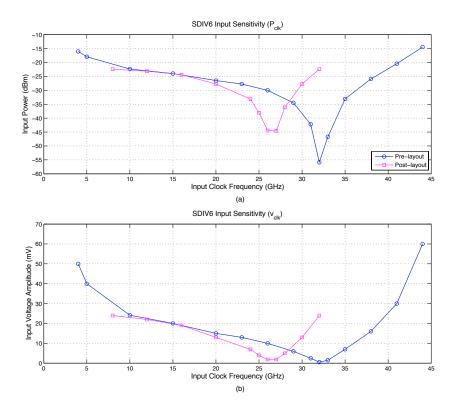

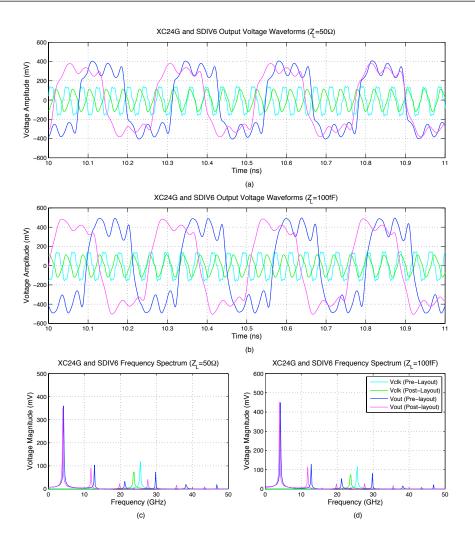

**Chapter 6** – **MMIC Fabrication and Measurement** This chapter reports the on-wafer measurement methodology and results for the four fabricated MMICs. VCO measurements include output time domain waveforms, frequency spectra, frequency and power characteristics over tuning range and phase noise using a single-ended test setup. Frequency divider measurements include self oscillation and divided output spectrum, input sensitivity, power output and DC power consumption, obtained using both single-ended and differential test setups. The measured results are also compared against analog extracted post-layout schematic simulations and the current state-of-the-art.

# Chapter 1

The main contribution of this chapter is the use of both single-ended and differential measurement techniques to confirm the accuracy of frequency divider performance characteristics – typically only single-ended measurement techniques are used to assess the performance of differential circuits in the literature.

**Chapter 7** – **Conclusion** This chapter summarises the principle outcomes of the thesis and advises areas of future research.

**Appendix A** - **Schematics** This appendix contains the final optimised circuit schematics of the MMICs designed and simulated in Chapters 3, 4 and 5.

**Appendix B** – **SDIV6 Layout Cell Views** This appendix contains additional layout cell views of the frequency prescaler core, ECL Data-latch (D-latch), Data Flip-Flop (DFF) and emitter-follower (EF) output buffer designed in Chapter 5.

**Appendix C** – **Measurement Data** This appendix contains the manually recorded onwafer measurement data presented in Chapter 6.

**Appendix D** - **MMIC Die Photos** This appendix contains photographs of the four fabricated MMIC dies.

# Chapter 2

# Design Theory and Process Technology

This chapter presents theoretical analyses of frequency synthesis pertaining to PLL implementation and the two building blocks designed in this thesis – the VCO and frequency prescaler. Common mm-wave circuit topologies are explored and the attributes which have influenced system design choices presented in later chapters. A system level view and VCO specific discussion on phase noise mechanisms and models is also given. The chapter then closes with an overview of the relevant characteristics of the IBM SiGe BiCMOS process technology used for MMIC fabrication.

# 2.1 PLL Frequency Synthesis

Frequency synthesisers are essential components in RF systems, providing precisely controlled sources for frequency conversion and continuous or pulsed carrier generation. Modern wireless system synthesisers demand frequency stability, low noise performance and sufficiently wide tuning range to accurately access the designated frequency bands in multichannel communication or radar standards. Phase-locked loops are often used for this purpose.

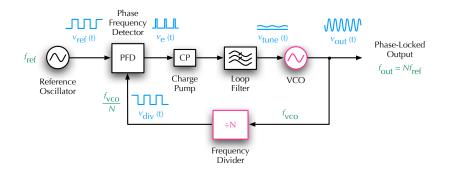

PLLs incorporate feedback control to allow a voltage controlled oscillator to accurately track the phase of a stable reference oscillator and generate a periodic output at a multiple of the reference source. The integer-N PLL block diagram of Figure 2.1 represents the indirect frequency synthesis method and indicates the signals presented to each sub-circuit.

The PLL ensures accurate local oscillator (LO) synthesis by tuning the VCO proportional to the phase error between the divided VCO output,  $v_{div}(t)$ , and a stable reference signal,  $v_{ref}(t)$ . The charge pump (CP) and low-pass filter (LPF) translate the phase difference pulse

**Figure 2.1.** Integer-N PLL block diagram, indicating the feedback frequency control mechanism used to achieve phase-lock to a high quality reference oscillator.

train signal,  $v_e(t)$ , from the phase frequency detector (PFD) into a tuning voltage,  $v_{tune}(t)$ , which alters the capacitance of the VCO resonant tank and hence its centre frequency to achieve the locked state. The loop filter also controls the dynamic properties of the PLL frequency response including; modulation bandwidth, rise time, overshoot and stability.

There are three characteristics of PLLs that are of particular importance in practical systems.

- 1. Capture range is the range of input frequency for which the loop can achieve lock.

- 2. Lock range is the input frequency range over which the loop will remain locked usually larger than the capture range.

- 3. Settling time is the time taken for the loop to lock onto a new frequency changing between multiple frequency channels for instance.

The phase noise characteristic of a PLL is similar to that of the reference source and influenced by the phase noise and spurious behaviour of the VCO.

# 2.2 Oscillator Analysis

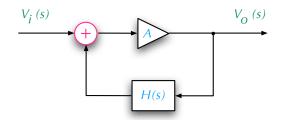

# 2.2.1 Linear Feedback Analysis

At the most fundamental level, an electrical oscillator relies on circuit nonlinearity and the presence of noise to generate a periodic output voltage or AC waveform from DC power. The circuits are designed to be both unstable, which is generally achieved through feedback, and self-sustaining. The operation of an oscillator can be described by the linear feedback circuit of Figure 2.2. The output voltage<sup>4</sup> of this positive feedback system can be expressed as

Figure 2.2. Sinusoidal oscillator linear feedback model.

$$V_o(s) = AV_i(s) + H(s)AV_o(s), \qquad (2.1)$$

where A is the amplifier voltage gain and H(s) is a frequency dependent feedback network. Further manipulation yields the overall closed loop transfer function

$$\frac{V_o(s)}{V_i(s)} = \frac{A}{1 - AH(s)}.$$

(2.2)

A self-sustaining mechanism arises when the denominator of Eq. (2.2) becomes zero,  $H(s_0) = +1$  at a particular frequency  $s_0$ . To produce constant amplitude at the output  $s_0$  must be purely imaginary,  $H(s_0 = j\omega_0) = +1$ . These conditions for steady state oscillation must be simultaneously met and are known as the Nyquist or Barkhausen criterion:

- 1. The loop gain,  $H(j\omega_0)$ , must equal unity and,

- 2. The total phase shift around the positive feedback loop,  $\angle H(j\omega_0)$  must be equal to zero or a multiple of 360°.

In most RF oscillators the feedback network consists of an LC tank (or resonant tank), the most commonly recognised being Hartley, Colpitts, Clapp and Pierce circuits. The sharpness of an oscillators output frequency response is significantly influenced by the quality factor of the LC tank while the component values determine the operation frequency. Therefore, the design of the feedback network is critical for narrowband operation.

# 2.2.2 Negative Resistance $(-g_m)$ Oscillators

Most of today's integrated RF oscillators fall into the category of negative resistance oscillators. They incorporate as few active devices (Bipolar Junction Transistor (BJT), Metal Oxide Semiconductor Field Effect Transistor (MOSFET) or IMPact ionisation Avalanche

$<sup>^{4}</sup>$ Note – although voltage is used in the explanation of the linear feedback model, the analysis is equally valid for current, waves, etc.

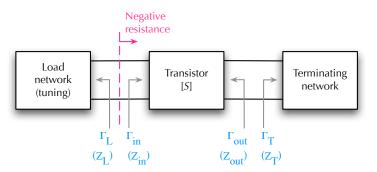

Transit-Time (IMPATT) diode) as possible to minimise noise and passive resonators using transmission line elements or lumped LC devices. A transistor oscillator can be viewed as a one-port negative resistance network by terminating the potentially unstable transistor with an impedance,  $Z_T$  designed to force the device into its unstable region. Consider the transistor circuit of Figure 2.3 where  $Z_{in} = R_{in} + jX_{in}$  is the current (or voltage) and frequency dependent input impedance of the transistor. The passive load impedance  $Z_L = R_L + jX_L$

**Figure 2.3.** Two-port negative resistance transistor oscillator circuit structure, indicating the reflection coefficients and associated impedances looking into each connection interface.

is chosen to match  $Z_{in}$  so that applying Kirchoff's voltage law to the one-port equivalent results in

$$(Z_L + Z_{in})I = 0. (2.3)$$

When oscillation occurs, I is nonzero which implies the following conditions:

$$R_L + R_{in} = 0 \tag{2.4}$$

$$X_L + X_{in} = 0. (2.5)$$

Eq. (2.5) sets the oscillation frequency while Eq. (2.4) implies  $R_{in} < 0$  since the load is passive,  $R_L > 0$ . A positive resistance means energy dissipation whereas a negative resistance implies an energy source. From Eq. (2.3), for steady state oscillation  $Z_L = -Z_{in}$ , which in terms of the reflection coefficients  $\Gamma_L$  and  $\Gamma_{in}$  can be expressed as

$$\Gamma_L = \frac{Z_L - Z_0}{Z_L + Z_0} = \frac{-Z_{in} - Z_0}{-Z_{in} + Z_0} = \frac{Z_{in} + Z_0}{Z_{in} - Z_0} = \frac{1}{\Gamma_{in}}.$$

(2.6)

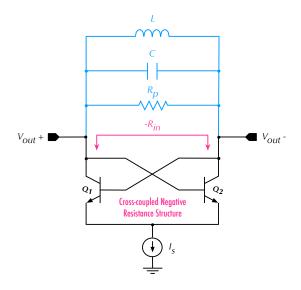

Thus, the reflection coefficient theory  $\Gamma_L\Gamma_{in} = 1$  is an instance of the linear feedback analysis in which  $\Gamma_L = H(s)$  and  $\Gamma_{in} = A$ . For oscillations to occur at the intended frequency  $f_0$ , the transistor must have sufficient negative resistance such that  $R_{in}(f_0) + R_L < 0$ . The presence of noise or power supply transients will then cause oscillation to build up. As the current increases,  $R_{in}$  must become less negative until a point where  $R_{in} + R_L = 0$  and a stable oscillatory state is reached at  $f_0$ . There are numerous possible RF oscillator circuits utilising the transconductance  $(g_m)$  of bipolar or field-effect transistors to generate negative resistance in conjunction with different resonant networks. The cross-coupled pair of Figure 2.4 is an example of a negative resistance BJT based oscillator where the impedance seen at the collector of  $Q_1$  and  $Q_2$  is calculated as  $R_{in} = -2/g_m$  [11]. Therefore, if  $R_{in}$  is greater than or equal to the equivalent parallel resistance  $R_p$  of the tank, the circuit oscillates.

Figure 2.4. Cross-coupled pair differential oscillator indicating the generation of negative input resistance.

Oscillator frequency control can be achieved by changing the inductance or capacitance of the tank circuit or by varying the bias currents for transistor oscillators which alters the contribution of device parasitic impedance to the LC network. The latter approach, however, results in output voltage amplitude changes as tuning is performed – an undesired outcome. While it is possible to get tunable discrete inductors, voltage-controlled capacitors (varactors) are the only feasible tuning device for integrated circuits. A varactor is a diode (or diode connected BJT/MOSFET) whose junction capacitance can be controlled by the DC reverse bias voltage applied across the device. Generally varactors appear either in series or parallel with a capacitor in the feedback network to offer a fine tuning range about the natural resonant frequency. As the DC bias is varied the oscillator centre frequency shifts in response, hence the term, voltage-controlled oscillator. The capacitance range of the varactors dictates the available tuning range of the oscillator.

# 2.2 Oscillator Analysis

# 2.2.3 Microwave Oscillator Designs

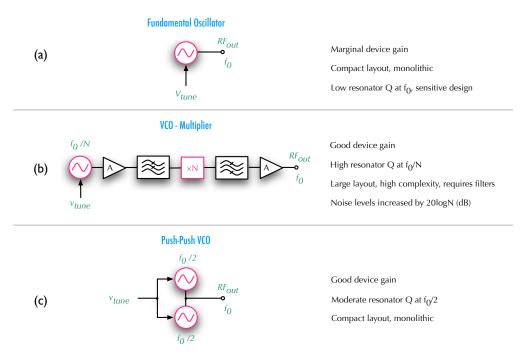

There are currently three main approaches to MMIC oscillator design at mm-wave frequencies. The topological block diagrams are shown in Figure 2.5 along with their basic implementation characteristics. Fundamental VCOs simply generate an output at the desired frequency, how-

Figure 2.5. The three basic mm-wave VCO implementations: (a) fundamental oscillators directly generate the desired output frequency, (b) VCO-multipliers isolate higher order harmonics from a lower fundamental VCO frequency, and (c) push-push VCOs add second harmonics of lower odd mode VCO frequencies.

ever they are only feasible if the device technology has sufficient gain at that frequency. Until recently, silicon based integrated technologies have not presented enough gain at microwave frequencies.

VCO-multipliers incorporate a VCO designed to operate at a more modest frequency  $f_0/N$  (typically  $f_0/2$  or  $f_0/3$ ) and employ a frequency multiplier to convert the signal to the millimeter-wave realm. While active device gain and resonator Q are much better at the lower centre frequency, the additional circuitry required to isolate the desired higher order harmonic increases complexity, chip area and output noise levels.

Push-push VCO designs consist of two fundamental frequency oscillators operating at  $f_0/2$ in odd mode so that the fundamental frequencies add out of phase, cancelling, and the second harmonics add in phase, thus producing the required output. The performance of this topology is heavily reliant on the anti-phase accuracy of both oscillators and therefore layout symmetry and device matching are paramount.

# 2.3 Phase Noise

Oscillator circuits are susceptible to noise just like all analog circuits. However, the amount of noise produced by a frequency synthesiser or oscillator is critically important in practice because it can seriously degrade the performance of a wireless system.

# 2.3.1 System Level View

Noise injected via the oscillators constituent devices (active and passive) or by external means may influence both the centre frequency and the amplitude of the output signal. Amplitude changes can, in general, be neglected because there exists circuit techniques for eliminating such disturbances. The short-term random deviation of frequency can be alternatively viewed as random variation of the period or deviation of the zero crossing points of the output waveform from its ideal position along the time access. This phenomenon is more commonly known as phase noise in the analog design world or jitter in the digital design world and has more serious implications than amplitude inaccuracies.

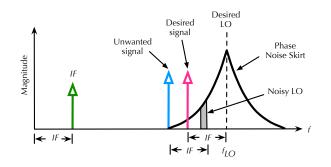

Phase noise not only adds to the overall noise level (minimum synthesiser output noise floor) but in digital systems, clock jitter directly affects timing margins of logic circuits hence limiting system speed. In analog RF systems, a generic transceiver for instance, phase noise in the LO leads to corruption of both the downconverted and upconverted signals by translating undesired nearby signals to the frequency of interest, thus limiting detection sensitivity, selectivity, channel bandwidth and output purity of the transceiver. Modern digital modulation schemes such as Phase Shift Keying (PSK) and Quadrature Amplitude Modulation (QAM) used in WLAN systems are particularly affected by the presence of phase noise, introducing uncertainty during signal detection and degrading the Bit Error Rate (BER). Figure 2.6 illustrates how phase noise effects the selectivity of a receiver by down-converting signals adjacent to the desired signal frequency. The figure assumes a heterodyne architecture with LO at  $f_{LO}$  to translate the desired signal to an intermediate frequency (IF). Unfortunately, a nearby unwanted signal can be down converted to the same IF due to the LO's phase noise spectrum. The portion of phase noise spectrum leading to this conversion is situated at an offset from the carrier equal to the IF from the unwanted signal – a process known as reciprocal mixing. Essentially resulting in spectral overlapping and significant degradation of the wanted signal.

**Figure 2.6.** Illustration of how LO phase noise can lead to the reception of an undesired signal close to the frequency of the desired signal in a heterodyne receiver architecture.

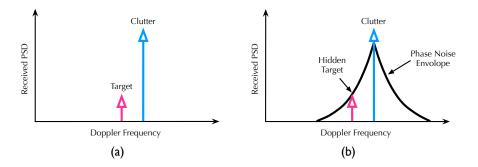

In terms of radar systems, internally generated phase noise degrades sensitivity and target detection performance. The presence of phase noise sidebands around the carrier and hence the reflected signal (or echo) spectrum from large returns such as clutter<sup>5</sup> can completely obscure the echo from smaller targets in close proximity. This potentially makes the smaller target indistinguishable from the received noise, as illustrated in Figure 2.7. The measure of

**Figure 2.7.** Receiver power spectral density (PSD) of (a) an ideal radar exhibiting no phase noise where the target and clutter can be differentiated by their Doppler frequencies, and (b) a radar with phase noise where the target is rendered indiscernible from the broadened clutter spectrum.

a radar's ability to discern moving target signals superimposed on clutter signals is known as Sub-Clutter Visibility (SCV). The extent of clutter spread is dependent on the level of the clutter signal, the radar's phase noise characteristic and the target range [12].

The specific effects of phase noise on radar performance depends on the type of radar implemented, for example Frequency Modulated Continuous Wave (FMCW), pulsed, UWB and so on. [13, 14] have studied the effects of transmitter phase noise on FMCW based radar and identify a broadening of the clutter velocity spectrum, increased velocity and range measurement errors and reduced SCV.

<sup>&</sup>lt;sup>5</sup>Unwanted radar reflections from ground, sea, atmospheric conditions, urban objects, jamming etc.

In Doppler radar systems, frequency shifts in the reflected signal are used to determine the velocity of moving objects. As such, small Doppler frequency shifts from slow moving targets close to the carrier signal demand a high level of close-in carrier phase noise purity to be detectable. The phase noise requirements become more relaxed as the target speed and proximity to the carrier increase due to the larger Doppler frequency shifts.

#### 2.3.2 Phase Noise Mechanisms

The characterisation of phase and frequency fluctuations in electrical oscillator circuits has been the subject of many detailed studies in recent times [15, 16, 17, 18, 19, 20]. Complex mathematical models have been presented, however they are often only applicable to specific classes of oscillators because of the simplifications assumed. Modern Computer Aided Design (CAD) tools can simulate the presence of phase noise however they rely on the accuracy of the available design kit device models and still have limited ability to model the nonlinear nature of oscillator noise sources. Nevertheless, phase noise in oscillators is spawned from noise sources divided into two main categories – device noise and interference. Device noise encompasses thermal, shot and flicker noise (or 1/f noise) along with the Q of resonant devices. Interference on the other hand arises from substrate noise (LO leakage, self mixing, nonlinear device harmonic components, etc.) and supply noise.

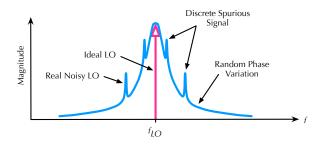

The output of an ideal sinusoidal oscillator can be expressed as,

$$v_o(t) = A\cos[\omega_{LO}t + \phi], \qquad (2.7)$$

where A is the amplitude,  $\omega_{LO}$  (=  $2\pi f_{LO}$ ) is the frequency, and  $\phi$  is the fixed phase of the signal. The frequency spectrum of such a signal would consist of a pair of Dirac delta functions<sup>6</sup> (impulses) at  $\pm f_{LO}$ , as shown only in the positive frequency region in Figure 2.8. In reality, however, the output voltage of a typical oscillator or frequency synthesiser is more accurately defined as

$$v_o(t) = V_o[1 + A(t)] \cos[\omega_{LO}t + \phi(t)], \qquad (2.8)$$

where A(t) represents the amplitude fluctuations of the output, and  $\phi(t)$  represents the phase variation of the output waveform. A consequence of the time varying amplitude and phase is the addition of sidebands in the oscillators output spectrum around the centre frequency,  $f_{LO}$ . This effect is also shown in Figure 2.8. The discrete spikes represent spurious signals due to oscillator harmonics or mixer products. Phase noise due to random fluctuations caused by device noise and interference appear as a broad continuous distribution localised about the output signal.

<sup>&</sup>lt;sup>6</sup>A function  $\delta(x)$  that equals infinity at one value of x and zero elsewhere.

Figure 2.8. Frequency spectrum of an ideal oscillator consisting of a delta function at the operating frequency  $f_{LO}$  and a practical oscillator indicating the presence of spurious noise frequency peaks and noise sidebands around the operating frequency.

Phase noise is defined as the ratio of power in one phase modulation sideband to the total signal power per unit bandwidth (1Hz) at a given offset,  $\Delta \omega$  from the signal frequency. This leads to the general definition for single-sideband phase noise spectral density, denoted as  $\mathcal{L}(\Delta \omega)$ ,

$$\mathcal{L}(\Delta\omega) = 10 \log \left[ \frac{P_{sideband}(\omega_{LO} + \Delta\omega, 1Hz)}{P_{carrier}} \right].$$

(2.9)

This definition includes the effect of both amplitude and phase fluctuations and has units of decibels relative to the carrier power per Hertz, dBc/Hz.

The advantage of this figure-of-merit (FOM) is its ease of measurement, however since it indicates the cumulative effect of both amplitude and phase noise it does not provide information about the severity of each noise source separately. Knowing the specific contributions of amplitude and phase variations greatly benefits the designer in devising noise reduction mechanisms.

# Leeson's Oscillator Phase Noise Model

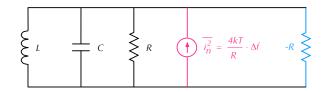

One of the classical oscillator phase noise models on which many of the new theories are based is the linear time invariant (LTI) model described by Leeson. Leeson's model approximates the noise power spectral density of tuned tank oscillators, assuming that the oscillator is a linear positive feedback system as previously discussed in Section 2.2.1.

Initially, consider the oscillator system as a ideal oscillator with the only noise contribution coming from the lossy tank, as shown in Figure 2.9. The tank resistance has to be compensated by the active device generating negative resistance -R. The noise current source associated with this lossy tank conductance can be expressed by the mean-square value,

$$\overline{i_n^2} = S_n(f) \cdot \Delta f = \frac{4kT}{R} \cdot \Delta f \tag{2.10}$$

Figure 2.9. Oscillator noise model with LC resonant tank, loss resistance, associated noise current source and active device generating negative resistance.

where  $S_n(f)$  represents the noise spectral density, k is Boltzmann's constant  $(1.38 \times 10^{-23})$ Joules/Kelvin), T is the temperature and R is the tank resistance. This noise current source converts to a voltage noise source when multiplied by the effective tank impedance. During oscillation the unstable active device will generate sufficient negative resistance to exactly cancel the positive resistance of the tank. Therefore, the effective impedance seen by the noise current source is that of a perfectly lossless parallel LC network that can be approximated for small offset frequency  $\Delta \omega$  from the centre frequency as,

$$Z(\omega_{LO} + \Delta\omega) \approx j \cdot \frac{\omega_{LO}L}{2\frac{\Delta\omega}{\omega_{LO}}}$$

(2.11)

provided that  $\Delta \omega \ll \omega_{LO}$ . This expression can be rewritten incorporating the unloaded tank quality factor,

$$Q = \frac{R}{\omega_{LO}L} = \frac{1}{\omega_{LO}GL},\tag{2.12}$$

revealing the magnitude of the tank impedance as,

$$Z(\omega_{LO} + \Delta\omega) = \frac{1}{G} \cdot \frac{\omega_{LO}}{2Q\Delta\omega} . \qquad (2.13)$$

The spectral density of the mean-square noise voltage can then be determined by multiplying the spectral density of the mean-square noise current by the squared magnitude of the tank impedance,

$$\frac{\overline{v_n^2}}{\Delta f} = \frac{\overline{i_n^2}}{\Delta f} \cdot Z^2 = 4kTR \left(\frac{\omega_{LO}}{2Q\Delta\omega}\right)^2.$$

(2.14)

Note that increasing resonator Q reduces the noise density and that the output noise power spectral density falls as the inverse-square of the offset frequency.

Normalising the mean-square noise voltage density of Eq. (2.14) to the mean-square oscillator voltage and representing the result as a ratio in decibels gives the following equation for the normalised single-sideband noise spectral density,

$$\mathcal{L}(\Delta\omega) = 10 \log \left[\frac{2kT}{P_{LO}} \cdot \left(\frac{\omega_{LO}}{2Q\Delta\omega}\right)^2\right].$$

(2.15)

#### 2.3 Phase Noise

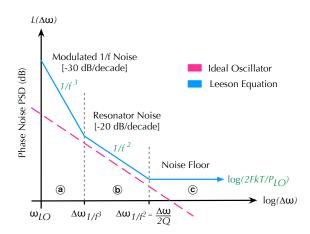

The above equation allows us to draw some important conclusions about the RLC resonant tank of an ideal oscillator; improving tank Q and increasing the LO signal power are essential for low phase noise design. According to Leeson, this expression alone is insufficient for describing the complete phase noise spectrum of an oscillator, however it does represent the region proportional to  $1/f^2$  shown graphically in Figure 2.10 with a theoretical slope of -20 dB/decade.

Now considering additive flicker (1/f) and thermal noise from the active devices within the oscillator core or associated buffer amplifiers, the phase noise expression (referred to as Leeson's equation) becomes,

$$\mathcal{L}(\Delta\omega) = 10 \log\left[\frac{2FkT}{P_{LO}} \cdot \left(1 + \left(\frac{\omega_{LO}}{2Q\Delta\omega}\right)^2\right) \cdot \left(1 + \frac{\Delta\omega_{1/f^3}}{\Delta\omega}\right)\right]$$

(2.16)

where  $P_{LO}$  is the oscillator output power,  $\Delta \omega$  is the LO offset frequency, Q is the loaded quality factor of the tank and  $\omega_{LO}$  is the LO frequency. F is an empirical fitting parameter (often referred to as the device noise factor) determined from measurements and accounts for the increased noise in the  $1/f^2$  region when compared to that predicted by the ideal oscillator assumption. The parameter  $\Delta \omega_{1/f^3}$  is the boundary between the  $1/f^2$  and  $1/f^3$  regions and is equal to the 1/f corner of the active device noise. At around the resonator 3dB bandwidth

**Figure 2.10.** Leeson's LTI oscillator phase noise model predicting three typical regions relative to the centre frequency  $\omega_{LO}$  on a logarithmic scale: (a) Additive 1/f active device noise contribution. (b) Passive resonant tank generated noise. (c) Thermal noise floor of resistive oscillator losses.

$\Delta \omega/2Q$  offset from the LO centre frequency, the phase noise spectrum flattens off revealing the spectral noise floor.

The Leeson model provides a realistic interpretation of the generalised oscillator phase noise spectrum, however it relies heavily on the measured fitting parameters and therefore has

# Chapter 2

limited predictive power. Nevertheless, several insights can be gained from Leeson's equation into phase noise reduction techniques including; maximising LO power or equivalently the output voltage swing, maximising resonator Q and utilising active devices with low 1/f flicker noise to reduce the close-in phase noise component and noise floor.

# 2.4 Frequency Dividers

There are essentially two types of mm-wave frequency divider topologies prevalent in the literature and suitable for MMIC PLL implementation – the static and the dynamic.

### 2.4.1 Static Divider

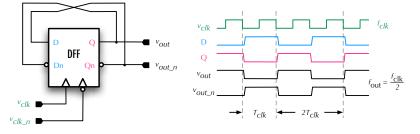

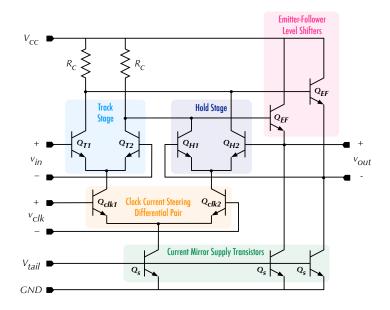

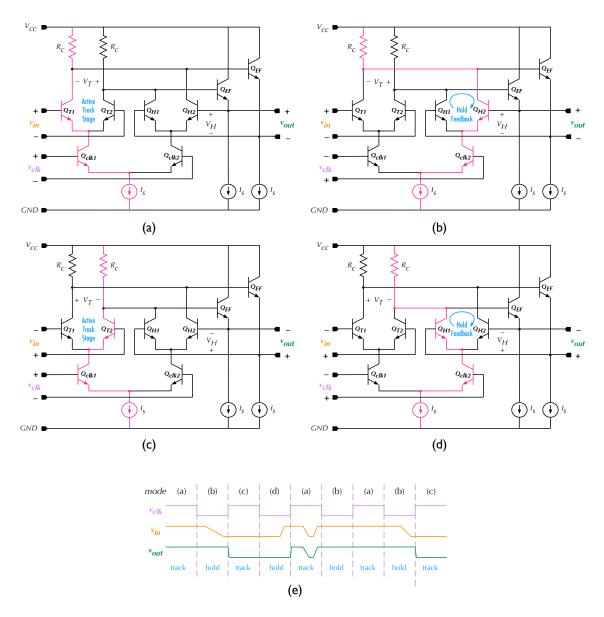

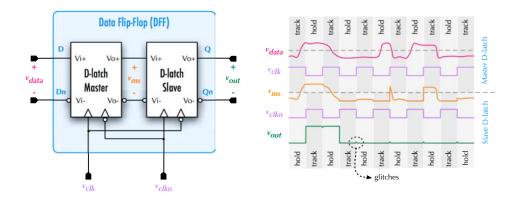

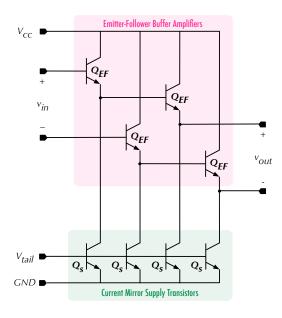

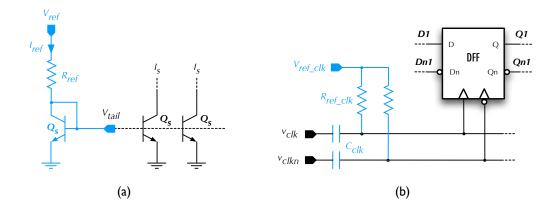

Static frequency dividers are based on the conventional Data Flip-Flop topology with negative feedback as shown in Figure 2.11, including switching signal waveforms. The differential

**Figure 2.11.** Block diagram of the DFF based 1/2 static frequency divider element and principle of operation waveforms.

input signal is applied to the clock ports of the DFF while the negative feedback mechanism produces an output at  $f_{out} = f_{clk}/2$ , provided that the propagation delay through the DFF and feedback wiring is less than the input period,  $T_{clk}$ .

The DFFs are constructed from two master-slave connected Data-latches operating on opposite clock phases. The D-latches are typically designed using fully differential ECL [21, 22, 23] or double emitter-coupled logic ( $E^2CL$ ) [24, 25, 26], in bipolar transistor implementations. The difference being that  $E^2CL$  has a second level of emitter-followers at the output of the D-latch to increase switching speed and provide additional level shifting, at the expense of increased power consumption and higher supply voltage requirements. Inductive peaking can also be introduced in the latch resistor loads to improve switching speeds however this significantly increases chip area.

The lower operational frequency limit for static dividers is usually restricted by the slew rate of the input clock signal, while the upper limit is defined by the maximum propagation delay through each of the DFFs and associated wiring. As such, static dividers typically have broader operational frequency ranges compared to dynamic topologies.

# 2.4.2 Dynamic Divider

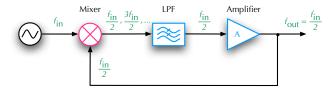

Dynamic frequency dividers on the other hand, work on the principle of regenerative frequency division shown in Figure 2.12. The design involves applying the input signal to a mixer,

Figure 2.12. System level diagram of the dynamic regenerative divider mechanism.

reproducing the fundamental signal along with a signal at half its frequency. A low-pass filter then removes the fundamental frequency while a feedback mechanism injects the half frequency signal back into the mixer. The output frequency is therefore  $f_{out} = f_{in}/2$ . The feedback loop frequency response dictates the maximum divider operating frequency, where at high frequencies the loop gain is insufficient to sustain operation. The minimum operating frequency limit occurs when the low-pass filter can no longer suppress the  $3f_{in}/2$  harmonic component [27].

Common MMIC dynamic divider implementations [28, 25] utilise double balanced active mixers such as the Gilbert cell mixer, in which case low-pass filtering and amplification are unnecessary due to the low-pass frequency response of the mixer gain.

In comparison, dynamic divider circuits are faster and consume less power than static dividers [29]. However at the more modest frequency of 24GHz compared to those reported, both static and dynamic dividers should be realisable.

### 2.4.3 Higher Order Division

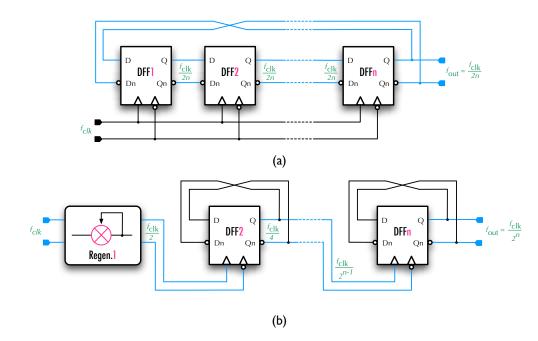

Higher order frequency division ratios can be achieved both synchronously or asynchronously.

Synchronous higher order division can only be achieved using multiple static DFF divider stages in a chain with negative feedback from the final stage to the first, as shown in Figure 2.13(a). Assuming *n*-stages, the output frequency of a synchronous divider chain is defined by the expression,

$$f_{out} = \frac{f_{clk}}{2n}.\tag{2.17}$$

Figure 2.13. Block diagram representation of (a) synchronous and (b) asynchronous divider topologies.

Each DFF stage is clocked at the high input signal frequency, placing high driving capability requirements on the input source and tight timing requirements on the DFFs and associated layout wiring delays. This also results in high power consumption compared to asynchronous designs. Propagation delays and hence clock jitter do not accumulate in synchronous dividers since the output of each DFF stage is simply a time shifted version of the divided output signal with identical frequency. The synchronous divider topology possesses similar broadband operation to the static 1/2 divider element, therefore making it suited to PLL implementation where phase noise minimisation and broad band operation are critical. Assuming however, that sufficiently fast ECL logic can be achieved with the available fabrication technology.

Asynchronous higher order division can be achieved using any combination of cascaded static or dynamic 1/2 divider stages as illustrated in Figure 2.13(b). Assuming n-stages, the output frequency of an asynchronous divider is defined by,

$$f_{out} = \frac{f_{clk}}{2^n}.$$

(2.18)

In the asynchronous configuration, each successive stage operates at half the frequency of its predecessor, relaxing the speed constraints at each stage further down the chain. This results in low power operation compared to synchronous methodologies. Essentially the performance of the first stage determines the maximum operating frequency of an asynchronous divider. Given the higher frequency and lower power consumption of dynamic dividers, a common approach is to implement the first stage dynamically and subsequent stages using dynamic

#### 2.5 SiGe Process Technology

or static divider stages [23, 30]. The main disadvantage of the asynchronous design is that timing delays and jitter accumulate with each additional stage, leading to increased phase noise on top of the input source phase noise characteristic.

# 2.5 SiGe Process Technology

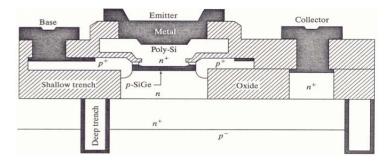

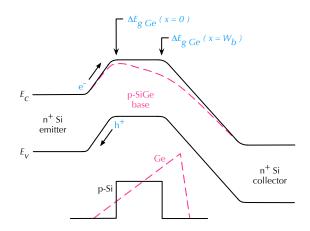

SiGe BiCMOS is a successful integration of SiGe HBTs with conventional Si CMOS to yield a technology ideal for high performance mixed signal Very Large Scale Integration (VLSI). Traditional Si homojunction BJTs use materials with the same bandgap, whereas SiGe heterojunction devices use bandgap engineering to alter the bandgap in the base region by implantation of the SiGe alloy as shown in Figure 2.14. With reference to Figure 2.15, the

**Figure 2.14.** Cross-section diagram of a typical SiGe HBT indicating the presence of Germanium in the base region to reduce the material bandgap [31].

epitaxial Germanium (Ge) concentration in the base is graded so that the bandgap is narrower at the collector than at the emitter. Tapering of the bandgap in the base induces an electric

Figure 2.15. Energy band diagram for a typical Si BJT and a graded-base SiGe HBT [32].

field that accelerates the injected electrons, thus reducing base transit times and improving

frequency response [32]. Reduction of the bandgap at the emitter-base junction also lowers the potential barrier to injection from the emitter to the base, exponentially increasing the collector current density and hence current gain. Hole injection into the base region is limited by the large potential barrier in the valence band allowing higher doping concentrations in the base. This creates higher electron mobility while maintaining gain.

# 2.5.1 IBM BiCMOS7WL

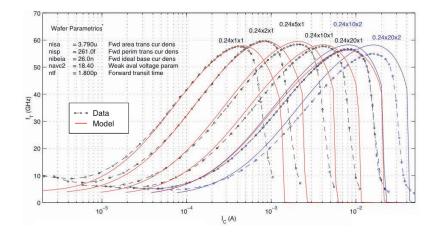

The IBM BiCMOS7WL  $0.18\mu$ m SiGe BiCMOS process with seven metal interconnect layers has been used for low volume MMIC prototyping in this thesis. Detailed technical information regarding device structure, modelling and fabrication requirements can be found in the official documentation [33, 34], however this section will give a brief overview of the features and particular device characteristics relevant to the ensuing circuit design.

# **Active Devices**

The fastest transistors offered in this technology for RF applications are the high performance NPN Si/SiGe HBT family with  $f_t = 60$ GHz. They support single and dual emitter stripe configurations with fixed emitter width  $W_e = 0.24\mu$ m and scaleable emitter length  $L_e$  to achieve the required current rating. Nominal electrical parameters for a single emitter high $f_t$  NPN transistor of size  $0.24\mu$ m ×  $4.2\mu$ m are shown in Table 2.1. Although both single

**Table 2.1.** Nominal electrical parameters of a high- $f_t$  NPN transistor of size  $0.24\mu$ m ×  $4.2\mu$ m and single emitter stripe [33].

| Electrical Parameter              | Value             | Conditions                                            |

|-----------------------------------|-------------------|-------------------------------------------------------|

| Base-emitter voltage, $V_{BE}$    | $0.737\mathrm{V}$ | $I_C = 10\mu A, V_{CB} = 0V$                          |

| Current gain, $\beta$             | 140               | $V_{BE} = 0.72 \text{V}, V_{CB} = 0 \text{V}$         |

| Peak transition frequency, $f_t$  | 60GHz             | $V_{CB} = 1$ V, $I_C = 1.65$ mA/ $\mu$ m <sup>2</sup> |

| Breakdown voltage, $BV_{CEO}$     | 3.3V              | $I_C = 10\mu A$                                       |

| Rated current density, $I_{rate}$ | $4 mA/\mu m^2$    | $W_e = 0.24 \mu m$ , single or dual                   |

and dual emitter HBT configurations are available, the dual emitter stripe option is favoured in this thesis because its lower intrinsic and extrinsic base resistance minimises the base resistance-induced thermal noise [6].

The  $f_t$  characteristics of Figure 2.16 have been used as an aid to determine HBT collector bias current for maximum frequency performance, relative to the effective emitter area. Optimal SiGe HBT device matching is achieved through symmetrical layout techniques with: devices

# 2.5 SiGe Process Technology

**Figure 2.16.** High- $f_t$  SiGe NPN  $f_t$  characteristic versus emitter area ( $V_{CB} = 1V$  and  $T = 25^{\circ}C$ ) [34]. The characteristic is used to determine transistor bias current for optimum frequency performance.

located as close as possible to each other, identical device size and orientation and similar wiring.

### **Passive Devices**

BiCMOS7WL has an extensive standard library of passive components, however only a small subset have been utilised in this thesis. Six resistor types are provided with a variety of specifications and applications. Resistor selection criteria include: sheet resistance, sensitivity or tolerance, mismatch sensitivity, parasitic capacitance and current carrying capacity. Deep trench isolation mesh underneath resistors has also been used where possible.

Single layer spiral inductors (asymmetrical and symmetrical) have been used and are formed in the thick copper top metal for high Q performance. The inductors have deep trench isolation mesh underneath to decrease spiral to substrate capacitance, lower coupling between turns and maximise self resonant frequency. Inductor reactive values are customised through the geometrical parameters of: outer diameter, number of turns, turn width and turn spacing.

The seven metal wiring layers also support Metal Insulator Metal (MIM) capacitor construction. Single MIM capacitors have a capacitance calculated according to the area capacitance of  $4.05 \text{fF}/\mu\text{m}^2$  and perimeter capacitance of  $0.14 \text{fF}/\mu\text{m}$ , as a guide.

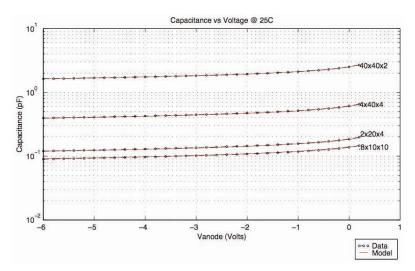

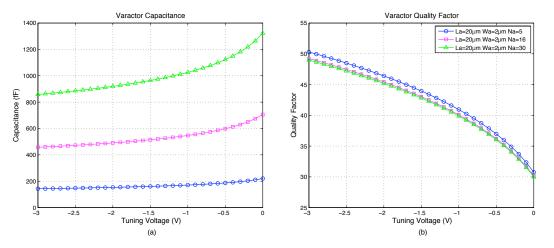

The VCO tuning elements used in this thesis are constructed from the medium- $f_t$  NPN collector-base (C-B) varactor diode. Scalability is obtained through selection of anode size and the number of anodes. Parasitic series resistance is minimised by wrap-around cathodes surrounding each varactor anode. Example varactor capacitance versus voltage characteristics

are displayed in Figure 2.17, while the nominal varactor tunability is specified as  $C_{0V}/C_{3V} = 1.36$ .

Figure 2.17. BiCMOS7WL C-B diode varactor capacitance versus voltage characteristic ( $T = 25^{\circ}C$ ), illustrating the tunable capacitance range of standard size varactors [34].

# Chapter 3

# **15GHz Oscillator Implementations**

This chapter documents the design, simulation and layout of four 15GHz single-ended VCOs in a 0.18 $\mu$ m SiGe BiCMOS technology. The VCO is intended for implementation in the 30GHz continually tunable phase shifter and active antenna beam-forming network as described in Section 1.2.1 and identified in the block diagram of Figure 3.1. The basic requirements of the circuit revision include: injection locking capability, accurate frequency synthesis, improved linear tuning range, improved insensitivity to circuit loading (i.e. better output matching) and sufficient output voltage amplitude.

Figure 3.1. Phase shifter block diagram highlighting the injection locked 15GHz VCO designed in this chapter.

# 3.1 Single-Ended VCO Topologies

There are two single-ended VCO topologies presented in this thesis – the emitter-tuned topology and the base-tuned topology. As the naming suggests, the differentiating feature of these VCOs is the physical location of the tuning mechanism with respect to transistor

#### 3.1 Single-Ended VCO Topologies

terminals. Both topologies facilitate injection locking by injecting a high quality reference oscillator signal into the output port of the VCO, as described in Section 1.2.1. The following subsections discuss each topology in detail.

# 3.1.1 Emitter-Tuned VCO Topology

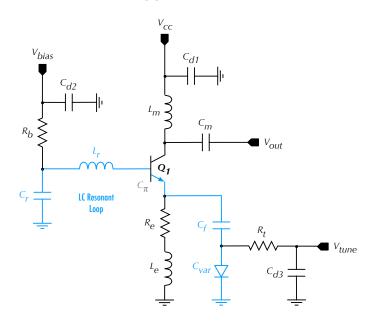

Figure 3.2 shows the Colpitts based circuit topology used in three versions of the E-tuned VCO and is based on the original work [4]. The single-ended Colpitts topology is favoured for its good phase noise performance [6]. Note that in this topology the tuning element

**Figure 3.2.** Schematic view of the single-ended Colpitts based VCO topology with varactor tuning element connected to the emitter of the transistor.

$C_{var}$  is connected via the feedback capacitor  $C_f$  to the emitter of the transistor.  $C_f$  acts to destabilise the transistor and creates negative resistance at the input port of the transistor. This negative resistance then cancels the resistance of the resonant tank comprising  $C_r$ ,  $L_r$ ,  $C_f$ ,  $C_{var}$  and the input capacitance  $C_{\pi}$  of the transistor  $Q_1$ , allowing sustained oscillation to occur. The amount of negative resistance generated can be derived by evaluating the real part of the input impedance  $(Z_a)$  looking into the base of the transistor expressed as,

$$Z_a = \frac{r_{\pi}}{(1 + w^2 r_{\pi}^2 C_{\pi}^2)} \left(1 - \frac{g_m r_{\pi} C_{\pi}}{C_e}\right)$$

(3.1)

where  $g_m$  is the transconductance of the transistor,  $r_{\pi}$  is the transistor input resistance,  $C_e$  is the series combination of  $C_f$  and  $C_{var}$ ,

$$C_e = \frac{C_f C_{var}}{C_f + C_{var}} \tag{3.2}$$

and the angular frequency  $w = 2\pi f$ . From Eq. (3.1) it can be seen that negative resistance is indeed created if,

$$\frac{g_m r_\pi C_\pi}{C_e} > 1 \tag{3.3}$$

which implies,

$$C_e < g_m r_\pi C_\pi. \tag{3.4}$$

Therefore, by simulating the amount of negative resistance at the desired transistor bias point, it is theoretically possible to determine a value for  $C_e$  to satisfy the rule of thumb for achieving an optimum power impedance match in eventual large signal steady state oscillations,

$$Z_a \approx -3 \quad Z_r \tag{3.5}$$

where  $Z_a$  is the real transistor input impedance and  $Z_r$  is the real tank loss resistance. Unfortunately, one side effect of  $C_{var}$  connected in series with  $C_f$  is that varying the effective varactor capacitance via the tuning voltage changes the destabilising effect at the emitter node and hence the negative resistance generated. Changes in the amount of negative resistance may inadvertently effect the large signal operating point of the active device.

Assuming that the emitter inductance,  $L_e$  is a high impedance at the oscillation frequency and can therefore be treated as an open circuit, an equation can be derived for the predicted oscillation frequency as,

$$f_{osc} = \frac{1}{2\pi \cdot \sqrt{L_r \left(\frac{1}{C_r} + \frac{1}{C_\pi} + \frac{1}{C_f} + \frac{1}{C_{var}}\right)^{-1}}}.$$

(3.6)

Thus, the following relationship can be used to estimate the theoretical tuning range capability of the VCO,

$$f_{\Delta} = \frac{1}{2\pi \cdot \sqrt{L_r \left(\frac{1}{C_r} + \frac{1}{C_\pi} + \frac{1}{C_f} + \frac{1}{C_{var_{min}}}\right)^{-1}}} - \frac{1}{2\pi \cdot \sqrt{L_r \left(\frac{1}{C_r} + \frac{1}{C_\pi} + \frac{1}{C_f} + \frac{1}{C_{var_{max}}}\right)^{-1}}}$$

(3.7)

where  $C_{var_{max}}$  and  $C_{var_{min}}$  are the maximum and minimum varactor capacitance bounds.

The relatively large capacitances  $C_{d1}$ ,  $C_{d2}$  and  $C_{d3}$  are decoupling or bypass capacitors to shunt unwanted power supply noise to ground. Supply impurities can cause oscillator pushing where by voltage fluctuations alter the bias point of the transistor and subsequently the frequency of oscillation. The effects of supply noise are particularly evident in a single-ended topology where common mode noise sources are not eliminated compared to a differential design.

### 3.1 Single-Ended VCO Topologies

The inductance  $L_m$  and capacitance  $C_m$  form an output matching network optimised for maximum transfer of RF power to the load.  $L_m$  also acts as a DC feed of  $V_{cc}$  to  $Q_1$ , whilst  $C_m$  couples RF signals only to the output port.

The transistor base bias voltage  $V_{bias}$  and varactor tuning voltage are applied to the circuit through resistors  $R_b$  and  $R_t$  respectively. The varactor is orientated with the cathode connected to ground to maximise Q due to the subcollector to substrate capacitance [35].

The emitter degradation resistance  $R_e$  provides DC feedback to compensate for temperature fluctuations and threshold voltage process variation. This improves the stability of the transistor DC operating point. The series inductance  $L_e$  simply acts as an AC open circuit to direct RF signals through the tuning capacitance path when under oscillating conditions.

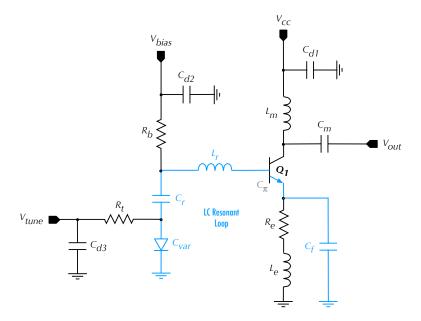

# 3.1.2 Base-Tuned VCO Topology

Figure 3.3 shows the B-tuned single-ended VCO topology as presented in [36, 6, 37] and introduced to provide a possible alternative to the E-tuned design. In this configuration

**Figure 3.3.** Schematic view of the single-ended Colpitts based VCO topology with varactor tuning element alternatively located at the base of the transistor.

the tuning capacitance  $C_{var}$  is connected to the base of the transistor via the resonant tank inductor,  $L_r$ . As such, it does not change the amount of capacitive feedback destabilisation at the emitter or the associated generation of negative resistance. The negative resistance generated by the base-tuned topology can again be derived by evaluating the real part of the transistor input impedance at the base of the transistor expressed as,

$$Z_a = \frac{r_{\pi}}{(1 + w^2 r_{\pi}^2 C_{\pi}^2)} \left(1 - \frac{g_m r_{\pi} C_{\pi}}{C_f}\right)$$

(3.8)

where  $g_m$  is the transconductance of the transistor,  $r_{\pi}$  is the transistor input resistance,  $C_{\pi}$ is the transistor input capacitance,  $C_f$  is the feedback capacitance and the angular frequency  $w = 2\pi f$ . Therefore, according to Eq. (3.8) negative resistance is achieved if,

$$\frac{g_m r_\pi C_\pi}{C_f} > 1 \tag{3.9}$$

which implies,

$$C_f < g_m r_\pi C_\pi. \tag{3.10}$$

Expressions for the oscillation frequency and tuning range defined in Eq. (3.6) and Eq. (3.7) respectively are directly applicable to the base-tuned topology because the resonant loop consists of the same series reactive elements as the E-tuned structure, despite the relocation of  $C_{var}$ .

The remaining circuit elements perform identical functions to those described for the E-tuned topology in Section 3.1.1.

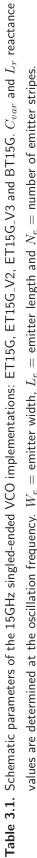

# 3.2 Biasing and Device Selection

Although the original intent of this research task was to simply port the existing VCO design and its parameters to the new technology, simulation identified certain key performance deficiencies, particularly with respect to frequency tuning capability. The tuning range proved insufficient to cover centre frequency variation from process variation. In an attempt to mitigate these deficiencies, four 15GHz VCOs were designed and prepared for fabrication. Three are parametric variations of the E-tuned topology and identified by the abbreviations: ET15G, ET15G\_V2 and ET15G\_V3 (where Vn represents the version number). The fourth VCO design is based on the B-tuned topology and is abbreviated to BT15G. The schematic device parameters of each VCO are recorded in Table 3.1 while Section 3.4 evaluates their simulated pre and post-layout performance. The focus of initial device selection was to produce oscillations at approximately 16–17GHz to allow 1–2GHz margin for the detuning effects of layout parasitics.

| Device     | Properties                                    | ET15G                        | ET15GV2                       | ET15GV3                        | BT15G                          |

|------------|-----------------------------------------------|------------------------------|-------------------------------|--------------------------------|--------------------------------|

| $Q_1$      | High- $f_t$ NPN HBT: $W_e \times L_e$ , $N_e$ | $0.24\mu m \times 4\mu m, 2$ | $0.24\mu m 	imes 2.5\mu m, 2$ | $0.24\mu m \times 2.5\mu m, 2$ | $0.24\mu m \times 2.5\mu m, 2$ |

| $C_{d1}$   | $V_{cc}$ supply decoupling                    | 8.64 pF                      | 8.64 pF                       | 7.36 pF                        | 7.36pF                         |

| $C_{d2}$   | $V_{bias}$ supply decoupling                  | 3.26 pF                      | 3.26 pF                       | 3.26 pF                        | 3.26 pF                        |

| $C_{d3}$   | $V_{tune}$ supply decoupling                  | 2.09 pF                      | 2.09 pF                       | 3.26 pF                        | 3.26 pF                        |

| $C_r$      | $V_{bias}$ DC block + RF ground               | 10.90 pF                     | 7.36 pF                       | 3.26 pF                        | 1.83 pF                        |

| $C_f$      | Instability feedback for $-R$                 | 2.22 pF                      | 812.3 fF                      | 812.3 fF                       | 455.5fF                        |

| $C_m$      | Output coupling + matching                    | 128.1 fF                     | 518.7 fF                      | 5.11 pF                        | 5.11 pF                        |

| $C_{var}$  | Tuning varactor capacitance                   | $143 fF \rightarrow 221 fF$  | 458 fF  ightarrow 706 fF      | $858fF \rightarrow 1.323pF$    | 229 fF  ightarrow 353 fF       |

| $R_b$      | Base bias voltage feed                        | $126\Omega$                  | $132\Omega$                   | $5k\Omega$                     | $2k\Omega$                     |

| $R_e$      | Temperature stabilisation                     | $106\Omega$                  | $106\Omega$                   | $16k\Omega$                    | $16k\Omega$                    |

| $R_t$      | Tuning voltage feed                           | $5k\Omega$                   | $5k\Omega$                    | $5k\Omega$                     | $5k\Omega$                     |

| $L_r$      | Resonant tank inductance                      | 1.076nH                      | 910pH                         | 704pH                          | 910pH                          |

| $L_m$      | $V_{cc}$ feed + output matching               | 882pH                        | 1.07 nH                       | 4.99nH                         | 4.99nH                         |

| $L_e$      | RF high impedance choke                       | 1.027 nH                     | 1.027 nH                      | 4.99nH                         | 4.99nH                         |

| $V_{bias}$ | Base bias voltage                             | +1V                          | +1.1V                         | +1V                            | +1V                            |

| $V_{cc}$   | Supply rail voltage                           | +1.8V                        | +1.8V                         | +1.8V                          | +1.8V                          |

| $V_{tune}$ | $C_{var}$ tuning voltage                      | -3V  ightarrow 0V            | -3  ightarrow 0V              | -3V  ightarrow 0V              | $-3V \rightarrow 0V$           |

Two variants of the high- $f_t$  SiGe NPN HBT were selected from the technology device library for  $Q_1$ , with emitter dimensions as shown in the schematic parameters Table 3.1. The smaller transistor should have a reduced capacitive contribution to the resonant loop. The subsequent collector bias currents for maximum  $f_t$  performance were determined with reference to the  $f_t$  characteristics presented in the technology design manual and shown in Figure 2.16. The voltages  $V_{cc}$  and  $V_{bias}$  are used to achieve the desired bias point of the core transistor. Given a supply voltage of 1.8V and transistor  $V_{BE} \approx 0.737$ V,  $V_{bias}$  is set in the order of 1V to provide adequate headroom under large signal oscillation without driving  $Q_1$  into the non-linear saturation region. Saturation of the active device in a single-ended topology may result in sinusoidal asymmetries in the output waveform and hence spectral impurity. A base-collector varactor diode forms the tuning element,  $C_{var}$  in both VCO topologies. The varactor cathode is at AC ground potential to maximise Q. The emitter-base junction breakdown voltage limits the varactor tuning voltage to the range,  $-3V \leq V_{tune} \leq 0$ V.

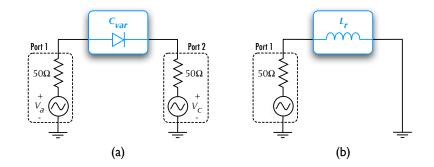

# **3.2.1** $C_{var}$ and $L_r$ Characterisation

Characterisation of varactor and inductor properties was undertaken to determine the capacitive tuning range of varactor configurations as a function of reverse bias potential and the inductance, Q and series loss resistance of resonant tank inductor configurations as a function of frequency. Figure 3.4(a) shows the two-port schematic used to perform Scattering parameter (S-parameter) simulation on varactor configurations, where the reverse bias tuning voltage is the difference between anode and cathode DC potentials ( $V_a$  and  $V_c$ ) defined in the port properties. Individual parametric analysis on the reverse bias voltage and input

Figure 3.4. S-parameter schematics used to characterise the reactance, Q and series resistance of varactor and inductor configurations.

signal frequency produce capacitance and Q characteristics according to the expressions,

$$C(V_{ac}) = \frac{Y_{11}}{2\pi f}$$

(3.11)

$$Q(V_{ac}) = \frac{Y_{11}}{Y_{11}} \tag{3.12}$$

where  $Y_{11}$  and  $Y_{11}$  are the real and imaginary parts of the Y-parameter,  $Y_{11}$  of Port 1 respectively. Parametric simulation of the inductor circuit shown in Figure 3.4(b) with respect to input signal frequency produces inductance, loss resistance and Q characteristics according to the expressions,

$$L = \frac{Z_{11}}{2\pi f} \tag{3.13}$$

$$Q = \frac{Z_{11}}{Z_{11}}$$

(3.14)

$$R = Z_{11}$$

(3.15)

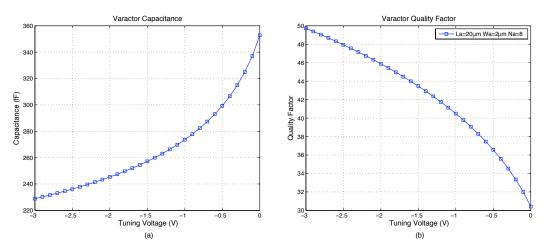

where  $Z_{11}$  and  $Z_{11}$  are the real and imaginary parts of the Z-parameter,  $Z_{11}$  of Port 1 respectively. The chosen varactors have standard anode size  $L_a \times W_a = 20 \mu \text{m} \times 2 \mu \text{m}$  and operate in reverse bias mode. The number of varactor anodes,  $N_a$  is selected in conjunction with the tank inductance  $L_r$  through a process of iterative simulation, to achieve the 15GHz oscillation frequency requirement.  $N_a$  in the four VCO designs ranges from 5 to 30 and their simulated capacitance and quality factor characteristic graphs are shown in Figure 3.5. The characteristics indicate that irrespective of the varactor size, the capacitive tuning ratio

Figure 3.5. S-parameter simulation of varactor: (a) capacitance and (b) quality factor at 15GHz as a function of applied reverse bias potential,  $V_{ac}$ .  $L_a$  = varactor anode length,  $W_a$  = anode width and  $N_a$  = number of anodes.

remains constant at  $C_{V_{ac}=-3V}$  :  $C_{V_{ac}=0V} = 1$  : 1.54. Therefore, increasing varactor size

alone is not an effective means of increasing VCO frequency tuning capability, instead only the median capacitance is increased. The varactor quality factor characteristic illustrates a significant roll-off as  $V_{tune}$  approaches zero volts. This ultimately indicates a large variation of the energy restoration capability of the resonant loop during tuning.

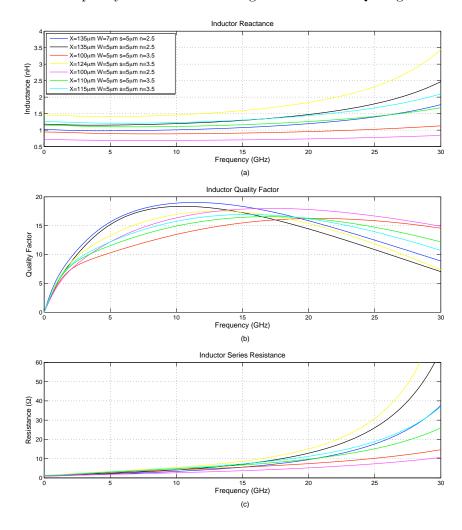

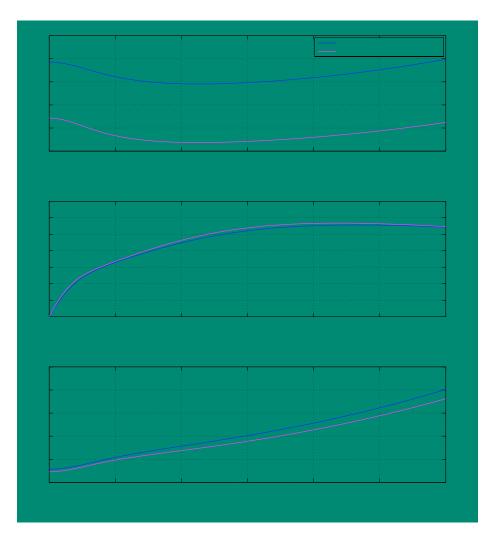

$L_r$  is a standard top metal spiral inductor over a crosshatch pattern of deep trench isolation, which creates a barrier of insulator material, effectively cutting up the conductivity of the substrate near the surface [33]. Figure 3.6 shows the inductance, quality factor and series resistance characteristics of the devices used in each of the single-ended 15GHz VCO designs as a function of frequency. It is worth noting that inductor Q ranges from 15 to 18 at

Figure 3.6. S-parameter simulation of 15GHz VCO resonant tank inductor: (a) inductance, (b) Q and (c) series loss resistance, as a function of frequency. X =spiral outer diameter, W =spiral width, s = turn separation and n = number of turns.

15GHz and peaks in the vicinity of the operational frequency. Series resistance increases

#### 3.3 Circuit Layout

exponentially as frequency increases, however it is generally less than  $9\Omega$  at 15GHz. A high Q resonant tank is typically more difficult to tune with the necessary precision, however it leads to better selectivity. In the phase shifter application, a low VCO Q is desirable because it promotes a wide locking range to the external injected reference signal [38]. Although the low VCO Q results in poor phase noise, during lock the oscillator will adopt the phase noise characteristic of the injected high purity reference oscillator.

Sufficiently large values are selected for the decoupling capacitors  $C_{d1}$ ,  $C_{d2}$  and  $C_{d3}$  to provide adequate isolation of unwanted AC noise superimposed on the DC power supply lines.

While the remaining passive components of ET15G are an adaptation of the original work, ET15G\_V2 is a minor optimisation of these components focussing on improving frequency tunability by reducing the feedback capacitor,  $C_f$  to allow for increased varactor size. BT15G and ET15G\_V3 however, are more extensive redesigns. Whilst still concerned with maximising tuning range, they attempt to improve bias voltage isolation, temperature stability and RF blocking in the emitter degradation path via increasing the values of components  $R_b$ ,  $R_e$  and  $L_e$  respectively. Impedance matching analysis was performed to improve the output match of  $L_m$  and  $C_m$  for maximum linearity and signal transmission. However, interdependencies between the matching network and centre oscillation frequency make this difficult. The redesigned circuits exhibited sufficient negative resistance to sustain oscillation at above 40GHz, albeit with small output amplitude.

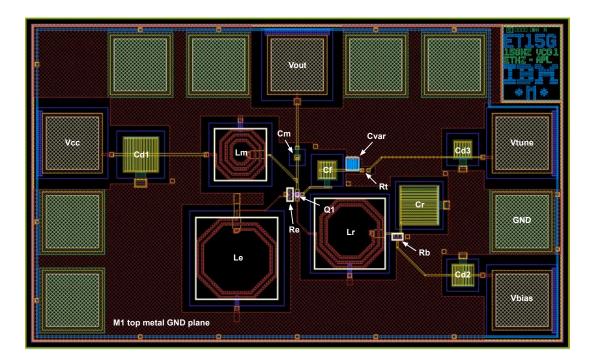

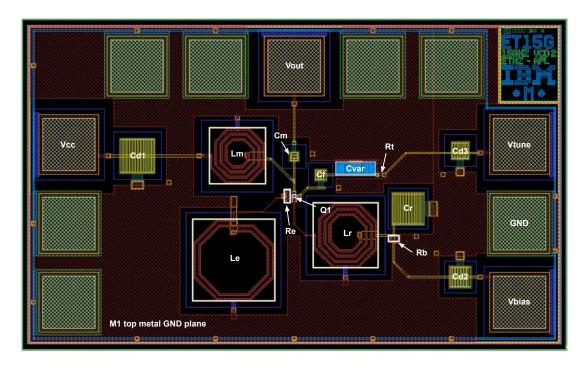

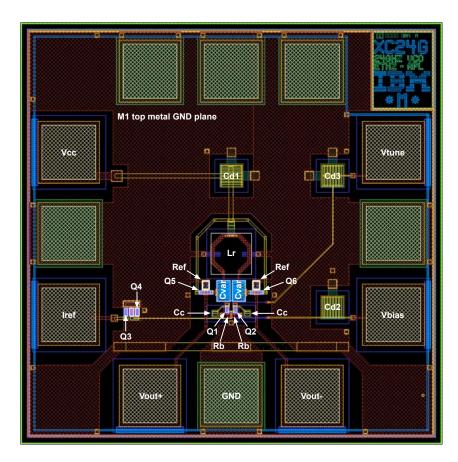

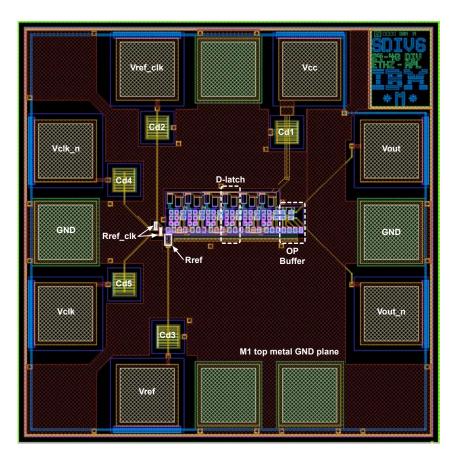

## 3.3 Circuit Layout

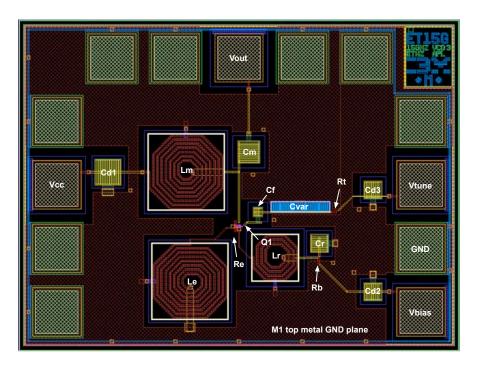

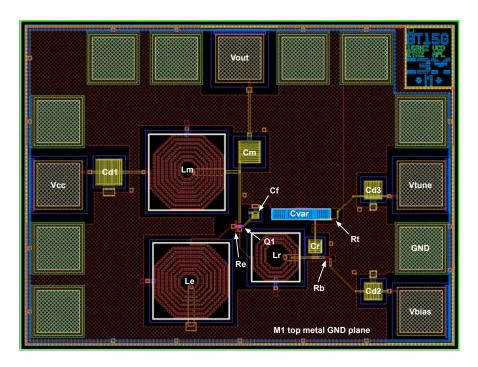

Industry standard RF layout techniques were employed in the generation of the four 15GHz single-ended VCO layouts shown in Figures 3.7, 3.8, 3.9 and 3.10. Compact device placement and minimisation of parasitics were of particular focus. A top metal ground plane is incorporated in each layout to ensure a low resistance, common ground path, reduced metal layer to substrate parasitic effects and to shield against RF signal cross-coupling. All inductors and bond pads utilise deep trench isolation to break up the conductivity in the substrate surface and reduce coupled noise in the VCO output. Bond pads are placed at minimum pitch around the perimeter of each VCO core, the size of which is dominated by the passive inductive and capacitive components. The size and pitch of bond pads is dictated by the mechanical constraints of the wafer measurement probes. Encompassing chip rings and the necessary metal density fill for fabrication, complete the layout process. ET15G are slightly larger at 1038 $\mu$ m × 780 $\mu$ m to accommodate increased  $L_m$  and  $L_e$  inductor size.

Figure 3.7. ET15G 15GHz single-ended E-tuned VCO layout cell view with annotated device labels – chip size  $1038\mu m \times 630\mu m$ .

Figure 3.8. ET15G\_V2 15GHz single-ended E-tuned VCO layout cell view with annotated device labels – chip size  $1038 \mu m \times 630 \mu m$ .

**Figure 3.9.** ET15G\_V3 15GHz single-ended E-tuned VCO layout cell view with annotated device labels – chip size  $1038\mu m \times 780\mu m$ .

Figure 3.10. BT15G 15GHz single-ended B-tuned VCO layout cell view with annotated device labels – chip size  $1038\mu m \times 780\mu m$ .

### 3.3.1 Layout Parasitic Extraction

Analog parasitic resistance and capacitance were extracted from the VCO layouts (including metal density fill) using the design tools, with the values back-annotated into the circuit schematics. Unfortunately, the design kit did not allow extraction of parasitic inductance, therefore, some discrepancy is expected between simulated and measured performance. Post-layout simulations were performed on the extracted schematics and appear in Section 3.4 in conjunction with pre-layout simulation results for comparison.

The results triggered minor schematic modifications with respect to resonant tank inductor  $(L_r)$  properties, to fine tune the expected oscillation frequencies. Table 3.2 summarises the modifications while the inductance, quality factor and series resistance characteristics of the new devices are included in Figure 3.6. All pre and post-layout simulated VCO results reported in this chapter incorporate these  $L_r$  instance changes.

| MMIC     | Version  | Dimensions                            | $L_r$  | R          | Q     | $f_{peak Q}$ |

|----------|----------|---------------------------------------|--------|------------|-------|--------------|

|          |          |                                       | (nH)   | $(\Omega)$ |       | (GHz)        |

| ET15G    | Original | $135 \mu m \times 7 \mu m \times 2.5$ | 1.076  | 5.53       | 18.33 | 9.85         |

| EIIG     | Updated  | $135 \mu m \times 5 \mu m \times 2.5$ | 1.295  | 7.15       | 17.26 | 9.58         |

| ET15G_V2 | Original | $100\mu m \times 5\mu m \times 3.5$   | 0.9101 | 5.54       | 15.48 | 11.83        |

| E113G_V2 | Updated  | $124 \mu m \times 5 \mu m \times 3.5$ | 1.591  | 8.65       | 17.33 | 8.42         |

| ET15G_V3 | Original | $100\mu m \times 5\mu m \times 2.5$   | 0.7044 | 3.72       | 17.86 | 14.17        |

| E110G_V3 | Updated  | $110 \mu m \times 5 \mu m \times 3.5$ | 1.164  | 6.671      | 16.44 | 10.13        |

| BT15G    | Original | $100\mu m \times 5\mu m \times 3.5$   | 0.9101 | 5.54       | 15.48 | 11.83        |

| DI 10G   | Updated  | $115 \mu m \times 5 \mu m \times 3.5$ | 1.305  | 7.27       | 16.93 | 9.44         |

**Table 3.2.**  $L_r$  schematic modifications resulting from post-layout simulations, to fine tune each VCOfundamental frequency. The original and updated device attributes are included.

## 3.4 Simulation Results

Simulation of the single-ended VCO implementations was carried out in accordance with the large and small signal oscillator analysis as described in [39]. The basic premise of this procedure is that small signal simulation quickly identifies a satisfactory circuit topology in the early design phase, while large signal analysis focuses on accurate design of the oscillator and its associated parameters for reliable performance. Using S-parameter analysis to obtain the reflection coefficients and resulting impedances at the interface between the active device and the resonator (the plane between  $L_r$  and  $Q_1$  in Figure 3.2 and Figure 3.3), the simulation tools can be set up to directly plot the real ( ) and imaginary ( ) impedance relationships,

$$\frac{Z_a(A,\omega)}{Z_r(\omega)} \tag{3.16}$$

$$Z_a(A,\omega) + Z_r(\omega) \tag{3.17}$$

where  $Z_a$  is the frequency ( $\omega$ ) and oscillation amplitude (A) dependent impedance looking into the active circuit network and  $Z_r$  is the frequency dependent input impedance looking into the resonant circuit network. The predicted small signal oscillation frequency can be read from the graph at the point where the conditions for stable oscillation are met for negative resistance oscillators, in accordance with Eq. (2.5) and Eq. (3.5). Whilst these conditions are mandatory to achieve oscillation, [40] derives an equation representing the correlation between a differential change in the circuit impedance and variations in the operating point amplitude as,

$$\left[\frac{\partial R_a(A)}{\partial A}\right]_{A=A_0} \cdot \left[\frac{\partial X_r(\omega)}{\partial \omega}\right]_{\omega=\omega_{LO}} - \left[\frac{\partial R_r(\omega)}{\partial \omega}\right]_{\omega=\omega_{LO}} \cdot \left[\frac{\partial X_a(A)}{\partial A}\right]_{A=A_0} > 0.$$

(3.18)

Properties of the active and passive loads allow simplification of Eq. (3.18) to the following form,

$$\left[\frac{\partial X_r(\omega)}{\partial \omega}\right]_{\omega=\omega_{LO}} > 0 \tag{3.19}$$

stipulating that to guarantee stable oscillation, the reactive component of the  $Z_r$  impedance must also be increasing with frequency about the operating point. Simulation verified that this condition is automatically satisfied by the passive resonant networks of each VCO.

Transient and periodic steady-state (PSS) simulation techniques were utilised to accurately model VCO output and tuning characteristics under large signal operating conditions, after start-up. A component of the PSS simulation was also used to evaluate single-sided VCO phase noise characteristics relative to the fundamental oscillation frequency.

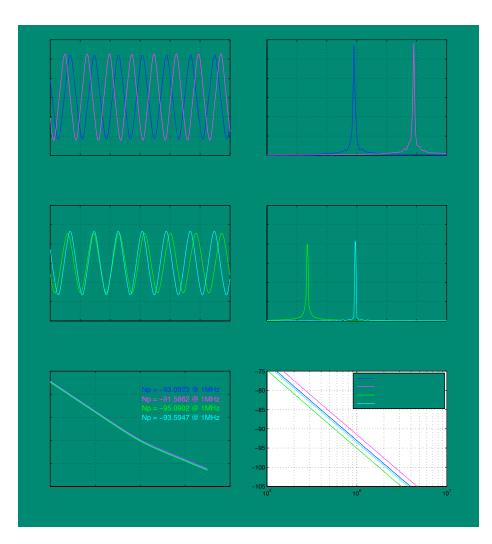

### 3.4.1 VCO Output and Phase Noise

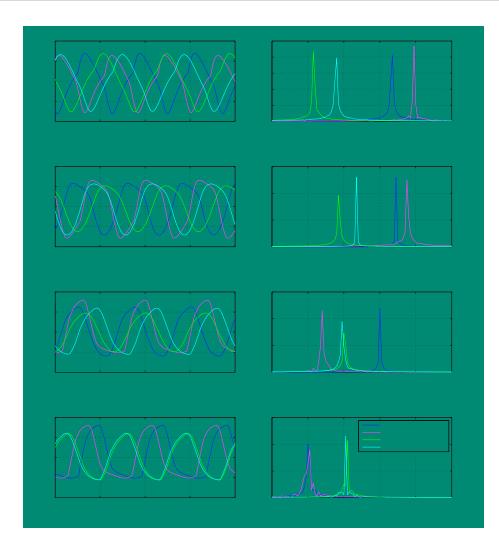

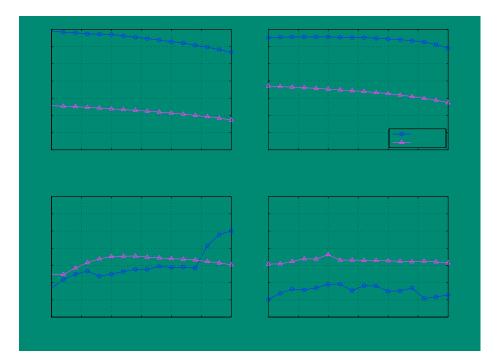

Time domain waveforms of each VCO output were obtained using transient simulation of the single-ended output voltage signals at the tuning voltage limits,  $V_{tune} = -3V$  and 0V. A load impedance of 50 $\Omega$  is assumed and represents the input impedance of a matched succeeding circuit connection. The results are shown in Figure 3.11, and represent constant amplitude sinusoids. Post-layout waveforms closely follow the shape of the pre-layout predictions, while ET15G\_V3 and BT15G appear to suffer more voltage amplitude degradation. ET15G demonstrates approximately double the amplitude compared to the other VCOs. This can be attributed to the increased current capacity of the larger transistor used in its design.

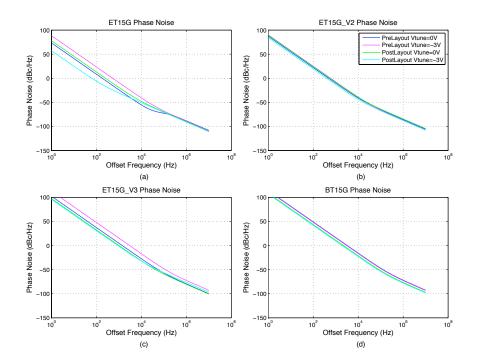

Figure 3.11. Simulated pre-layout schematic and post-layout analog extracted 15GHz VCO output signals at the tuning voltage limits,  $V_{tune} = -3V$  and 0V, in the time and frequency domain: (a) & (b) ET15G, (c) & (d) ET15G\_V2, (e) & (f) ET15G\_V3, and (g) & (h) BT15G.

The frequency domain plots shown in Figure 3.11 were generated using a windowed Fast Fourier Transform (FFT) function on each output voltage signal and reveal upper and lower oscillation frequency bounds. The frequency spectrum are also extremely useful in demonstrating the sensitivity of VCO resonant frequency to layout parasitics. Although the frequency tuning range of ET15G is relatively unaffected by circuit layout, the centre frequency has shifted down by approximately 2GHz. ET15G\_V2 suffers a similar downward shift of the centre frequency by approximately 1.5GHz after layout, however the tuning range has actually slightly increased according to the simulations. ET15G\_V3 is somewhat of an anomaly. While pre-layout results predict that it has the largest tuning range of all the VCO designs, post-layout results show that only roughly a third of the range centred around 15GHz is

#### 3.4 Simulation Results