# CIRCUIT-BASED MONITORING OF HIGH-PERFORMANCE SEMICONDUCTOR MANUFACTURING PROCESSES

By

Evgeny Kuxa

A THESIS SUBMITTED TO MACQUARIE UNIVERSITY

for the degree of

Doctor of Philosophy

Department of Engineering

June 2015

## Abstract

The conventional process control of semiconductor manufacturing is done by testing the electrical properties of the structures and devices which comprise the process control monitor, or PCM. Being useful at spotting process fluctuations over long periods of time, the PCM poorly predicts the nonlinear behaviour of the real circuits. This means that good PCM measurement results do not guarantee the expected performance of the functional circuits.

An augmented PCM is proposed which uses a simple circuit to relate process variation to nonlinear circuit performance. The suggested circuit control monitor, or CCM, is a nonlinear circuit whose signals can be related to the state of the manufacturing process. It is expected that the correlation between the CCMs' and functional nonlinear circuits' performance would be stronger.

A chaotic Chua's oscillator-based CCM is designed. It is implemented using the GaAs pHEMT manufacturing process which required developing a new version of the circuit's nonlinear element. The circuit equations suggested that the individual oscillator signals contain the features in the form of equilibrium levels which can indicate the state of the process. A computer algorithm is implemented as an analysis tool to retrieve the chaotic features of the measured circuit data. It is found that equilibrium levels fluctuate across the wafer and are closely correlated with both, the PCM parameters and the nonlinear parameters of the functional circuits. Overall, the results are regarded as satisfactory and the viability of the CCM approach is demonstrated.

iv

# Acknowledgements

I would like to acknowledge the great help I have received from my academic supervisors Michael Heimlich and Anthony Parker. I would like to thank people from Sydney's Macom design office, namely Simon Mahon, Anna Dadello, Tony Fattorini, Gerry McCulloch and others who assisted me with mastering circuit design and layout, and also measurements. Furthermore, without the contribution of WIN Semiconductors employees Wen-Kai Wang and Richard Kuo, this project would not have been implemented at all.

In addition I would like to thank all the engineering students and research fellows in our department, especially Oya Sevimli, Forest Zhu and Ayobami Iji for their support and guidance. Administration staff for dealing with all the organisation problems quickly and efficiently, thus making my research life a smooth sailing.

Last but not least I would like to express my gratitude to Macquarie University and Australian Research Council for providing me the opportunity to carry out this absorbing and challenging research, present at conferences and experience the life in Australia altogether.

Dr Keith Imrie, former Senior Lecturer in Electronics, provided copyediting and proofreading services, according to the guidelines laid out in the University-endorsed national 'Guidelines for editing research theses'.

# Statement of Originality

The project was completed at Macquarie University between December 2011 and December 2014.

The original circuit-based monitoring concept was proposed jointly by Macom Tech. Solutions and WIN Semiconductors.

The Matlab code of Chua's circuit mathematical model included parts developed by V. Sidersky. The code for bifurcation diagram was developed by M. Audet. The remaining Matlab algorithms were developed by the author.

The operational-amplifier-based Chua's circuit schematic for board-level implementation was taken from V. Sidersky's website. The second board-level concept was suggested by the author.

The GaAs pHEMT Chua's circuit implementation was developed by the author employing the saturated-buffer FET logic patented by A.E. Parker and D.J. Skellern. The circuit layouts were developed with the assistance of Macom Sydney Design Centre's employees A. Dadello and A.P. Fattorini. Advice on the layout design was also received from Dr F. Zhu, at time Department of Electronics research fellow.

The integrated circuits were manufactured on WIN Semiconductor foundry, Taiwan. Assistance with interpreting the PCM data was given by R. Kuo.

On-wafer measurements of the designed circuits were prepared with the assistance of Dr O. Sevimli, at time Department of Electronics research fellow and G. McCulloch from Macom. Measurements were performed by the author.

The work of others is acknowledged and referenced, except in cases where the results

are widely known.

This work has not been submitted in whole or part towards another degree at Macquarie University or any other university.

| Evgeny Kuxa |  |

|-------------|--|

|             |  |

## List of Publications

- E. Kuxa, A. E. Parker, S. J. Mahon, A. Dadello, W.-K. Wang, M. C. Heimlich, Process control in GaAs manufacturing using Chuas circuit. CS MANTECH Conference, May 2014

- E. Kuxa, A. E. Parker, S. J. Mahon, A. P. Fattorini, W.-K. Wang, R. Kuo, M. C. Heimlich, *Chua's Chaotic Oscillator as the GaAs Manufacturing Process State Indicator*. APMC 2014, November 2014

# List of Acronyms

PCM: process control monitor

CCM: circuit control monitor

pHEMT: pseudomorphic high electron mobility transistor

FET: field effect transistor

LNA: low-noise amplifier

RF: radio frequency

MMIC: monolithic microwave integrated circuit

MESFET: metal-semiconductor FET

PECVD: plasma-enhanced chemical vapour deposition

CPW: coplanar waveguide

RFIC: radio frequency integrated circuit

EM: electromagnetic

HBT: heterojunction bipolar transistor

VSAT: very small aperture terminal

CATV: cable television

BJT: bipolar junction transistor

MBE: molecular beam epitaxy

MOCVD: metal-organic chemical vapour deposition

2-DEG: two-dimensional electron gas

SPC: statistical process control

UCL: upper control limit

LIST OF ACRONYMS

LCL: lower control limit

MOSFET: metal-oxide-semiconductor FET

DC: direct current

NR: nonlinear resistor

CAD: computer aided design

SPICE: simulation program with integrated circuit emphasis

FFT: fast Fourier transform

NMOS: n-type MOSFET

PMOS: p-type MOSFET

PCB: printed circuit board

PDK: process design kit

TFR: thin-film resistor

MIM: metal-insulator-metal

LVS: layout versus schematic

DRC: design rules check

UGW: unit gate width

NOF: number of fingers

PC: personal computer

PDF: probability distribution function

P1dB: 1 dB compression point

# Contents

| $\mathbf{A}$ | bstra | ct                                          |

|--------------|-------|---------------------------------------------|

| $\mathbf{A}$ | ckno  | wledgements                                 |

| St           | aten  | nent of Originality vii                     |

| Li           | st of | Publications ix                             |

| Li           | st of | Acronyms xi                                 |

| Li           | st of | Figures xvii                                |

| Li           | st of | Tables xxiii                                |

| 1            | Intr  | roduction 1                                 |

|              | 1.1   | Motivation                                  |

|              | 1.2   | Synopsis                                    |

|              | 1.3   | Scope of the Work                           |

| <b>2</b>     | Ove   | erview 7                                    |

|              | 2.1   | Gallium Arsenide Manufacturing              |

|              |       | 2.1.1 pHEMT Manufacturing Process           |

|              | 2.2   | Semiconductor Manufacturing Process Control |

|              | 2.3   | Circuit Control Monitor                     |

XiV

|   | 2.4  | Chaos Theory                       | 2 |

|---|------|------------------------------------|---|

|   | 2.5  | Chua's Circuit                     | 4 |

| 3 | Chu  | a's Circuit Analysis 4             | 5 |

|   | 3.1  | Mathematical Properties            | 5 |

|   |      | 3.1.1 Circuit Equations            | 6 |

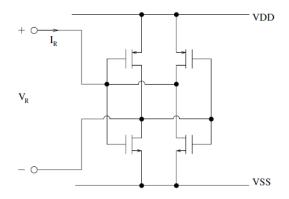

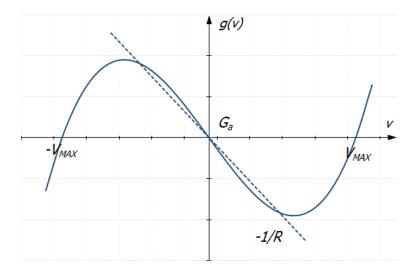

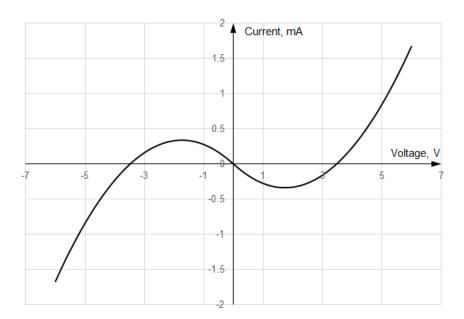

|   |      | 3.1.2 Nonlinear Resistor           | 8 |

|   |      | 3.1.3 Equilibrium Points           | 9 |

|   | 3.2  | Loading Effects                    | 1 |

| 4 | Chu  | a's Circuit Prototyping 5          | 3 |

|   | 4.1  | Matlab Simulations                 | 3 |

|   |      | 4.1.1 Piecewise Nonlinearity       | 4 |

|   |      | 4.1.2 Smooth nonlinearity          | 9 |

|   | 4.2  | CAD Circuit Simulations            | 4 |

|   | 4.3  | Analysis of the Circuit's Signals  | 0 |

|   | 4.4  | Circuit Sensitivity                | 5 |

|   | 4.5  | Board-level CCM Concept            | 1 |

|   | 4.6  | Conclusions                        | 6 |

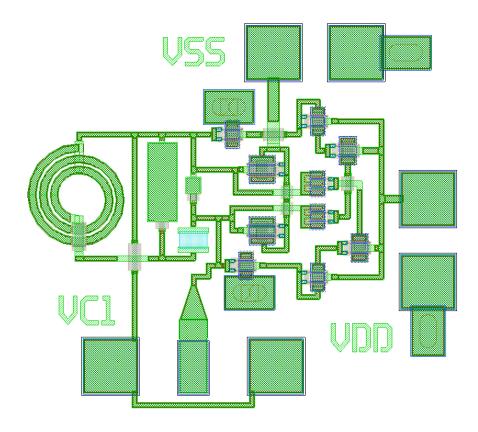

| 5 | Inte | grated-Circuit Design of the CCM 8 | 7 |

|   | 5.1  | Manufacturing Processes Overview   | 8 |

|   |      | 5.1.1 PP-10 GaAs pHEMT Process     | 8 |

|   |      | 5.1.2 PL-15 GaAs pHEMT Process     | 8 |

|   | 5.2  | Circuit Design                     | 0 |

|   |      | 5.2.1 Nonlinear Resistor           | 0 |

|   |      | 5.2.2 Resonator Design             | 5 |

|   |      | 5.2.3 Circuit Layout               | 8 |

|   | 5.3  | Conclusions                        | 7 |

| 6 | CC   | I Testing 10                       | 9 |

|   | 6.1  | PP-10 Measurements                 | g |

Contents

|              | 6.2    | PL-15 Measurements                     | 117 |

|--------------|--------|----------------------------------------|-----|

|              | 6.3    | Conclusions                            | 126 |

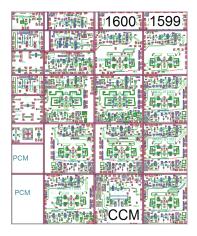

| 7            | CC     | M correlation with PCM                 | 127 |

|              | 7.1    | Measurement Setup                      | 128 |

|              | 7.2    | Correlation Results                    | 131 |

|              | 7.3    | Variations in Correlation              | 136 |

|              | 7.4    | Conclusions                            | 139 |

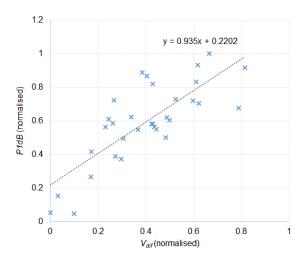

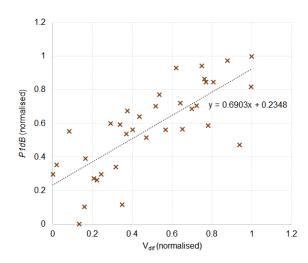

| 8            | CC     | M and Nonlinear Circuits               | 141 |

|              | 8.1    | Nonlinear Circuits Measurements        | 142 |

|              | 8.2    | Correlation Results                    | 146 |

|              | 8.3    | Conclusions                            | 154 |

| 9            | Con    | aclusions                              | 157 |

|              | 9.1    | Work Scope                             | 157 |

|              |        | 9.1.1 Project Summary                  | 158 |

|              | 9.2    | Suggested Improvements and Future Work | 161 |

| $\mathbf{A}$ | App    | pendix A: Matlab program listings      | 167 |

| Re           | efere: | nces                                   | 185 |

Contents

# List of Figures

| 2.1  | GaAs pseudomorphic HEMT [1]                                                      | 9  |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | Thin strained superlattice pseudomorphic active layer structure $[1]$            | 10 |

| 2.3  | The 0.15 $\mu m$ optical-gate pHEMT device [2]                                   | 10 |

| 2.4  | Scanning electron microscope cross-section of the 0.15 $\mu m$ optical gate [2]. | 11 |

| 2.5  | Typical control chart                                                            | 13 |

| 2.6  | Two types of pendulums                                                           | 25 |

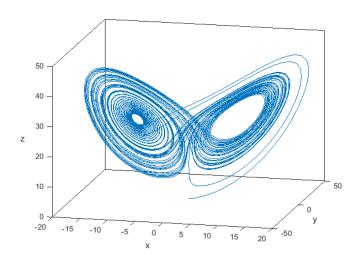

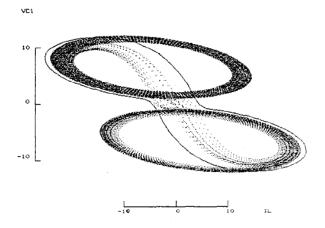

| 2.7  | Matlab-generated Lorenz's two-lobed attractor                                    | 26 |

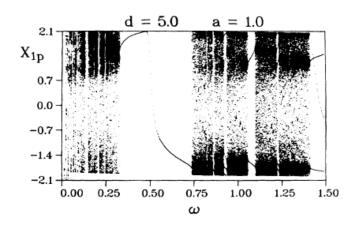

| 2.8  | Bifurcation diagram showing coordinate $X_{1p}$ of the attractor in the          |    |

|      | Poincaré cross section versus the excitation frequency $\omega$ [3]              | 29 |

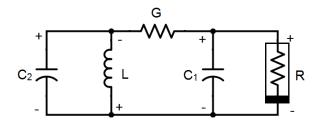

| 2.9  | Chua's circuit schematic diagram                                                 | 35 |

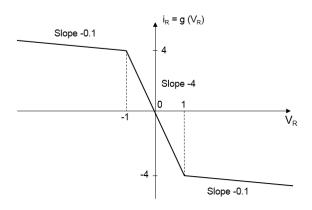

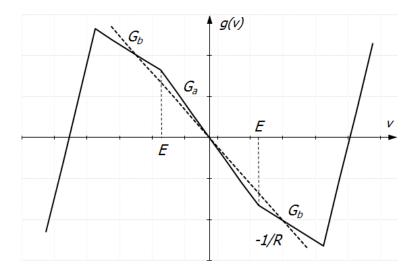

| 2.10 | Nonlinear resistor's current-voltage function [4]                                | 36 |

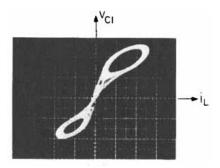

| 2.11 | $(i_L, v_{C_1})$ -plane of the chaotic attractor [4]                             | 36 |

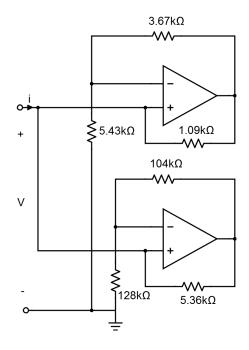

| 2.12 | The circuit designed by Zhong and Ayrom [5]                                      | 37 |

| 2.13 | Operational-amplifier nonlinear resistor realisation $[5]$                       | 37 |

| 2.14 | The chaotic attractor observed by Zhong and Ayrom [5]                            | 38 |

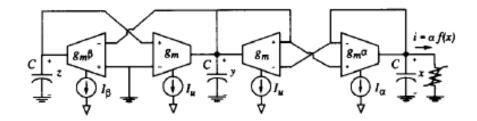

| 2.15 | Conceptual transconductance amplifier Chua's circuit [6]                         | 38 |

| 2.16 | CMOS schematics for the transconductance amplifiers (left) and CMOS              |    |

|      | Chua's diode (right) [6]                                                         | 39 |

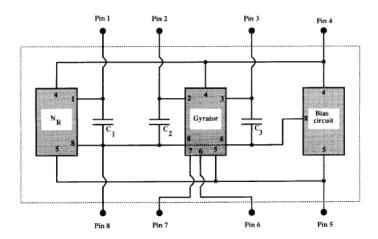

| 2.17 | Network schematics of the CMOS IC Chua's circuit including the bias [7].         | 39 |

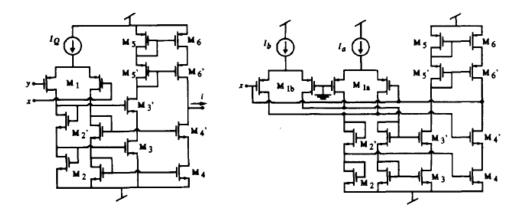

| 2.18 | Four-transistor cubic-like Chua's diode [8]                                      | 40 |

| 2.19 | Variable cubic-like Chua's nonlinear resistor [9]                                | 40 |

xviii List of Figures

| 2.20 | Implementation of Chua's circuit with a biased tunnel diode [10]           | 41 |

|------|----------------------------------------------------------------------------|----|

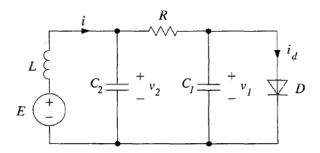

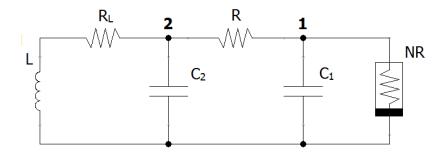

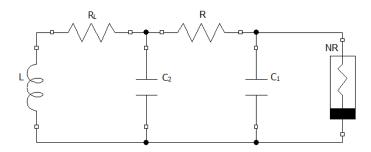

| 3.1  | Chua's circuit schematic diagram                                           | 46 |

| 3.2  | Piecewise-linear current-voltage characteristic of the NR (solid) and load |    |

|      | line (dashed)                                                              | 49 |

| 3.3  | Cubic-like current-voltage characteristic of the NR (solid) and load line  |    |

|      | $(dashed). \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                          | 50 |

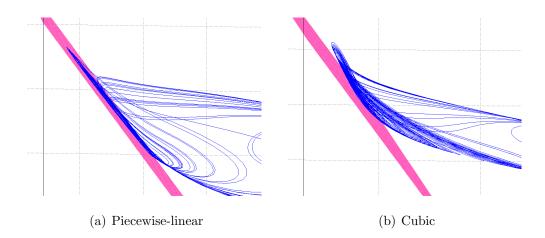

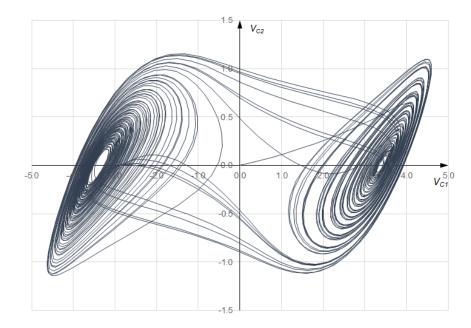

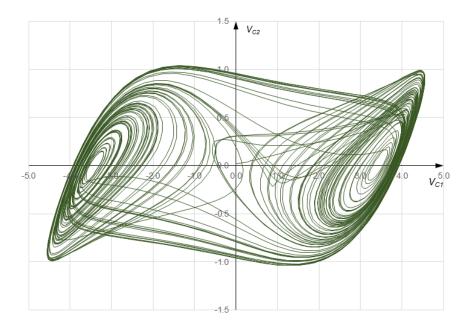

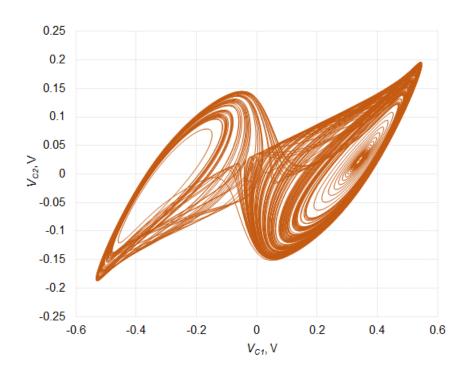

| 4.1  | The geometry of the chaotic attractor from a circuit with piecewise non-   |    |

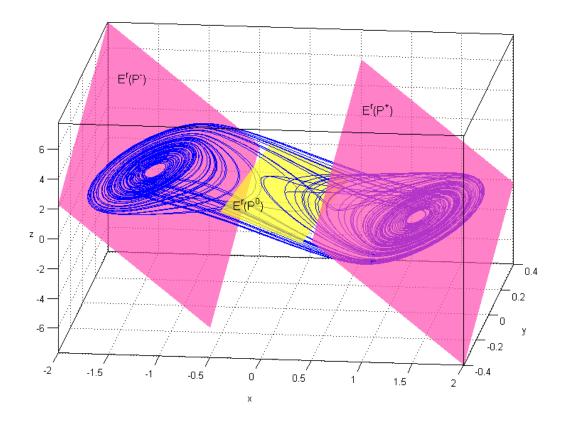

|      | linearity                                                                  | 57 |

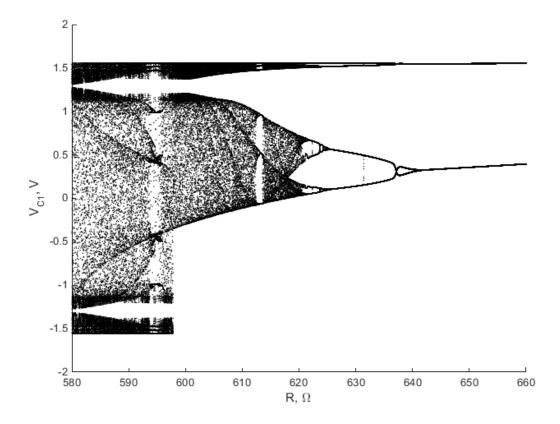

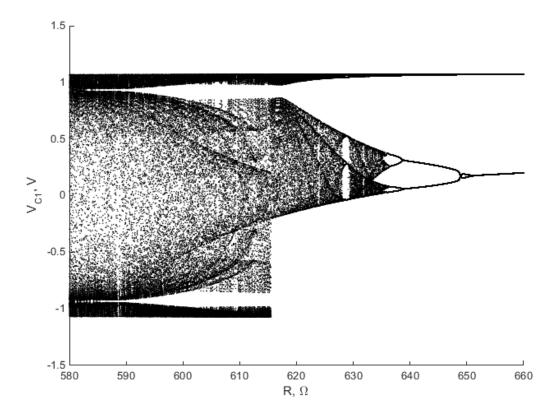

| 4.2  | The bifurcation diagram of the circuit with piecewise-linear nonlinearity  |    |

|      | generated by Matlab algorithm                                              | 58 |

| 4.3  | The geometry of the chaotic attractor from a circuit with cubic nonlin-    |    |

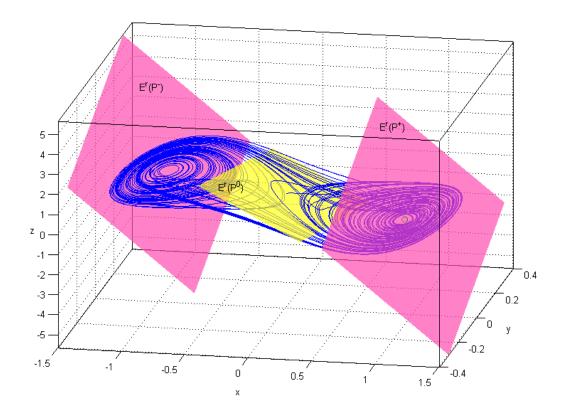

|      | earity                                                                     | 61 |

| 4.4  | Zoom in on the $P^-$ equilibrium point for the two attractors              | 62 |

| 4.5  | The bifurcation diagram of the circuit with piecewise-linear nonlinearity  |    |

|      | generated by Matlab algorithm                                              | 63 |

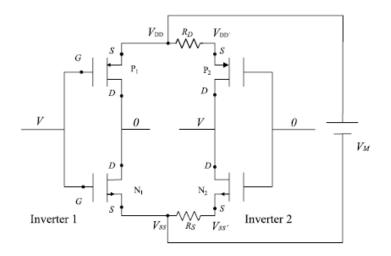

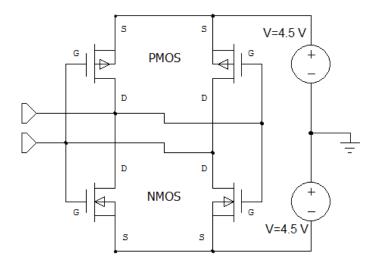

| 4.6  | Nonlinear element with two cross-coupled CMOS inverters as simulated       |    |

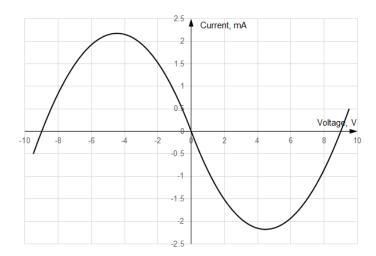

|      | in AWR                                                                     | 65 |

| 4.7  | Current-voltage characteristic of the MOSFET nonlinear element             | 66 |

| 4.8  | AWR schematic of the designed MOSFET Chua's circuit                        | 66 |

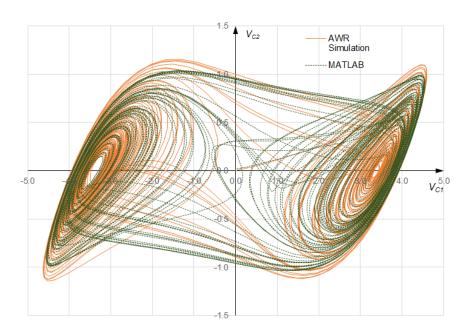

| 4.9  | Attractor for CMOS circuit generated from AWR simulation                   | 67 |

| 4.10 | Attractor for CMOS circuit generated by the Matlab script                  | 68 |

| 4.11 | Comparison of the MOSFET circuit attractors generated in AWR and           |    |

|      | by Matlab script                                                           | 69 |

| 4.12 | Steady state Harmonic Balance circuit simulation                           | 70 |

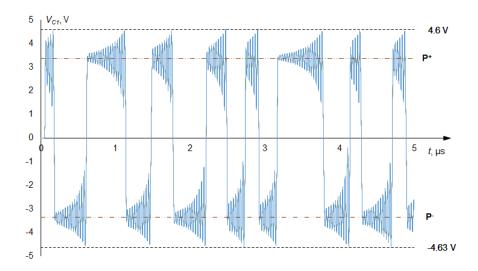

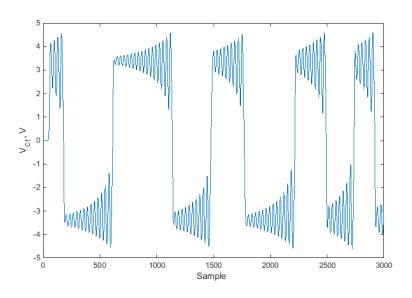

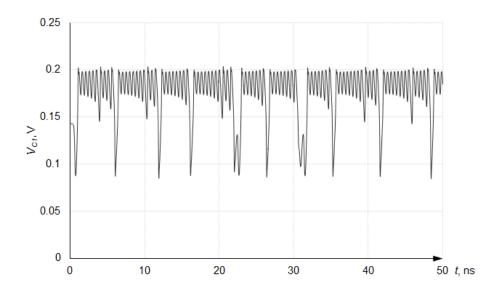

| 4.13 | $V_{C1}$ of the MOSFET Chua's circuit simulated in time domain by AWR.     | 71 |

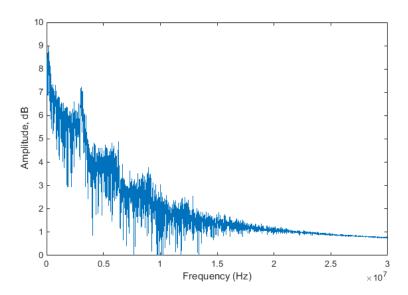

| 4.14 | $C_1$ voltage of the AWR-simulated MOSFET circuit in the frequency         |    |

|      | domain                                                                     | 72 |

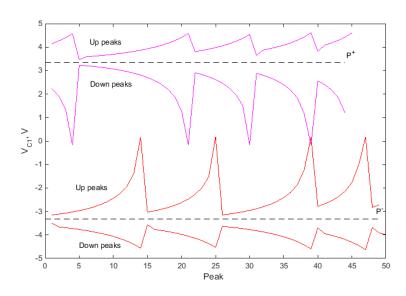

| 4.15 | The output of the Matlab equilibrium-level estimation algorithm            | 74 |

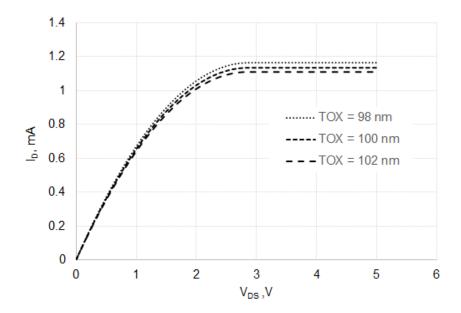

| 4.16 | NMOS output characteristic for three TOX values                            | 76 |

List of Figures xix

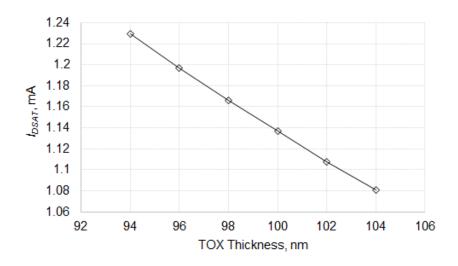

| 4.17 | Drain saturation current $I_{DSAT}$ as the function of gate oxide $TOX$ thick-     |    |

|------|------------------------------------------------------------------------------------|----|

|      | ness                                                                               | 76 |

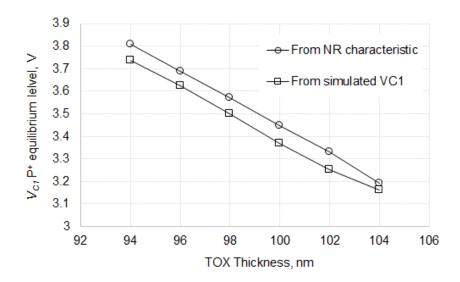

| 4.18 | Effect of gate oxide $TOX$ thickness change of the $V_{C1}$ $P^+$ equilibrium      |    |

|      | level                                                                              | 77 |

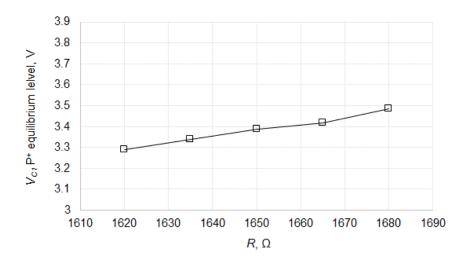

| 4.19 | Effect of linear resistor $R$ change of the $V_{C1}$ $P^+$ equilibrium level       | 78 |

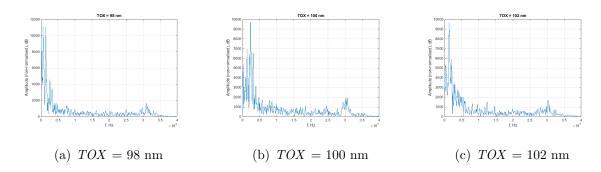

| 4.20 | Spectra of the AWR-simulated $V_{C1}$ , with MOSFET $TOX$ varied, ob-              |    |

|      | tained after Matlab FFT transformation                                             | 81 |

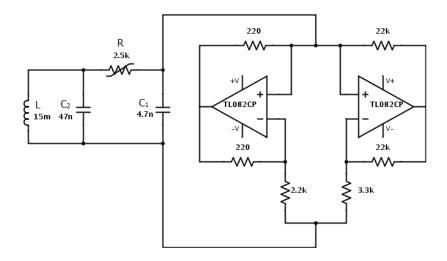

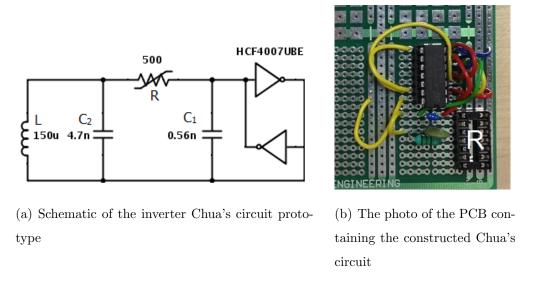

| 4.21 | The op-amp realisation of the Chua's circuit                                       | 82 |

| 4.22 | Measured signals generated by the op-amp Chua's circuit realisation. $$ .          | 83 |

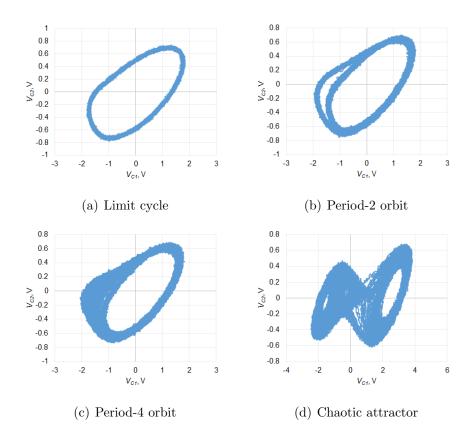

| 4.23 | Bifurcations occurring in the op-amp Chua's circuit with changing ${\cal R}.$      | 84 |

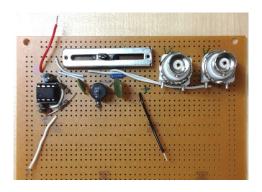

| 4.24 | The CMOS inverter realisation of Chua's circuit                                    | 84 |

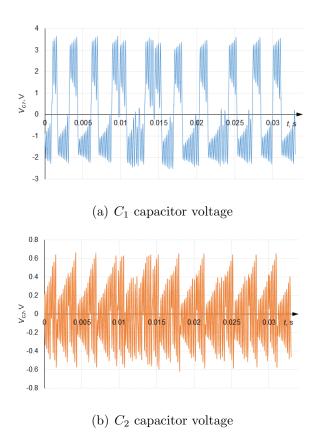

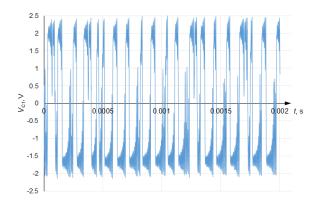

| 4.25 | Measured capacitor $C_1$ voltage in time domain                                    | 85 |

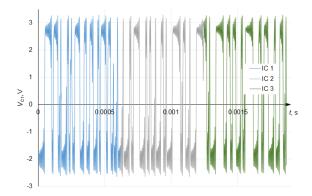

| 4.26 | Signals generated by the Chua's oscillator with three different 4007-series        |    |

|      | integrated circuits                                                                | 85 |

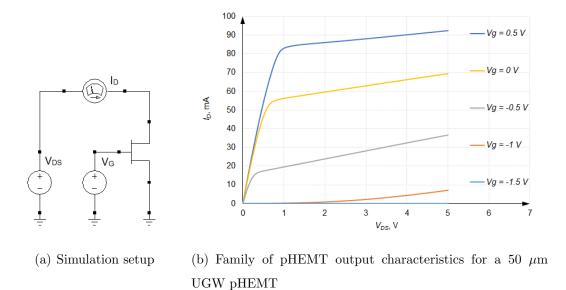

| 5.1  | The simulation of the PP-10 pHEMT output characteristics                           | 89 |

| 5.2  | The simulation of the PP-10 pHEMT output characteristics with vari-                |    |

|      | able unit gate widths $(UGW)$ with $V_G = 0$ V                                     | 89 |

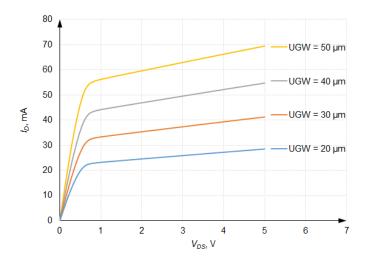

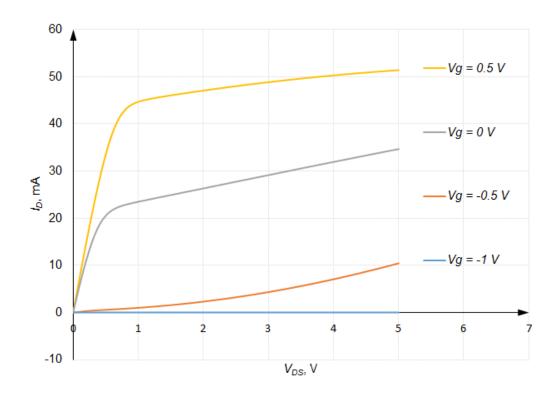

| 5.3  | The simulation of the PL-15 pHEMT output characteristics for a 50 $\mu \mathrm{m}$ |    |

|      | UGW                                                                                | 90 |

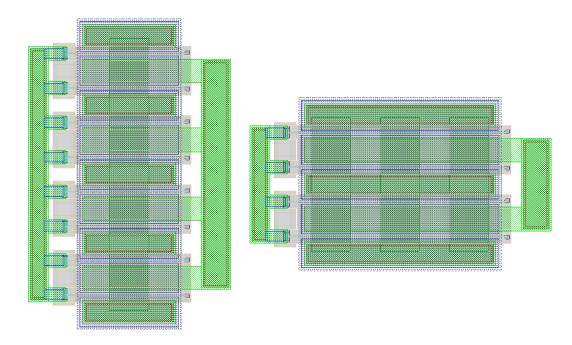

| 5.4  | The layouts (same scale) of two equivalent PL-15 pHEMTs: 8 finger by               |    |

|      | $50~\mu\mathrm{m}$ (left) and 4 finger by 100 $\mu\mathrm{m}$ (right)              | 91 |

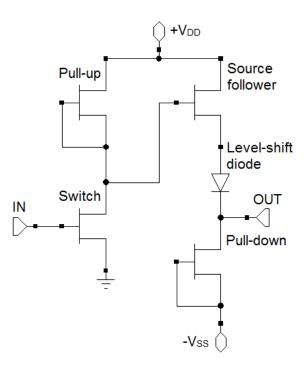

| 5.5  | Schematic diagram of the saturated-buffer logic inverter                           | 92 |

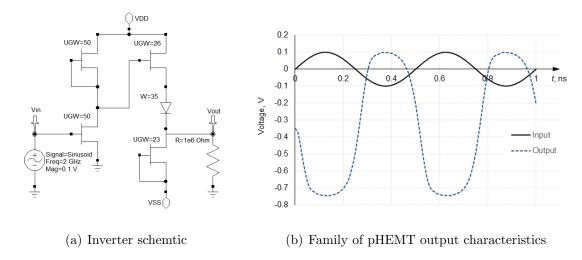

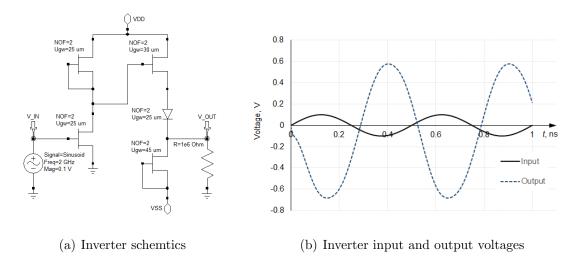

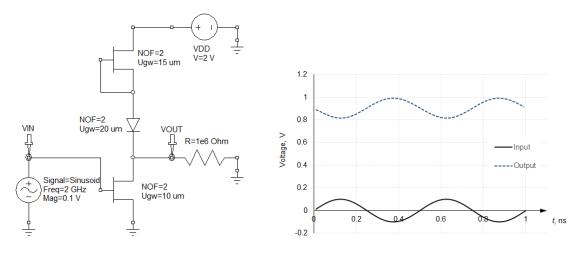

| 5.6  | Time-domain simulation of the inverter for the PP-10 process                       | 93 |

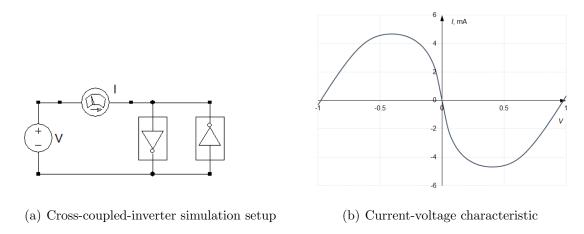

| 5.7  | Simulation of the PP-10 cross-coupled-inverters nonlinear resistor con-            |    |

|      | figuration                                                                         | 93 |

| 5.8  | Time-domain simulation of the inverter for the PL-15 process                       | 94 |

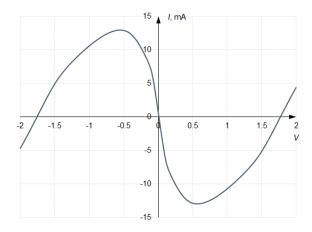

| 5.9  | Current-voltage characteristic of the PL-15 cross-coupled inverters. $$            | 95 |

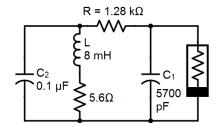

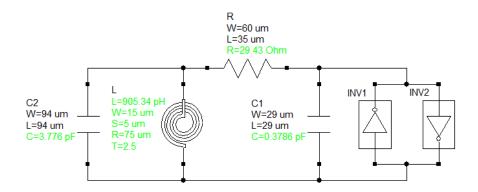

| 5.10 | Schematic diagram of Chua's circuit for the PP-10 GaAs process                     | 96 |

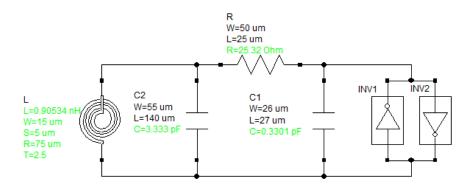

| 5.11 | The schematic diagram of Chua's circuit for the PL-15 GaAs process                 | 97 |

XX LIST OF FIGURES

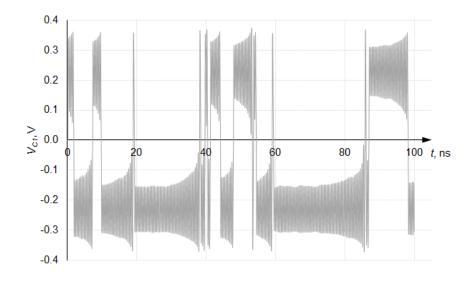

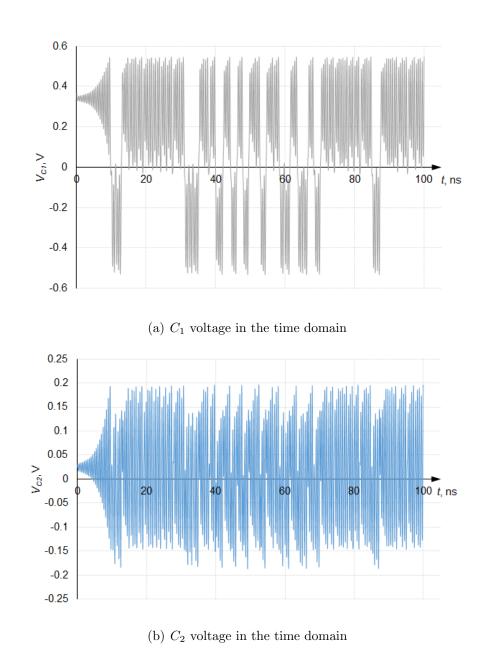

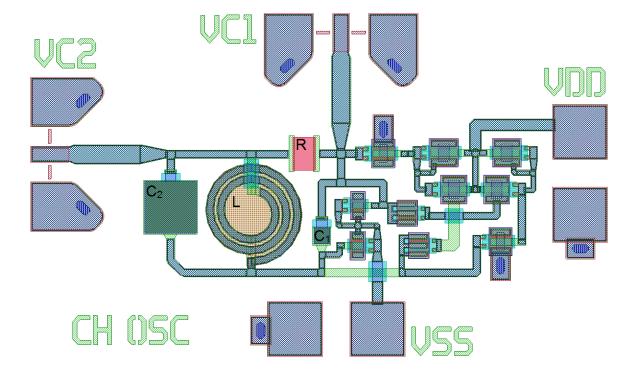

| 5.12 | Simulation of the PP-10 circuit's signals in the time domain                       | 99  |

|------|------------------------------------------------------------------------------------|-----|

| 5.13 | The chaotic attractor observed during the PP-10 design simulations                 | 100 |

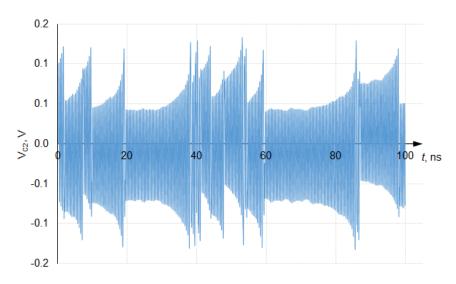

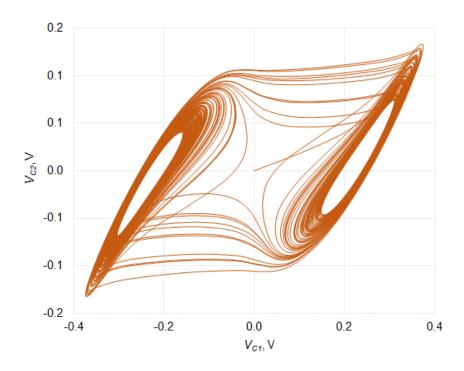

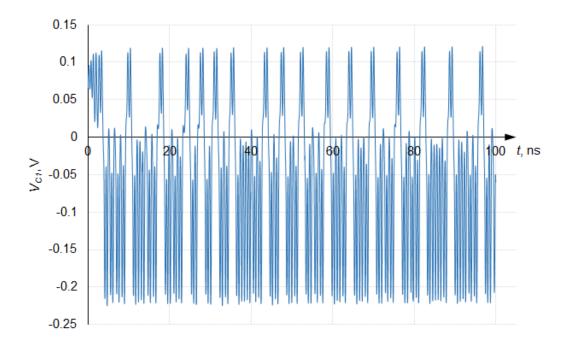

| 5.14 | Simulation of the PL-15 circuit's signals in the time domain                       | 101 |

| 5.15 | The chaotic attractor observed during the PL-15 design simulations                 | 102 |

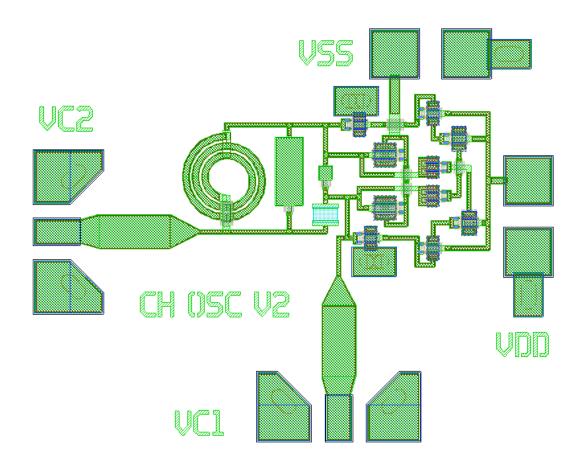

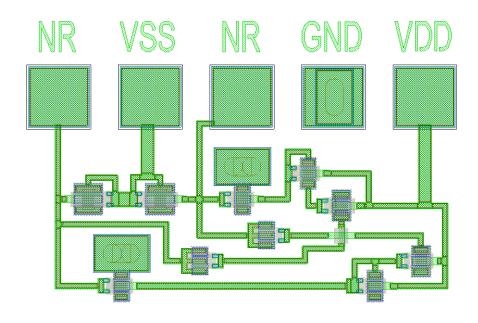

| 5.16 | The layout of Chua's circuit designed for the PP-10 manufacturing                  | 102 |

| 5.17 | Simulated $C_1$ voltage of PP-10 circuit with inclusion of the EM effects.         | 103 |

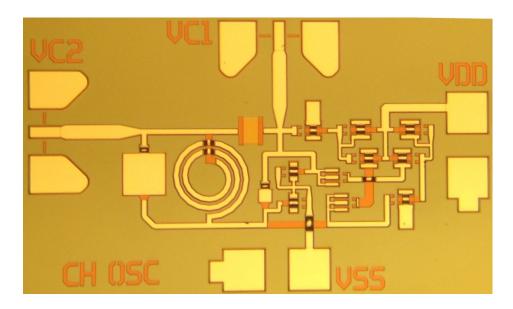

| 5.18 | Microphotograph of the manufactured Chua's circuit layout on the PP-               |     |

|      | 10 wafer                                                                           | 104 |

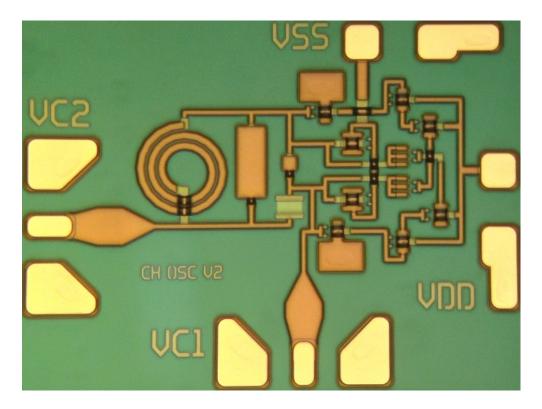

| 5.19 | The layout of Chua's circuit designed for the PL-15 manufacturing. $$              | 105 |

| 5.20 | Simulated $C_1$ voltage of PL-15 circuit with inclusion of the EM effects.         | 106 |

| 5.21 | Microphotograph of the manufactured Chua's circuit layout on the PL-               |     |

|      | 15 wafer                                                                           | 107 |

| 6.1  | The probe station with three probe holders mounted                                 | 110 |

| 6.2  | Instek DC voltage source                                                           | 110 |

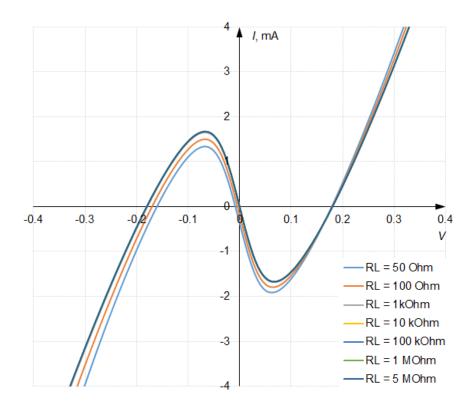

| 6.3  | Effective circuit current-voltage characteristics plotted for various loads        |     |

|      | connected to $C_1$                                                                 | 111 |

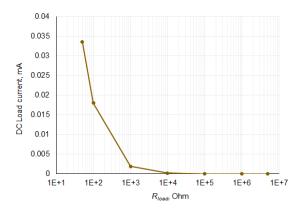

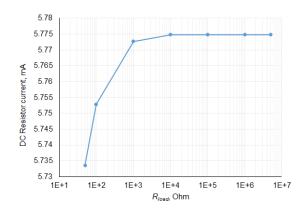

| 6.4  | Effect of load resistance $R_{load}$ on the circuit DC currents                    | 112 |

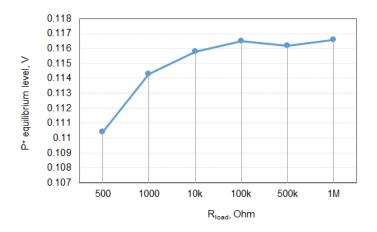

| 6.5  | Relocation of the $P^+$ of $V_{C1}$ with the change of load resistance $R_{load}$  | 113 |

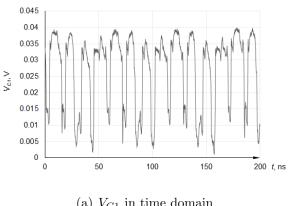

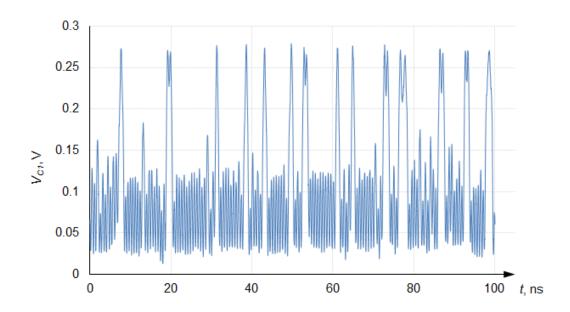

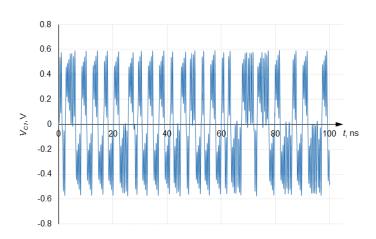

| 6.6  | Chaotic-like $\mathcal{C}_1$ capacitor voltage oscillations from the PP-10 circuit | 114 |

| 6.7  | $C_1$ capacitor voltages measured on the same reticle at different bias            |     |

|      | voltages from the PP-10 circuit                                                    | 115 |

| 6.8  | The spectra of period-1 and period-2 oscillations from the PP-10 circuit.          | 116 |

| 6.9  | The time-domain voltage measurement setup                                          | 117 |

| 6.10 | The capacitor $C_1$ voltage from the PL-15 circuit as measured by the              |     |

|      | oscilloscope                                                                       | 118 |

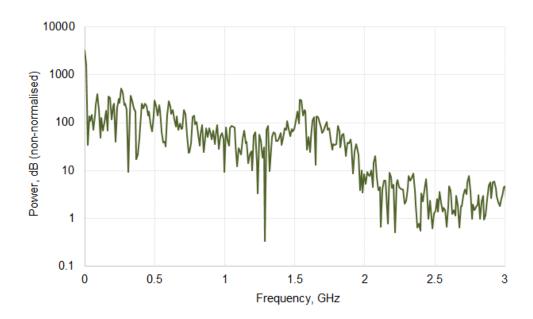

| 6.11 | Spectrum of the measured capacitor $C_1$ voltage from the PL-15 circuit            |     |

|      | obtained after Matlab FFT processing                                               | 119 |

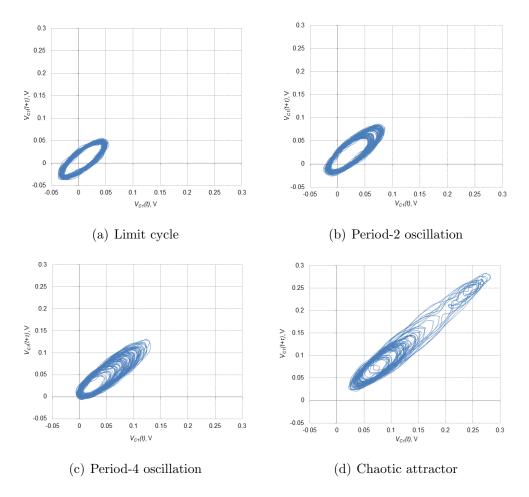

| 6.12 | Period bifurcations observed in the PL-15 Chua's circuit                           | 120 |

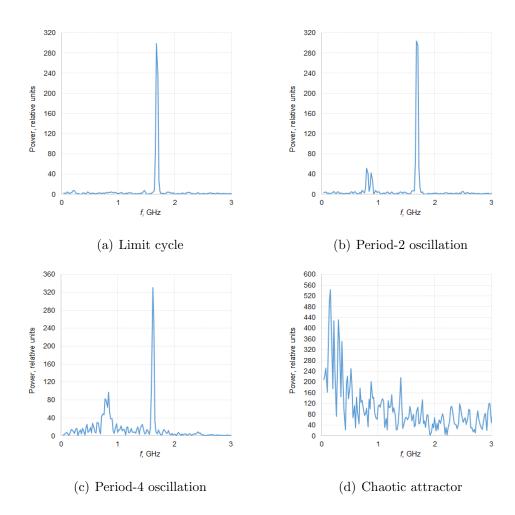

| 6.13 | FFT transformation of the bifurcating signals in the PL-15 circuit                 | 121 |

List of Figures xxi

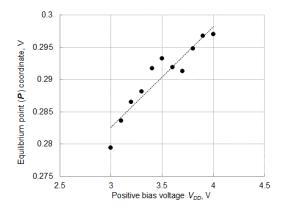

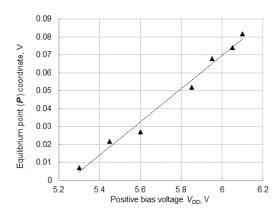

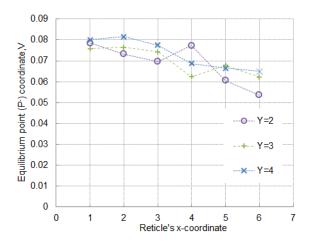

| 0.14 | Effect of the bias voltage on the equilibrium levels in the PL-15 circuit.                                             | 122 |

|------|------------------------------------------------------------------------------------------------------------------------|-----|

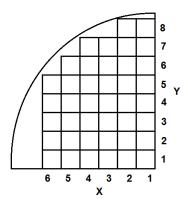

| 6.15 | The reticle map of the PL-15 quarter-wafer                                                                             | 123 |

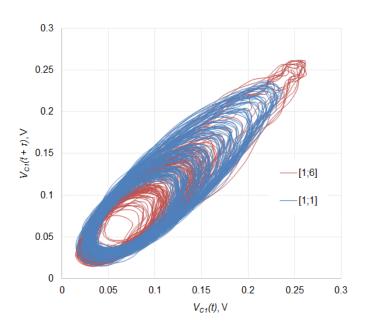

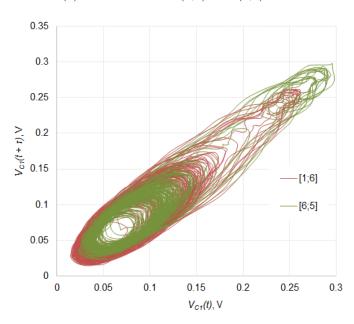

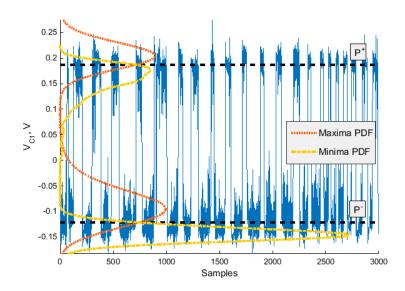

| 6.16 | Comparison of the attractors corresponding to the signals of the circuits                                              |     |

|      | at different locations on the PL-15 wafer                                                                              | 124 |

| 6.17 | The observed shift of the lower equilibrium level for the circuits at var-                                             |     |

|      | ious locations on the PL-15 wafer                                                                                      | 125 |

| 7.1  | National Instruments PXI chassis with the digitiser                                                                    | 128 |

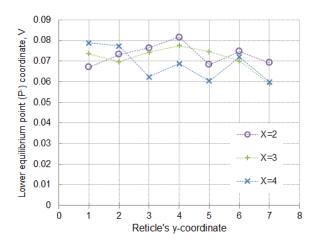

| 7.2  | The result of the equilibrium-levels estimation algorithm applied to the                                               |     |

|      | $V_{C1}$ time series                                                                                                   | 129 |

| 7.3  | The map of the quarter-wafer with the adopted reticle coordinate grid                                                  |     |

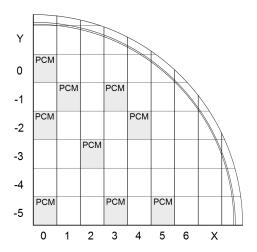

|      | and PCM data availability                                                                                              | 130 |

| 7.4  | The maps of the equilibrium levels separation for the CCMs of three                                                    |     |

|      | quarter-wafers                                                                                                         | 133 |

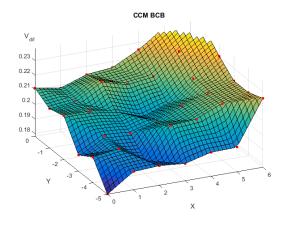

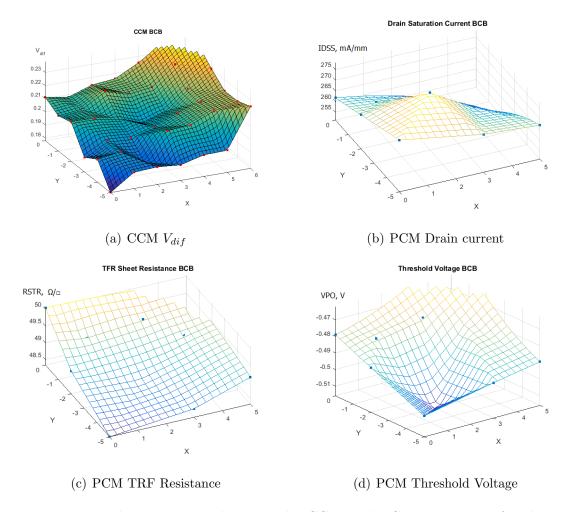

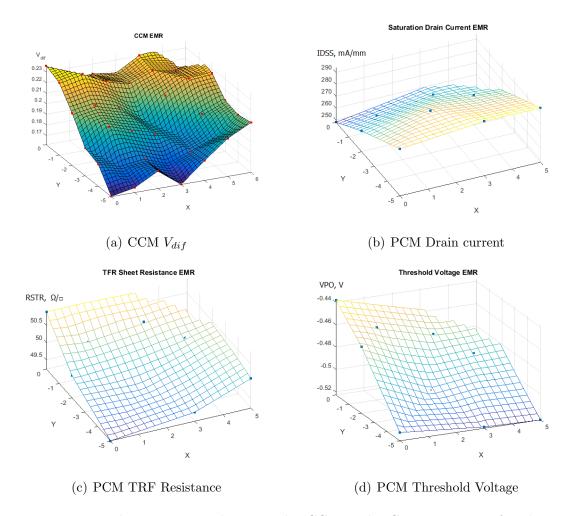

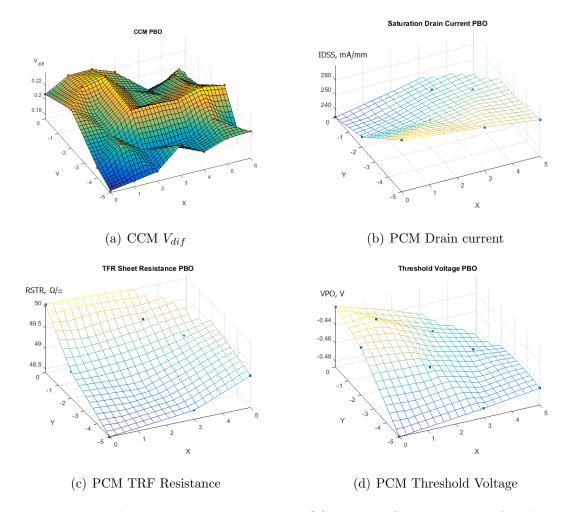

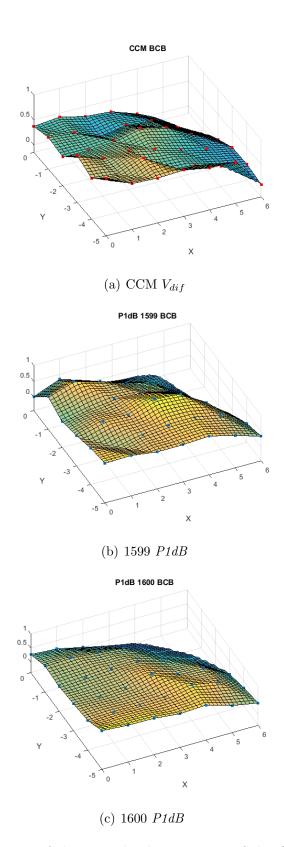

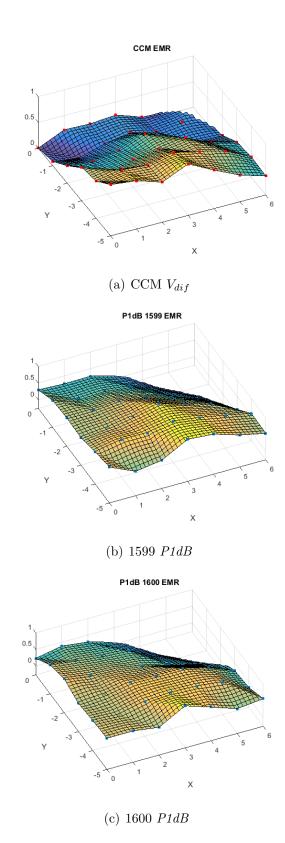

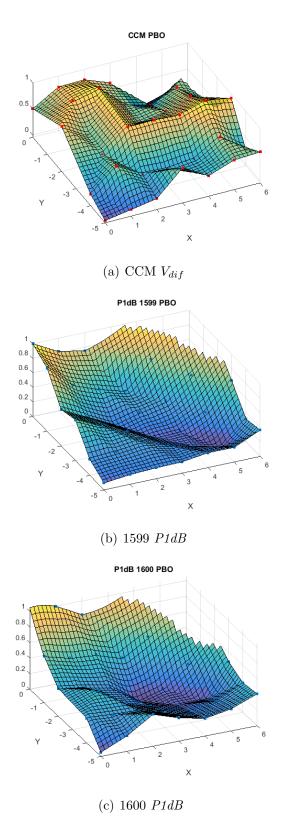

| 7.5  | The comparison between the CCM and PCM parameters for the BCB                                                          |     |

|      | quarter-wafer                                                                                                          | 134 |

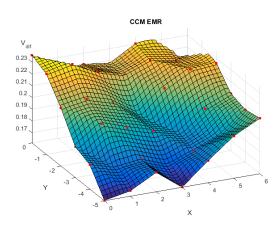

| 7.6  | The comparison between the CCM and PCM parameters for the EMR                                                          |     |

|      | quarter-wafer                                                                                                          | 135 |

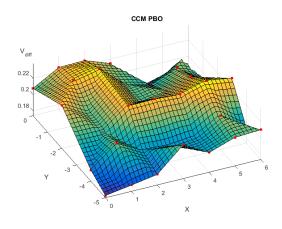

| 7.7  | The comparison between the CCM and PCM parameters for the PBO                                                          |     |

|      | quarter-wafer                                                                                                          | 136 |

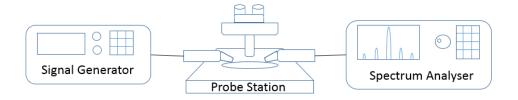

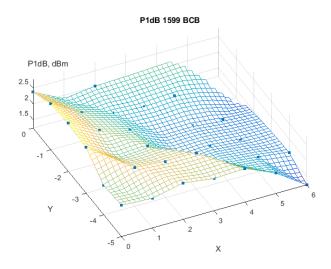

| 8.1  | The laboratory equipment used in the experiment                                                                        | 142 |

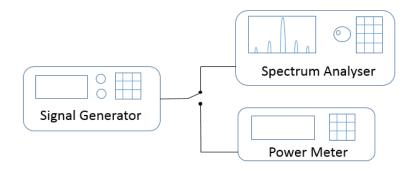

| 8.2  | The laboratory equipment setup for the $P1dB$ measurements                                                             | 143 |

| 8.3  | Spectrum analyser calibration setup                                                                                    | 143 |

| 8.4  | The laboratory equipment setup for the $P1dB$ measurements                                                             | 145 |

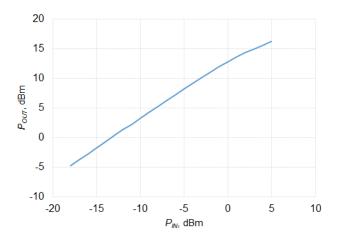

| 8.5  | The 1599 driver measurement results presented in two different ways. $% \left( 15000000000000000000000000000000000000$ | 146 |

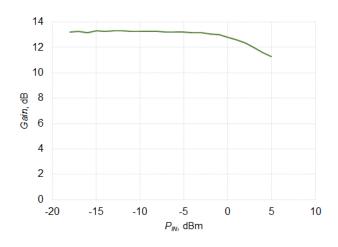

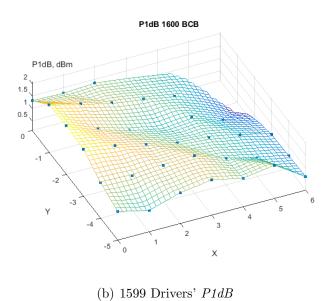

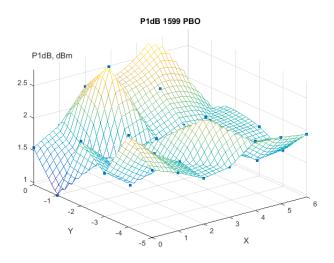

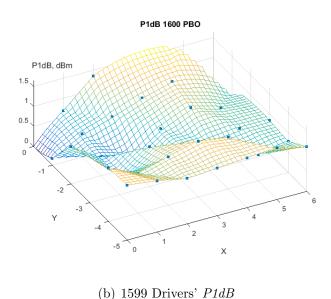

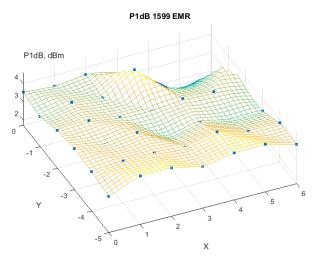

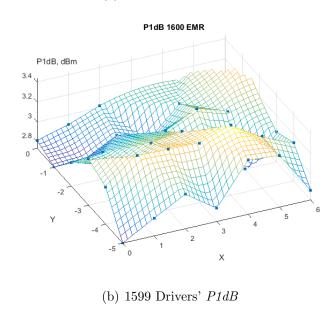

| 8.6  | 1 dB compression point of the drivers on the BCB wafer                                                                 | 147 |

| 8.7  | 1 dB compression point of the drivers on the PBO wafer                                                                 | 148 |

| 8.8  | 1 dB compression point of the drivers on the EMR wafer                                                                 | 149 |

| 8.9  | Comparison of the normalised parameters of the CCM and drivers on                                                      |     |

|      | the BCB wafer                                                                                                          | 150 |

xxii List of Figures

| 8.10 | Comparison of the normalised parameters of the CCM and drivers on |     |

|------|-------------------------------------------------------------------|-----|

|      | the EMR wafer                                                     | 151 |

| 8.11 | Comparison of the normalised parameters of the CCM and drivers on |     |

|      | the PBO wafer                                                     | 152 |

| 8.12 | The reticle map                                                   | 153 |

| 8.13 | Plotting CCM's $V_{dif}$ versus driver's $P1dB$                   | 154 |

| 9.1  | Suggested improved CCM design                                     | 163 |

| 9.2  | Time-domain simulation of $V_{C1}$                                | 163 |

| 9.3  | Optimised inverter design                                         | 164 |

| 9.4  | Layout of the NR-based CCM for external resonator                 | 165 |

# List of Tables

| 2.1 | Key parameters of WIN's PP-10 and PL-15 manufacturing processes                          |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | [11], [12]                                                                               | 12  |

| 2.2 | Comparison of possible CCM candidates                                                    | 20  |

| 4.1 | Simulation of linear resistor and piecewise-linear current-voltage func-                 |     |

|     | tion effect on $x_e$ coordinate of equilibrium point                                     | 59  |

| 4.2 | Simulation of linear resistor and cubic current-voltage function effect on               |     |

|     | $x_e$ coordinate of equilibrium point                                                    | 64  |

| 4.3 | Characteristics of chaotic signals and how they could be measured                        | 72  |

| 4.4 | Peak-to-peak voltage and $\mathbf{P}^+$ equilibrium level of $V_{C1}$ for varied $R$ and |     |

|     | TOX values                                                                               | 79  |

| 4.5 | Effect of $W$ and $NSUB$ change on the saturation drain current                          | 79  |

| 4.6 | Effect of $W$ and $NSUB$ changes on the coordinates of the $V_{C1}$ equilibrium          |     |

|     | levels                                                                                   | 80  |

| 5.1 | PP-10 process conductive layer characteristics                                           | 103 |

| 7.1 | Parameters measured during the PCM testing at WIN Semiconductors.                        | 131 |

| 7.2 | Correlation coefficients $\rho$ between the CCM characteristic, $V_{dif}$ and PCM        |     |

|     | parameters for the three quarter-wafers                                                  | 132 |

| 7.3 | PCM parameter measurement errors and standard deviation values for                       |     |

|     | BCB, PBO and EMR wafers.                                                                 | 137 |

|     |                                                                                          |     |

xxiv List of Tables

| 8.1 | The results of the spectrum analyser calibration                                  | 144 |

|-----|-----------------------------------------------------------------------------------|-----|

| 8.2 | Correlation coefficients $\rho$ of normalised CCM's $V_{dif}$ and normalised 1599 |     |

|     | and 1600 <i>P1dB</i>                                                              | 153 |

If you wish to make an apple pie from scratch, you must first invent the universe.

Carl Sagan

1

## Introduction

### 1.1 Motivation

Manufacturing integrated circuits is a complicated process as it involves multiple operations and processes. There are many stages in the process when things can go wrong and therefore a thorough control is needed.

The manufacturing process includes such operations as material deposition, etching and polishing, patterning using lithography, chemical treatment, epitaxy, etc. After most of these operations a control measurement is performed, such as layer thickness or sheet resistance measurement. These measurements help to monitor the equipment state and should it be necessary, the wafer can be scrapped or restored without going through all the process stages. Nevertheless such frequent testing is normally used only in experimental runs or when using novel processes or equipment. In production runs,

2 Introduction

however, such extensive control is not economically viable and normally major testing is performed at critical stages and at the end of the manufacturing cycle when process control monitors (PCM) are measured.

Process control monitors provide the possibility of measuring electrical characteristics of the devices and layers of the integrated circuit. Electrical measurements include, but are not limited to, measuring sheet resistance of layers, such parameters of FETs as transconductance, saturation drain current, leakage currents, threshold and breakdown voltages, etc. Often PCMs are placed in the scribe line in order to maximise the useful area of the wafer. Consequently, it is desired to have PCMs compact and small in size.

Testing of the PCM helps to identify process deviations and predict faulty circuits, as each of the measured parameters has certain control limits. Long-term observation of PCM data assists in tracking the equipment state and forecasting a process going out of control. However when we want to apply the PCM measured data to predict the functionality of the circuits on the wafer it often produces false results. Namely, good PCM measurements may not necessarily guarantee proper performance of the actual circuits, and the opposite event is possible as well.

Such a discrepancy may be caused by the devices in the PCM being biased in a different way than those inside the actual circuit, or possibly the density of the elements can also be a concern when different proximity effects come into play in the real circuit. Regardless of the actual cause, which we will leave for others to investigate, a more reliable monitor is needed in order to improve the yield by not scrapping good wafers and by timely scrapping of faulty reticles.

The problem has been raised by monolithic microwave integrated circuit (MMIC) designers when it was found that the simulation results do not accurately predict the performance of the physical circuit. Basically that means that the device models that designers use are not accurate over the whole range of operational conditions. It was understood that the performance of a MMIC can be predicted by scaling of the model parameters for a MESFET only in the cases when biases and operating conditions are similar [13].

1.1 MOTIVATION 3

In order to improve the predictability strength of the PCM, its successor, a circuit control monitor (CCM) is proposed. The main idea of a circuit control monitor is to restore the link between the manufacturing process state and circuit performance. A basic CCM is a simple, small circuit which can produce some measurable output. For high sensitivity to the manufacturing process, the circuit has to be nonlinear. Thus candidates for a CCM include low-noise amplifiers (LNAs), mixers and oscillators and possibly other highly nonlinear circuits. It is supposed that a CCM would be application specific, meaning that a radio-frequency integrated-circuit CCM would not be suitable for a digital to analogue converter testing, for example.

In our study on process monitoring improvement we propose a chaotic circuit for the role of a CCM. The main idea is to take advantage of such a chaotic-system property as severe sensitivity to initial conductions. Chua's chaotic oscillator was chosen for its simplicity and due to a extensive amount of information available about this chaotic system. It is hypothesised that inclusion of Chua's circuit in the PCM of a gallium arsenide pseudomorphic high-electron-mobility-transistor process can provide a predictive link between the PCM and nonlinear circuit performance data.

In order to test the hypothesis we firstly have to understand how GaAs processing influences circuit elements' electrical performance. It is important to recognise a relationship between device parameters and circuit performance. Mathematical modelling and computer aided design electrical simulation tools can greatly assist us with establishing this link. Before starting an integrated-circuit CCM design process, the circuit has to be prototyped on a board level for estimating the feasibility of the design.

Thereafter a functional GaAs pHEMT design of the CCM has to be developed. Application of pHEMT technology to Chua's circuit implies the redesign of the circuit without employing complementary devices, that can be manufactured in silicon process, but which are unavailable in most GaAs process. The manufactured devices have to be tested and measured. The obtained measurement results are to be analysed and processed in order to characterise individual oscillators. Then, finally, we can test our hypothesis by contrasting the obtained CCM characteristics and other devices' small-signal and large-signal parameters.

4 Introduction

### 1.2 Synopsis

Chapter 2 of this thesis provides an overview of modern compound semiconductor manufacturing processes. A particular emphasis is given on pseudomorphic high electron mobility gallium arsenide integrated-circuit manufacturing. Principles of pHEMT operation are explained along with the manufacturing process sequence examples. This is followed by explanation of semiconductor manufacturing quality control approaches and particularly methods of monitoring the electrical performance of the active devices by the means of process control monitor. It is shown that the PCM parameters are not directly linked to the nonlinear performance of functional circuits and hence the motivation for the current project is addressed. Consequently a new control method is described. It is proposed that an example of chaotic systems, which are inherently very sensitive systems, could make a good candidate for the role of a CCM. An introduction to the chaos theory is accordingly presented followed by the explanation of the selected candidate's, Chua's chaotic oscillator's, operation.

Chapter 3 provides the results of performed analysis of Chua's circuit. The chaotic system's mathematical properties are studied in detail. The performed analysis made a foundation for the following work. It is identified that chaotic signals contain certain features that could be linked to the circuit components.

Chapter 4 includes the theoretical work needed for the preparation of Chua's circuit for the role of a CCM. The circuit's mathematical model constructed in Matlab is presented. The behaviour of the circuit in different configurations and with variable parameter values is investigated. That is followed by presentation of the initial design of the electrical circuit in AWR Design Environment assembled for circuit simulations. A comparison between the mathematical and circuit simulations is performed and all the similarities and discrepancies are pointed out. Two circuit implementations as board-level prototypes are presented along with their measurement results.

Chapter 5 describes the integrated-circuit CCM design. Two versions of Chua's circuit prepared for two similar GaAs pHEMT manufacturing processes are presented. The background information about the employed processes is given. The design of

1.2 Synopsis 5

the circuit schematic is followed by presenting the prepared circuit layouts. A new version of nonlinear resistor implementation is discussed. Results of the simulations demonstrating chaotic behaviour are presented.

Chapter 6 provides the results of initial measurements performed on the two produced circuits. The measurement setup and procedure are described along with the method of signal analysis. The results show the variation of the output signal characteristics among the circuits in different locations of the wafer. The fluctuation of suggested CCM circuit characteristics suggests sensitivity of the designed monitors to different manufacturing process parameters. The advantage of one design over the other is shown. The study of chaotic signal's characteristics variation across the wafer is discussed in the following paper:

E. Kuxa, A. E. Parker, S. J. Mahon, A. Dadello, W.-K. Wang, M. C. Heimlich, Process control in GaAs manufacturing using Chuas circuit. CS MANTECH Conference, May 2014

Chapter 7 discusses the CCM's characteristics correlation with various PCM parameters. The CCM measurement results are plotted to graphically present the variation across the wafer. The same process is performed for the PCM parameters which are subsequently correlated with the CCM data. The results of the correlation procedure are presented in the following paper:

E. Kuxa, A. E. Parker, S. J. Mahon, A. P. Fattorini, W.-K. Wang, R. Kuo, M. C. Heimlich, *Chua's Chaotic Oscillator as the GaAs Manufacturing Process State Indicator*. APMC 2014, November 2014

Chapter 8 addresses the established link between the CCM performance and performance of real nonlinear circuits. Two driver amplifier circuits are measured to obtain their nonlinear characteristics. The circuit measurement procedure is discussed and the results are presented. The variation of the drivers' measured characteristics is presented along with the variation of the CCM indicator. The measured data are correlated and confirm the existence of the link between the nonlinear performance of real circuits and performance of circuit monitors.

6 Introduction

The *Chapter 9* finalises the work by listing the outcomes and suggesting topics for the future work on the subject.

Appendix A contains the listings of all developed Matlab scripts.

### 1.3 Scope of the Work

The main goal of the work is to develop a procedure for monitoring a GaAs pHEMT manufacturing process. Numerous ways of process monitoring with the help of circuits are discussed, however the focus of this project is on applying chaotic systems for the role of process monitoring. Particular class of these systems, namely chaotic oscillators, are chosen for the study; Chua's circuit, as a most simple representative of chaotic oscillators, was scrutinised. Other kinds of nonlinear circuits and their application to process monitoring lie beyond the scope of this work.

It is examined how chaotic signals can be interpreted and which of their features can be related to the manufacturing process state. It is expected to find a correlation between the features of chaotic signals and manufactured devices linear and nonlinear characteristics. The project is not aimed on obtaining significant statistical data on the performance of the proposed circuit monitor, while it is required to prove the concept of chaotic-circuit-based process monitoring.

Everyone is stupid except me.

Homer Simpson

2 Overview

## 2.1 Gallium Arsenide Manufacturing

The evolution of the wireless technologies over the past couple of decades pushed forward the development of compound semiconductors. The industry of III-V semiconductors including GaAs HBT amplifiers and pHEMT switches has seen a significant growth [14]. A fundamental driver of the compound-semiconductor manufacturing are the developments in cellular networks of the 4th [15], [16] and 5th generations which require GaAs amplifiers and switches in the mobile handsets as well as in the base stations. Other areas of GaAs MMICs wireless applications include automotive radar [17], aerospace [18] and defence [19], VSAT [20] and also wired networks such as CATV and broadband [21].

The field effect transistors (FETs) implemented in gallium arsenide which used

8 Overview

Schottky barrier for the gate were first introduced in 1967 [22] and they provided good amplification and low-noise performance at frequencies higher than in conventional bipolar junction transistor (BJT) amplifiers. The advances in molecular beam epitaxy and metal-organic chemical vapour deposition processes allowed thin layers of various semiconductor to be laid down on the GaAs substrate. That development led to creation of high electron mobility transistor (HEMT) [23].

#### 2.1.1 pHEMT Manufacturing Process

High electron mobility transistors are the group of devices which in their operation rely on heterojunctions often built using III-V semiconductors. The heterojunctions are formed between semiconductors of different compositions and band gaps, such as GaAs/AlGaAs. In a HEMT free electrons are physically separated from the ionised donors due to a specially designed epitaxial layer structure, thus the electron mobility is increased [24]. Conventionally, the epitaxial layers are grown employing molecular beam epitaxy (MBE) [25] or metal-organic chemical vapour deposition (MOCVD) [26] and may be doped or undoped depending on the requirements.

The HEMT active layer is composed of GaAs and AlGaAs layers. The most important heterojunction is that between the Si-doped AlGaAs and the undoped GaAs. The band gap of AlGaAs is higher than the band gap of the adjacent GaAs, which results in the diffusion of free electrons from AlGaAs into GaAs thus forming a two-dimensional electron gas (2-DEG) at the heterointerface. There are no ionised donors in the channel, therefore the 2-DEG does not suffer from Coulomb scattering and exhibits very high mobility.

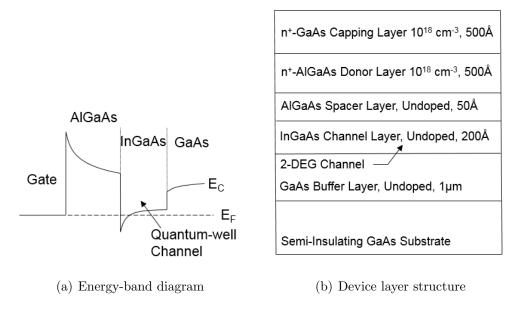

HEMT performance can be improved if InGaAs is used as the 2-DEG channel instead of GaAs. Pseudomorphic high electron mobility transistor's layer structure and energy-band diagram are shown in Fig. 2.1. The InGaAs channel is called pseudomorphic because its lattice unnaturally compresses to mirror the structure of GaAs. The pseudomorphic device, or pHEMT, is based on the AlGaAs/InGaAs/GaAs structure, and the electrons flow in the strained quantum-well InGaAs channel. The benefits include enhanced electron transport, improved confinement of carriers in the quantum

well along with a higher current density and transconductance than that of a conventional HEMT [27]. For example, Mishra et al [28] compared two HEMT devices of their fabrication and pseudomorphic structure exhibited 11.6 % better transconductance performance comparing to a similar HEMT device. At the same time, the cut-off frequency was increased from 175 GHz up to more than 200 GHz in a pHEMT.

FIGURE 2.1: GaAs pseudomorphic HEMT [1].

It is desirable to use a higher InAs mole fraction because then the energy band gap increases, enhancing the carrier transport properties. However in this case the lattice mismatch strain between InGaAs and GaAs rises and the quantum-well thickness is required to be very small, which is challenging to achieve. The solution to that can be the use of a thin strained supperlatice structure (Fig. 2.2) when thin GaAs layers are included in the InGaAs channel to smooth the surface of the InGaAs [1].

At a foundry it is very important to have a well-controlled and stable material growth process, or epitaxy. For example, layer growth rate in a MOCVD process will depend on temperature, flow rate of precursors, pressure, etc. In a MBE process, where an additional wafer preparation chamber is normally used, substrate surface preparation by chemical treatment is also important [29]. The properties of the grown

10 Overview

| n+-GaAs                                   | 500Å |                 |

|-------------------------------------------|------|-----------------|

| n+-Al <sub>0.3</sub> Ga <sub>0.7</sub> As | 500Å |                 |

| Al <sub>0.3</sub> Ga <sub>0.7</sub> As    | 50Å  |                 |

| In <sub>0.35</sub> Ga <sub>0.65</sub> As  | 50Å  | Undoped         |

| GaAs                                      | 15Å  | Active<br>Layer |

| In <sub>0.35</sub> Ga <sub>0.65</sub> As  | 50Å  |                 |

| GaAs Buffer                               | 1μm  |                 |

|                                           |      |                 |

GaAs Substrate

FIGURE 2.2: Thin strained superlattice pseudomorphic active layer structure [1].

| S<br>n+ GaAs | G              | D<br>n+ GaAs |

|--------------|----------------|--------------|

|              | i- AlGaAs      | Si δ-doping  |

|              | Spacer         | or c-doping  |

|              | i-Channel      |              |

|              | Spacer         | C: S 4i      |

| i- AlGaAs    |                | Si δ-doping  |

|              | Buffer         |              |

|              | S.I. Substrate |              |

FIGURE 2.3: The 0.15  $\mu m$  optical-gate pHEMT device [2].

layers affect the performance of manufactured devices. Fluctuations of doping and thickness of a capping layer will result in irregularity of transconductance,  $g_m$  and cutoff frequency,  $f_t$ . The same effects are observed for AlGaAs donor layer doping level

fluctuation. Lithography process, which is critical in gate formation, needs precise

control. Variation of gate width across the wafer will result in variation of device speed

of operation [1].

WIN Semiconductors is a GaAs foundry which has developed numerous technologies employing HBTs, BiFETs and pHEMTs [30]. It is worth describing WIN's GaAs pHEMT manufacturing process, as this work leverages circuits manufactured by WIN Semiconductor's fabrication plant.

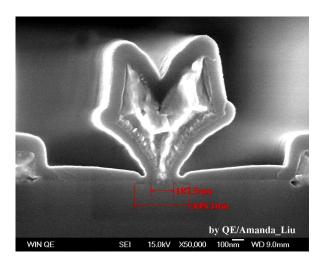

FIGURE 2.4: Scanning electron microscope cross-section of the 0.15  $\mu m$  optical gate [2].

The present 0.15  $\mu m$  pHEMT process utilises molecular beam epitaxy (MBE) material growth and an i-line ( $\lambda_i = 365$  nm) stepper for formation of the gates. The epitaxial structure consists of a high In concentration undoped InGaAs channel layer and double  $\delta$ -doped layers, that provide the carriers to the channel. There are AlGaAs spacer layers grown between the channel layer and Si layers, and on top of the upper spacer layer an AlGaAs Schottky layer is placed. The final layer structure is presented in Fig. 2.3. The gate is formed using so-called optical-gate flow. The gate photolithography is usually the most critical and yield-limiting process step. For the shown process, 99.2 % of the devices on the wafer showed normal performance, indicating that the gate photo-lithography is very well controlled. The cross-section of the optical gate is displayed in Fig. 2.4 [2].

Another high-performance developed process employed electron-beam, or e-beam, lithography [31] in the process of gate formation. The result is that the gate, with width of 100 nm at the bottom and 500 nm at the top is placed in the 2  $\mu$ m drain-source region thus achieving ultra-low resistance of the channel [11].

Both the aforementioned processes, codenamed PL-15 and PP-10 correspondingly, were utilised within the course of this project. The key parameters of these processes are listed in Table 2.1. Both processes employ two-level metallisation, similar thin film

12 Overview

| Manufacturing Process              | PP-10                  | PL-15                  |

|------------------------------------|------------------------|------------------------|

| Parameter                          | Value                  |                        |

| Peak transconductance, $G_{Mpeak}$ | 725 mS/mm              | 550 mS/mm              |

| Maximal drain current, $I_{Dmax}$  | $760~\mathrm{mA/mm}$   | 500  mA/mm             |

| $f_t$                              | $130~\mathrm{GHz}$     | $95~\mathrm{GHz}$      |

| $f_{max}$                          | $180~\mathrm{GHz}$     | _                      |

| Pinch-off voltage, $V_{to}$        | -0.95 V                | -0.7 V                 |

| MIM Capacitance                    | $400~\mathrm{pF/mm^2}$ | $400~\mathrm{pF/mm^2}$ |

| TRF Resistance                     | $50~\Omega/\Box$       | $50~\Omega/\Box$       |

TABLE 2.1: Key parameters of WIN's PP-10 and PL-15 manufacturing processes [11], [12].

resistor structures and silicon nitride PECVD for standard MIM capacitors.

According to [11], measurements of the PP-10 two-finger 75  $\mu$ m gatewidth devices suggest that average value of  $g_m$  is 728.4 mS/mm with a 4.5 mS/mm standard deviation, average pinch-off voltage is -0.95 V with a 0.03 V standard deviation and  $f_t$  is 134 GHz with a 3.3 GHz standard deviation. Average breakdown voltage measured on a 25-finger 75  $\mu$ m gatewidth pHEMT is 9.5 V with a 0.12 V standard deviation.

## 2.2 Semiconductor Manufacturing Process Control

For every industry it is important to have a reliable and repeatable manufacturing process. Semiconductor production, being utterly complicated, also greatly relies on process control as a means of achieving high-yield manufacturing. A specific feature of the semiconductor manufacturing process is that it has hundreds of sequential steps, with potential yield loss occurring at every step [32].

Yield is often divided into mechanical and parametric. Mechanical yield loss can happen due to a wafer breakage or other sort of damage. Parametric yield in its turn is based on the electrical tests.

Statistical Process Control (SPC) has been widely adopted since the beginning of the commercialisation of IC manufacturing [33]. The original aim of SPC was to

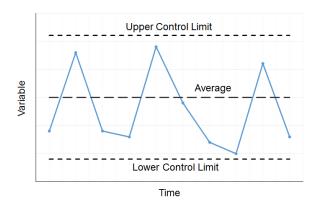

Figure 2.5: Typical control chart.

summarise the process and, should in the future the performance deviate from the norm, an alarm is raised and measures are taken to correct the root causes of the problem. The process is claimed to be in statistical control when it shows only routine run-by-run variations, which happen due to natural process fluctuation and systematic measurement errors. On the other hand, departures from those variations indicate that the process is out of statistical control. For every large deviation from the norm an assignable cause may be defined. As opposed to chronic or routine sources of variation, which are usually present due to inherent measurement errors or unavoidable inaccuracies of equipment sensors or control equipment, an assignable cause implies that something can be found and corrected or avoided such as equipment failure or operator mistake.

The fundamental tool of SPC is a control chart which can aid in detection and elimination of sources of unnecessary variations. This chart graphically displays how some sample quality characteristic changes with time. A typical control chart is presented in Fig. 2.5. Upper control limit (UCL) and lower control limit (LCL) are selected such that if a process is under statistical control mostly all of the points will fall between them. Should a point fall outside of the control limits it is going to indicate that a process is out of control. An average, or centre, line corresponds to an in-control state [32].

Control charts can help prevent a process from going out of control. For example,

when a trend, or run, is seen on the chart, suggesting that soon points will start falling outside of control limits, appropriate actions of eliminating a root cause should be taken, thus maintaining the process in-control. For example, it may happen that in a dielectric chemical vapour deposition chamber, a dielectric film is growing on an RF electrode due to degrading chamber cleaning process. This results in decreased deposition rate and deposited layers getting thinner from run to run. An experienced process engineer would be able to point that cause and take measures like increasing a cleaning step time or manual chamber cleaning.

Any process engineer wants to have some tools to control the process inside the chamber where the wafer processing is taking place in real time. Unfortunately, many critical wafer parameters, such as sheet resistance and layer thickness, can only be obtained after the contact measurements, procedures which can destroy the wafer surface. As opposed to contact measurements, real-time control is often performed by utilising the in-chamber parameters, such as temperature, pressure, RF power, etc. measured by various sensors. These parameters affect the critical wafer parameters (layer thickness, resistivity, etc.) indirectly. Moreover, the manufacturing processes suffer from a high level of system nonlinearity and often corrupted by slow drift due to maintenance operations, for example. Therefore models, which relate process variables to in-situ variables can be utterly complicated and computationally intensive [34].

The process control monitor (or module) normally contains such test structures as transistors (MOSFETs, HBTs, HEMTs, etc.), different functional layers, such as metal layers, resistive layers and, depending on the technology, capacitive structures too. This monitor is placed somewhere on the chip along with the production circuits, or can be placed in the scribe line region to save functional space. Test structures can include short circuit check units and open circuit check units. Normally these objects are represented by comb or meandering lines [35]. Certain PCM parameters, for example, metal sheet resistance or dielectric thickness can be measured straight after the corresponding process step by four-point probe testing [36] or spectroscopy [37]. At the same time, electrical properties of active devices can be tested only after all process steps are finished and before the wafers are prepared for slicing.

The measured *electrical* data is called parametric data and usually includes such semiconductor device parameters as threshold voltage, forward, reverse and leakage currents, resistivity of the layers, etc. The parametric data itself can not indicate a failure. Diagnosing steps are needed to be taken by a qualified engineer in order to find the root cause of the failure. Usually, there exists a many-to-many relationship between the PCM parameter and process factors, making it virtually impossible to define a faulty process step from the deviation of certain PCM parameter away from the mean value [38].

Electrical testing of circuits is done to ensure the correct operation of the final product and also to guarantee stable operation of the fabrication process. The PCM is tested by the fabrication plant on finished wafers, at both DC and RF, and based on the results wafer is accepted or rejected. Additional tests may be carried on finished dice or packaged parts, which is usually done at the customer site. The speed of testing is of vital importance, thus wafers are often tested employing a combination of probes and automated parametric testers [39].

Quality PCM tests are required for maintaining high yield or verifying improvements made to the process. DC wafer probe tests are fast and reliable, however wafer-level DC measurements do not necessarily guarantee acceptable RF module performance. RF measurements can be incorporated in the wafer-level tests for a faster feedback. The results can also be used for device modelling such that the extracted parameters can be used by circuit designers [40].

The RF part of PCM measurements firstly peruses the purpose of providing information on key manufacturing parameters to process and device engineers. Simultaneously, such device figures of merit as RF gain, transit time,  $f_t$  are reported and used in device models, such as hybrid- $\pi$ . RF test measurements can be done in-line, i.e. similarly to PCM DC tests, however require calibration structures integrated on wafer (e.g. open circuit, short circuit, load and through line) [41].

Normally, circuit designers use empirical FET models which may not accurately represent the FET under all circumstances. Typically this model is developed from a device under specific bias conditions, while in production the circuit may not be using

the FET under nominal conditions and thus the empirical model does not match the 'true' FET model [42]. Therefore, yields can be lower than expected and it would be hard to define whether the reason for that are the tests themselves or poor-quality wafers, for example. Moreover, it is possible that the devices in the PCM operate differently from those in the circuit because of the element density. Densely packed FETs may suffer from various proximity effects from nearby devices, metal lines, or multiple gate fingers [43]. The PCM device normally stands alone and is not a subject to electromagnetic effects and thus, even though the in-circuit devices may still be operating under normal bias conditions, their performance nevertheless varies.

Usually a PCM test of pHEMT will include measuring drain current  $I_d$  as a function of source-to-drain voltage  $V_{ds}$ . Measuring a family of this characteristics for a range of gate-to-source voltages  $V_{gs}$  helps identifying the drain saturation current  $I_{dss}$  and extrinsic transconductance  $g_m$ . The threshold voltage  $V_{th}$  is defined by linear extrapolation of the square root of the drain current versus gate voltage to zero current. Pinch-off characteristic can be obtained from measuring gate current as a function of gate voltage. A network analyser can be engaged into measuring the pHEMT's scattering parameters, such as current gain,  $|h_{21}|$ . The cut-off frequency  $f_t$  can be found by extrapolating current gain versus frequency function to unity using a -6 dB/octave slope [44].

It was found by Baumberger in his work [45] that main performance parameters of a GaAs MESFET, such as  $g_m$ ,  $f_t$  and  $V_{th}$  are strongly correlated with drain current  $I_d$  measured at fixed bias voltages  $V_{gs}$  and  $V_{gs}$ . That is taken as an indication that observed process variations are one-dimensional in nature and thus can be represented by a single parameter,  $X_S$ , which can be incorporated into the device SPICE model. This factor was included in empirical formulas for  $V_{to}$ ,  $\beta$ ,  $C_{gs0}$  and  $C_{gd0}$ . During the simulations  $X_S$  can be swept (0.9–1.1) representing the expected process extremes.

As opposed to small-signal parameters of linear models (e.g. hybrid- $\pi$ ), large-signal excitations, when device operation is nonlinear, depend on the device's size, especially when the highest harmonic frequency is comparable with this size. Circuit envelope is a simulation technique commonly used in microwave communication systems analysis for

transient and steady state simulations. Device parasitics and active parameters can be used for this model to simulate the nonlinear behaviour of the circuits. This method's results are close to the results of the lumped model simulation yet the difference is noticeable. It is stated that the distributed model, that is circuit envelope, is supposed to have a better correspondence with the measurements [46]. However the mismatch indicates that the models have limited applications and linear device parameters are hard to utilize in the models, predicting RFIC's nonlinear behaviour.

As a result, circuit designers use models that have limited validity – a model is not reality. When process fluctuations occur, PCM can indicate that, but the deviation may be considered insignificant; however it could result in a change of the FETs biasing regime to one where the device model is not suitable. Thus the circuit behaves in an unexpected manner and the yields appear to be low. That creates a niche in the process control actions that needs to be filled. There is a requirement for a monitor that can perform as a PCM but is at the same time suitable for the RF tests, and which additionally has a better correlation with the nonlinear performance of the circuits.

It would be naïve to assume that the problem of mismatch between small-signal device model predictions and real nonlinear performance is not being investigated. On the contrary, a lot of effort is put towards improving the wafer tests. Engineers try to make tests simpler, faster to perform and at the same time more reliable. Analytical fault models help to improve the test accuracy keeping the test variables at minimum [47]. One of the analogue circuit testing methods, referred to as signature testing, involves applying a short transient stimulus to the circuit under test and analysing the response in order to predict the circuit specifications [48]. The transient testing focuses on the circuit response to an arbitrary periodic or aperiodic waveform. The goal of the test process is to design a signature test stimulus that is constrained by the performance of the wafer in such a way that signature test response would contain information about the specifications of a bare die. That is followed by developing a model which includes the package parasitics and predicts the specifications of the circuit as seen from the package terminals.

The faults of analogue circuits can be subdivided into catastrophic faults, which are

caused by short or open circuits or due to dust particles, and parametric faults which happen due to the fluctuations in the manufacturing environment. Among the former faults are the faults caused by process gradients which can result in device mismatch. In their work [49], L. Milor and V. Visvanathan propose an algorithm of generating tests to be implemented before wafer probe measurements to filter out faulty reticles early in order to save time and resources. Therefore the first step of the algorithm is to determine a tolerance box of process parameters (e.g. layers thickness, doping levels), defined by process engineers. Secondly, map the tolerance box by the sensitivity matrix of the good circuit into the measurement space axis of which correspond to a measurement to be introduced before specification testing in wafer probe. The approach of simulation-before-test was taken. The idea is to compare the test result with one from the simulated database and define the fault by determining the closest simulated fault signature.

## 2.3 Circuit Control Monitor

The approach to process monitoring investigated here involves including simple nonlinear circuits in the process control monitor area and consequently referred to as circuit control monitor, CCM. Although the effective area on the wafer may thus be compromised, the benefits of better monitor sensitivity could outweigh this drawback.

It is expected that the correlation between the performance of transistors in a CCM with the devices in the actual circuit will be stronger. The output of a CCM is affected not only by the linear transistor characteristics but also by the influence of conductive lines. The superposition of these effects may not be linear therefore not properly simulated by the model circuits.

A proper CCM candidate has to be chosen for having a strong correlation between its performance and that of real circuits. The candidates for the CCM should produce some measurable signals from which the state of the process can be estimated. The possible list of candidates includes, but is not limited to, low-noise amplifiers, mixers and oscillators. LNAs can be subjects to gain measurements, measurements of third-order intercept point, 1 dB compression, etc. Mixers can be characterised by their conversion loss or gain, noise figure or isolation. Oscillator measurements can include their output power, frequency and phase noise. At the same time, to make the CCM measurements effective, the procedures for circuit testing should be as simple as possible and preferably not use complicated measuring equipment which needs careful calibration. Otherwise, measurements of CCMs would require efforts similar to measuring real functional circuits.

We can now briefly review the existing circuits from the aforementioned classes. The comparison of viable CCM candidates is given in Table. 2.2. The sizes of the listed circuits vary from 0.336 mm<sup>2</sup> up to 3.6 mm<sup>2</sup>. All of the presented examples utilise GaAs pHEMT process and thus can be applied for the CCM role with little or no modification. It can be seen from the table that different figures of merit can be measured depending on the circuit class.

Low-noise amplifier's S-parameters including the gain are normally measured employing a network analyser, while noise figure analysers can be employed for noise parameter measurements. Similar setups are used in power amplifier testing. Mixer measurements usually use spectrum analysers to monitor a mixer performance connected to an LO. Oscillators can be measured using signal source analysers or spectrum analysers can be employed as well.

Low-noise amplifiers can be designed in a very compact way as shown by the comparison. Measurements of LNAs are also relatively simple. However, amplifiers from this class are normally designed to provide operation that is highly linear, therefore being still affected by process variation, these circuits may not be sensitive enough for the purposes of monitoring. More or less the same statements apply to the power amplifiers. Mixers, on the other hand, take advantage of active device nonlinear characteristics and tend to operate in the knee region of drain-to-source current versus drain-to-source voltage characteristic. On the other hand, mixers usually contain planar coupled-line baluns or CPW structures, which define the mixer operation, but not sensitive to process variations. Therefore for the purpose of a CCM, the area will

| Circuit                               | Size, mm <sup>2</sup> | Specifications                                        | Reference |

|---------------------------------------|-----------------------|-------------------------------------------------------|-----------|

| Two-Stage LNA and SP2T                | 0.916 x 0.95          | f = 5.4  GHz; G = 16  dB; NF = 2.1                    | [50]      |

| Switch RFIC FEM for WLAN              |                       | dB                                                    |           |

| 802.11a Application                   |                       |                                                       |           |

| Ultra Low-Power Q-Band <b>LNA</b>     | 2 x 1                 | f = 27–45 GHz; G = 25 dB; $NF$ $<$                    | [51]      |

|                                       |                       | $3.1~\mathrm{dB}$                                     |           |

| Ultrawideband 3–10 GHz <b>LNA</b>     | 1.5 x 1.4             | f= 3–10 GHz; $G=4$ dB; $NF<5$                         | [52]      |

| MMIC                                  |                       | dB                                                    |           |

| Compact LNA                           | 0.73 x 0.46           | f = 50–60 GHz; $G = 15.5$ dB; $NF <$                  | [53]      |

|                                       |                       | 3.3                                                   |           |

| 23-37 GHz Miniature MMIC Sub-         | $0.85 \times 0.85$    | f = 23-37 GHz; $CL = 9.4-12$ dB;                      | [54]      |

| harmonic <b>Mixer</b>                 |                       | LO = 13  dBm; P1dB = 6  dBm                           |           |

| 26–38 GHz Monolithic Doubly           | 1 x 2.1               | f = 26-38  GHz; CL = 5.4-10.7  dB;                    | [55]      |

| Balanced Mixer                        |                       | LO = 12  dBm; P1dB = 13  dBm                          |           |

| Novel 60-GHz Monolithic Star          | $1.5 \times 1.5$      | f = 50-75  GHz; C = 13-18  dB; LO                     | [56]      |

| Mixer                                 |                       | $=13~\mathrm{dBm};P1dB=3~\mathrm{dBm}$                |           |

| 5.25 GHz <b>PA</b> for 802.11a Appli- | $1.5 \pm 1.0$         | $f=5.25~\mathrm{GHz};G=25.6~\mathrm{dB};P1dB$         | [57]      |

| cation                                |                       | = 24.8  dBm                                           |           |

| Compact K-Band <b>PA</b> MMIC         | $2.23 \times 1.33$    | f= 17–24 GHz; $G=$ 20 dB; $P1dB$                      | [58]      |

| with Integrated ESD Protection        |                       | $=28~\mathrm{dBm}$                                    |           |

| C-Band MMIC Low Phase Noise           | $2.4 \times 1.5$      | $f = 7.3 \text{ GHz}; P_{OUT} = 14 \text{ dBm}; PN$   | [59]      |

| ${f VCO}$ for Space Applications      |                       | = -86  dBc/Hz                                         |           |

| Fully Integrated 2.4-GHz High         | 2 x 2                 | $f = 2.4 \text{ GHz}; P_{OUT} = 27 \text{ dBm}; PN =$ | [60]      |

| Efficiency Class-E <b>VCO</b>         |                       | $\text{-}118.33~\mathrm{dBc/Hz}$                      |           |

| Low Phase Noise Ka-Band <b>VCO</b>    | 1.3 x 0.8             | $f = 30.9 \text{ GHz}; P_{OUT} = 14 \text{ dBm}; PN$  | [61]      |

|                                       |                       | $= -116.36~\mathrm{dBc/Hz}$                           |           |

LNA: Low-Noise Amplifier, PA: Power Amplifier, VCO: Voltage-Controlled Oscillator

G: Gain, NF: Noise Figure, CL: Conversion Loss, LO: Local Oscillator, PN: Phase Noise

Table 2.2: Comparison of possible CCM candidates

be used inefficiently. Furthermore, both amplifiers and mixers need external signal sources for testing. Therefore their figures of merit will be defined not only by the device parameters but also by the measuring equipment.

Functional amplifiers are designed to be stable. A power amplifier can be stable

during a small-signal operation, but as the input power increases, unexpected oscillations, frequency divisions or continuous spectrum of high power may be observed. It was shown in [62] that a class-E power amplifier operated linearly at low powers. However with the input power increase the spectrum became continuous suggesting chaotic behaviour. Further power increase resulted in observation of normal spectrum. When the power was decreased chaotic performance was observed with no hysteresis, but with the further power decrease amplifier exhibited mixer-like spectrum. Amplifier instability can be utilised in the CCM. We know that chaotic systems are highly nonlinear and sensitive, therefore it is possible to design a PA or an LNA making it deliberately unstable.

Voltage-controlled oscillators are naturally nonlinear circuits. Their advantage over the aforementioned candidates is that they do not rely on any inputs during measurements apart from a DC bias or control voltage – oscillators are autonomous circuits. The disadvantage these circuits is that they contain resonators which can occupy a lot of space on the reticle, but do not contribute to the circuit's sensitivity.

As was mentioned, chaotic systems are very sensitive to initial conditions and values of their components. Chaotically behaving power amplifier can be a good candidate for a CCM, however rather complicated amplifier testing procedure makes this type of circuit less attractive. At the same time, there exists a class of oscillators, which are capable of generating chaotic signals. Oscillators do not need external signal sources during testing and only an oscilloscope can be used to measure their output.

Chaotic signals can not be characterised in terms of a 3 dB bandwidth or phase noise. Chaotic oscillators generate oscillations with a wide and continuous spectrum. As any chaotic system, chaotic oscillators are highly nonlinear and very sensitive circuits and that makes them good candidates for the role of a CCM. Besides, we trust, that a chaotic oscillator can be designed to be very compact.

## 2.4 Chaos Theory

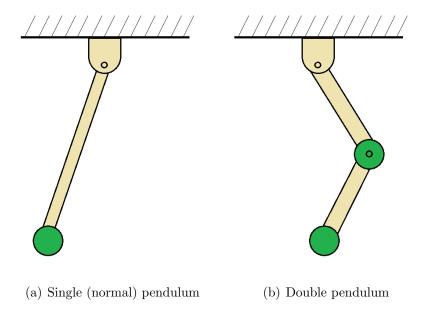

In our daily life when we say 'chaos' we mean something that does not follow any laws and completely lacks order. From the *mathematical* point of view, chaos is not completely random and can be described in formal terms. The main difference between a random behaviour and a chaotic system is that the latter follows some deterministic equations [63].

Many have heard the term 'butterfly effect'. It refers to the idea that a butterfly flapping its wings somewhere in Brazil and thus creating a small turbulence can cause a hurricane, say, in the Philippines. That idea was formulated by Edward Lorenz, the father of modern chaos theory.

Edward Lorenz, a meteorologist, had been developing a computer program simulating some weather patterns. The output of the program could be seen as a line graph. When Lorenz wanted to repeat some part of the simulations, he used a generated variable and rounded it. The printout indicated three decimal places in numbers instead of six, as computer had been storing them. He observed that the simulated results started to deviate quickly from previously obtained data. The tiny change transformed the whole pattern his program produced. Lorenz put his findings into a seminal paper which was titled "Deterministic Nonperiodic Flows" [64], published in 1963, where he elaborated on the sensitive dependence on initial conditions. Although, it was not instantly recognised, many researchers from the 1980s accepted that Lorenz's work challenged the classical understanding of nature [65].

Edward Lorenz is often called the father of modern chaos theory while emphasis on modern is given because he was not the first to describe a chaotic phenomena. French mathematician Henri Poincaré (1854-1912) discovered a chaotic deterministic system during his study of a three-body problem. He found that an evolution of a three-body system in space strongly depends on initial conditions, their positions and velocities. If we do not know the initial coordinates and velocities of the bodies to a very high precision we can not make accurate predictions about the final state. Thus Poincaré showed that determinism and predictability are two distinct problems [66].

2.4 Chaos Theory 23

Chaos theory works with nonlinear dynamical systems. A dynamical system is a system that changes over time, in other words, these systems evolve. In a linear system small perturbation in input results in small perturbation in the output. We can compare linear and nonlinear systems following the analysis performed in [67]. For example, let us take Newton's Second Law of Motion:

$$F_x(x,t) = ma = m\frac{d^2x}{dt^2}$$

(2.1)

We also know that for a point mass subject the force from an ideal spring is given by

$$F_x(x) = -kx (2.2)$$

where k is the spring constant and x is the displacement. We can combine these two equations to find the evolution equation for the position of a particle:

$$\frac{d^2x}{dt^2} = -\frac{k}{m}x\tag{2.3}$$

This equation is linear relative to x hence the described system is linear. If we displace the mass from the equilibrium position, it will oscillate around the equilibrium sinusoidally with an angular frequency

$$\omega = \sqrt{k/m} \tag{2.4}$$

If we take the case where spring's force depends on the square of the displacement, for example  $F = bx^2$ , then the evolution will be described by the following equation:

$$\frac{d^2x}{dt^2} = \frac{b}{m}x^2\tag{2.5}$$

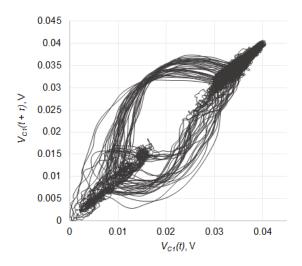

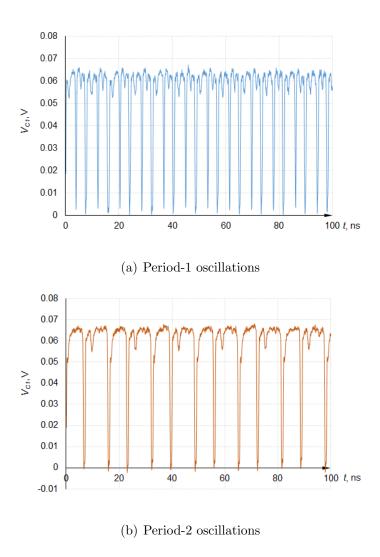

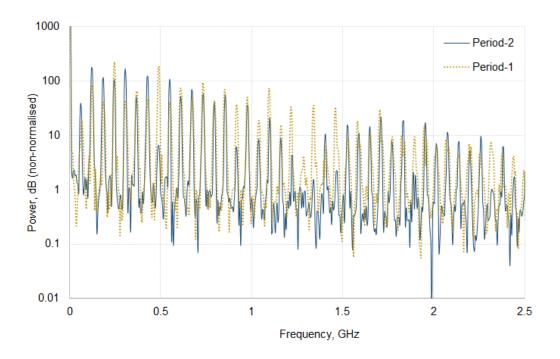

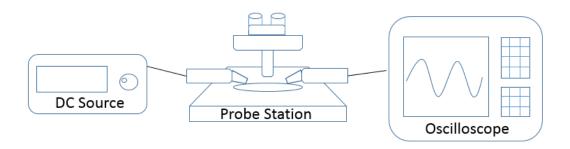

Here, x position appears in the equation squared, therefore the system is nonlinear.