# ELLIPTIC CURVE CRYPTOGRAPHIC PROTOCOLS: A SIMULATION AND IMPLEMENTATION OF ECDSA AND ECDH

#### Nathan Levett

Bachelor of Engineering with Bachelor of Science Computer Engineering, Mathematics

Department of Electronic Engineering Macquarie University

April 4, 2017

Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong

| Commission © 2017              | Nothern Legiste |

|--------------------------------|-----------------|

| Copyright © 2017  All Rights F |                 |

|                                |                 |

|                                |                 |

|                                |                 |

|                                |                 |

|                                |                 |

|                                |                 |

|                                |                 |

| DEPARTMENT APPROVAL  of a senior thesis submitted by  Nathan Levett  This thesis has been reviewed by the research advisor, research coordinator, as department chair and has been found to be satisfactory.  Date  Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong, Advisor                                |      |                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------|

| of a senior thesis submitted by  Nathan Levett  This thesis has been reviewed by the research advisor, research coordinator, at department chair and has been found to be satisfactory.  Date  Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator |      | MACQUARIE UNIVERSITY                                                                    |

| Nathan Levett  This thesis has been reviewed by the research advisor, research coordinator, a department chair and has been found to be satisfactory.  Date  Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator                                   |      | DEPARTMENT APPROVAL                                                                     |

| Nathan Levett  This thesis has been reviewed by the research advisor, research coordinator, a department chair and has been found to be satisfactory.  Date  Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator                                   |      |                                                                                         |

| This thesis has been reviewed by the research advisor, research coordinator, at department chair and has been found to be satisfactory.  Date  Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator                                                 |      | of a senior thesis submitted by                                                         |

| Date  Supervisor: Mr. MD Selim Hossain Supervisor: Dr. Yinan Kong, Advisor  Date  Department Ugrad Coordinator, Research Coordinator                                                                                                                                                                                    |      | Nathan Levett                                                                           |

| Date  Department Ugrad Coordinator , Research Coordinator                                                                                                                                                                                                                                                               |      |                                                                                         |

| Date Department Ugrad Coordinator , Research Coordinator                                                                                                                                                                                                                                                                |      |                                                                                         |

| nator                                                                                                                                                                                                                                                                                                                   | Date |                                                                                         |

| Date Department Chair Name, Chair                                                                                                                                                                                                                                                                                       | Date |                                                                                         |

|                                                                                                                                                                                                                                                                                                                         |      | Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator |

|                                                                                                                                                                                                                                                                                                                         | Date | Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator |

|                                                                                                                                                                                                                                                                                                                         | Date | Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator |

|                                                                                                                                                                                                                                                                                                                         | Date | Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator |

|                                                                                                                                                                                                                                                                                                                         | Date | Supervisor: Dr. Yinan Kong, Advisor  Department Ugrad Coordinator, Research Coordinator |

#### ACKNOWLEDGMENTS

I would like to acknowledge several fonts of inspiration and encouragement to pursue this thesis, and more largely, this degree. I would like to acknowledge Huawei for providing me the opportunity to be a part of their 2013 Winter Vacation to their Shenzhen campus, which inspired me to choose Computer Engineering as a major. I would also like to acknowledge the Macquarie University PACE Office, for funding my travel to, and participation in, the 2014 Winter Abroad "Digital System Design" unit taught in Changchun, Jilin, which inspired a deep appreciation for HDL's, which inspired half of this thesis. The other half of this thesis, reliant on Field Theory, causes thanks to be due to Dr Chris Cooper of the MQU Mathematics Department, for his inspirational teaching, and his courses and notes in Group, Ring, Field and Galois Theory, during his last semester teaching before retiring. I would also like to acknowledge and thank Dr Yinan Kong for making this possible, all the way from acting as an academic advisor prior to enrolling at MQU, through teaching the Computer Major stream, and designing the thesis goal for this, to suit my interest in computational applications of Galois Theory. Now is the appropriate time to also offer a shout-out to the mathematicians without whose work this area would not exist; Pioneer of Algebra - developer of Group Theory - Evariste Galois, masters of Elliptic Functions - Carl Gustav Jacob Jacobi and Karl Weierstrass, number theorists -Euclid, Etienne Bezout and Pierre de Fermat.

#### ABSTRACT

Elliptic Curve Cryptography provides a secure means of implementing the Digitial Signature Algorithm protocol through the Elliptic Curve Digitial Signature Algorithm scheme. The ECDSA upholds the data security objectives of information authentication and non-reputability. Similarly, the Elliptic Curve Diffie-Hellman upholds information confidentiality and information integrity. These schemes, whilst theoretically cryptographically secure, are expensive to implement up to certain security standards, with timeliness and size of circuit required to perform either scheme being the main considerations. To have any appreciable speed, they must be implemented in digital hardware design. This project outlines the design methodology and procedure of simulating a generalisable implementation of an Elliptic Curve Cryptographic Processor, able to effectively utilise both the ECDH and ECDSA, over any chosen bit length.

# Contents

| Abstract                                              |  |  |   | ix   |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|--|--|---|------|--|--|--|--|--|--|--|--|--|--|

| Table of Contents                                     |  |  |   | xi   |  |  |  |  |  |  |  |  |  |  |

| List of Figures                                       |  |  |   | xv   |  |  |  |  |  |  |  |  |  |  |

| List of Tables                                        |  |  | X | cvii |  |  |  |  |  |  |  |  |  |  |

| 1 Introduction                                        |  |  |   |      |  |  |  |  |  |  |  |  |  |  |

| 1.1 Project Overview                                  |  |  |   | 1    |  |  |  |  |  |  |  |  |  |  |

| 1.1.1 Pretext: Cryptography in its Historical Context |  |  |   | 1    |  |  |  |  |  |  |  |  |  |  |

| 1.1.2 Context: Elliptic Curve Cryptography            |  |  |   | 2    |  |  |  |  |  |  |  |  |  |  |

| 1.2 Project Goals                                     |  |  |   | 2    |  |  |  |  |  |  |  |  |  |  |

| 1.3 Project Philosophy and Constraints                |  |  |   | 3    |  |  |  |  |  |  |  |  |  |  |

| 1.4 Overview of Chapters                              |  |  |   | 4    |  |  |  |  |  |  |  |  |  |  |

| 1.4.1 Chapter 2: Topic Background                     |  |  |   | 5    |  |  |  |  |  |  |  |  |  |  |

| 1.4.2 Chapter 3: Mathematical Background              |  |  |   | 5    |  |  |  |  |  |  |  |  |  |  |

| 1.4.3 Chapter 4: Modelling ECC Protocols              |  |  |   | 5    |  |  |  |  |  |  |  |  |  |  |

| 1.4.4 Chapter 5: VHDL Implementation                  |  |  |   | 6    |  |  |  |  |  |  |  |  |  |  |

| 1.4.5 Chapter 6: VHDL Simulation                      |  |  |   | 6    |  |  |  |  |  |  |  |  |  |  |

| 1.4.6 Chapter 7: Future Work                          |  |  |   | 6    |  |  |  |  |  |  |  |  |  |  |

| 2 Topic Background                                    |  |  |   | 7    |  |  |  |  |  |  |  |  |  |  |

| 2.1 Chapter Introduction                              |  |  |   | 7    |  |  |  |  |  |  |  |  |  |  |

| 2.2 Elliptic Curves                                   |  |  |   | 7    |  |  |  |  |  |  |  |  |  |  |

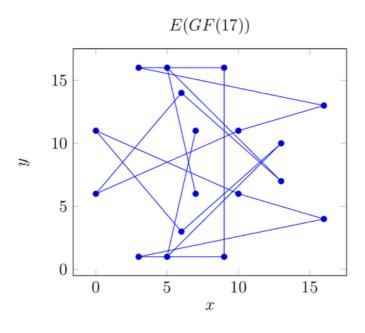

| 2.2.1 Elliptic Curves on Prime Fields                 |  |  |   | 8    |  |  |  |  |  |  |  |  |  |  |

| 2.2.2 Elliptic Curves on Binary Fields                |  |  |   | 8    |  |  |  |  |  |  |  |  |  |  |

| 2.3 Elliptic Curve Cryptographic Protocols            |  |  |   | 10   |  |  |  |  |  |  |  |  |  |  |

| 2.3.1 Cryptographically Secure Pseudo RNG             |  |  |   | 10   |  |  |  |  |  |  |  |  |  |  |

| 2.3.2 Elliptic Curve Diffie Hellman                   |  |  |   | 11   |  |  |  |  |  |  |  |  |  |  |

| 2.3.3 Elliptic Curve Digital Signature Algorithm      |  |  |   | 12   |  |  |  |  |  |  |  |  |  |  |

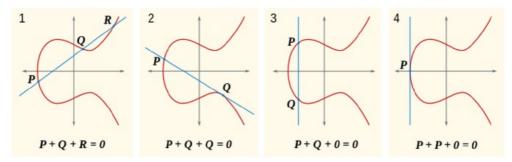

| 2.4 Elliptic Curve Primitives: Point Operations       |  |  |   | 13   |  |  |  |  |  |  |  |  |  |  |

xii CONTENTS

|   |     | 2.4.1 Point Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

|   |     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 |

|   | 2.5 | 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

|   | 2.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

| 3 | Mat | thematical Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21 |

|   | 3.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21 |

|   | 3.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21 |

|   |     | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

|   | 3.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25 |

|   | 3.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

|   | 3.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

|   |     | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35 |

|   | 3.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37 |

| 4 | Mod | delling ECC Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

|   | 4.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

|   | 4.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

|   |     | o a constant of the constant o | 39 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44 |

|   |     | 4.2.5 FAP: Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

|   | 4.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46 |