## EFFICIENT FPGA IMPLEMENTATION OF ELLIPTIC CURVE SCALAR MULTIPLICATION OVER THE BINARY FIELD

Kuntapong Ruangsantikorakul

Bachelor of Engineering Computer Engineering

Department of Electronic Engineering Macquarie University

November, 2016

Supervisor: Dr. Yinan Kong Co-supervisor: Md. Selim Hossain

| ACKNOWLEDGMENTS                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| I would like to acknowledge and thank my supervisors Dr. Yinan Kong and Selim                                                              |

| Hossain for their constant encouragement, enthusiasm, and guidance throughout my studies this past year and especially with this research. |

| my settles this past year and especially with this research.                                                                               |

| I would also like to acknowledge my mother and father for their endless sup-                                                               |

| port just for me to receive a high level of education and take great opportunities                                                         |

| that they wish they had themselves.                                                                                                        |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

|                                                                                                                                            |

STATEMENT OF CANDIDATE

I, Kuntapong Ruangsantikorakul, declare that this report, submitted as part of

the requirement for the award of Bachelor of Engineering in the Department of

Electronic Engineering, Macquarie University, is entirely my own work unless

otherwise referenced or acknowledged. This document has not been submitted

for qualification or assessment at any academic institution.

Student's Name: Kuntapong Ruangsantikorakul

Student's Signature: Kuntapong Ruangsantikorakul (electronic)

Date:  $1^{st}$  September, 2016

#### ABSTRACT

Elliptic curve cryptography (ECC) is the more efficient alternative to the widely used Ron Rivest, Adi Shamir and Leonard Adleman (RSA) cryptosystem since 283-bit ECC provides the same security per bit as 3072-bit RSA. This makes it useful for resource constrained portable devices since smaller operands can be used. For practical use of ECC, an efficient hardware implementation must be achieved in terms of area and time. Elliptic curve scalar multiplication (ECSM) is the crucial operation required for ECC processors. The goal of this research is for the implementation of area efficient and high-speed ECSM over a binary field in field-programmable gate array (FPGA) technology for the binary fields  $GF(2^{233})$  and  $GF(2^{283})$ . In order to achieve an efficient implementation of ECSM, the trade-off between area and time for two types of multipliers with various digit sizes was examined so that the most efficient hardware design can be achieved. Traditional digit-serial multipliers have the computational time complexity of  $\lceil m/d \rceil$  clock cycles while the modified digit-serial multipliers had a time complexity of  $2\lceil \sqrt{m/d} \rceil + 1$  clock cycles for the digit-size d. The comparison of affine coordinates and Jacobian coordinates were also analysed, which revealed that an implementation in affine coordinates is up to 13 times slower than that in Jacobian coordinates. In this research the efficient hardware implementation of ECSM on the Virtex-6 (XC6VLX760-2ff1760) FPGA device in  $GF(2^{233})$  takes 16,048 clock cycles, has the computation time of  $64.72\mu$ s, and occupies 35,615slices. ECSM in the binary field  $GF(2^{283})$  is performed in 13,565 clock cycles in  $63.61\mu$ s, and occupies 69,908 slices on the same device.

## Contents

| A  | cknov              | wledgn                  | nents                                | iii    |

|----|--------------------|-------------------------|--------------------------------------|--------|

| Αl | bstra              | $\mathbf{ct}$           |                                      | vii    |

| Ta | able o             | of Con                  | tents                                | ix     |

| Li | st of              | Figure                  | es :                                 | xiii   |

| Li | st of              | Tables                  | 3                                    | vii    |

| 1  | <b>Intr</b><br>1.1 | <b>oducti</b><br>Projec | on<br>t Scope                        | 1<br>2 |

| 2  | Bac                | kgrour                  | nd and Related Work                  | 5      |

|    | 2.1                | _                       | c Curve Cryptography                 | 5      |

|    | 2.2                | Galois                  | Field Arithmetic                     | 6      |

|    |                    | 2.2.1                   | Addition over the Binary Field       | 6      |

|    |                    | 2.2.2                   | Squaring over the Binary Field       | 6      |

|    |                    | 2.2.3                   | Multiplication over the Binary Field | 7      |

|    |                    | 2.2.4                   | Inversion over the Binary Field      | 7      |

|    | 2.3                | Ellipti                 | c Curve Scalar Multiplication        | 7      |

|    |                    | 2.3.1                   | Elliptic Curve Group Operations      | 7      |

|    |                    | 2.3.2                   | Affine Coordinates                   | 8      |

|    |                    | 2.3.3                   | Jacobian Coordinates                 | 9      |

|    | 2.4                | Relate                  | d Work                               | 11     |

| 3  | Exp                | erime                   | ntal Procedures                      | 13     |

|    | 3.1                | Resour                  | rces                                 | 13     |

|    | 3.2                | Experi                  | imental Procedures                   | 13     |

|    |                    | 3.2.1                   | Algorithm selection                  | 15     |

|    |                    | 3.2.2                   | Logic Modeling                       | 15     |

|    |                    | 3.2.3                   | VHDL coding                          | 16     |

|    |                    | 3.2.4                   | Syntax and behavioral verification   | 16     |

|    |                    | 3.2.5                   | Testing and waveform simulations     | 16     |

x CONTENTS

|   |     | 3.2.6 $3.2.7$ | Synthesis                                                        | 16<br>16 |

|---|-----|---------------|------------------------------------------------------------------|----------|

|   |     | 3.2.1         | Comparison and analysis of nardware designs                      | 10       |

| 4 | Har | dware         | for Galois field arithmetic over $GF(2^m)$                       | 17       |

|   | 4.1 |               | and implementation of Galois field arithmetic over binary fields | 18       |

|   |     | 4.1.1         | Addition over binary fields                                      | 18       |

|   |     | 4.1.2         | Multiplication in $GF(2^m)$                                      | 19       |

|   |     | 4.1.3         | Inversion in $GF(2^m)$                                           | 25       |

|   | 4.2 | Simula        | ation results for Galois field arithmetic                        | 29       |

|   |     | 4.2.1         | Testing of traditional digit-serial multipliers                  | 30       |

|   |     | 4.2.2         | Testing of binary field inversion                                | 30       |

| 5 | Har | dware         | for ECSM over $GF(2^m)$                                          | 35       |

|   | 5.1 |               | and Implementation of affine ECSM                                | 36       |

|   |     | 5.1.1         | Affine Elliptic Curve Point Doubling                             | 38       |

|   |     | 5.1.2         | Affine Elliptic Curve Point Addition                             | 38       |

|   |     | 5.1.3         | Affine Elliptic Curve Point Multiplication                       | 38       |

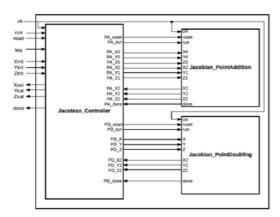

|   | 5.2 | Design        | and implementation of Jacobian ECSM                              | 42       |

|   |     | 5.2.1         | Jacobian Elliptic Curve Point Doubling                           | 42       |

|   |     | 5.2.2         | Jacobian Elliptic Curve Point Addition                           | 43       |

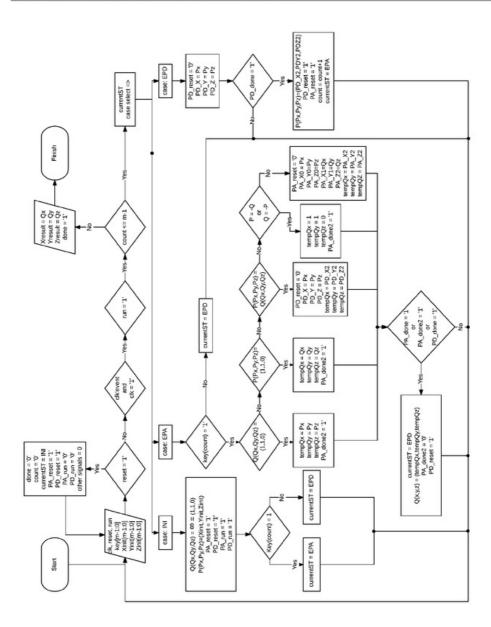

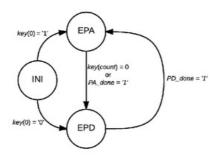

|   |     | 5.2.3         | Jacobian Elliptic Curve Point Multiplication                     | 44       |

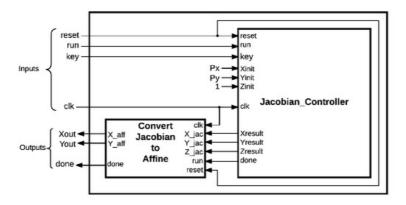

|   | 5.3 | FPGA          | implementation of ECSM                                           | 49       |

|   | 5.4 | Simula        | ations for ECSM over binary fields                               | 50       |

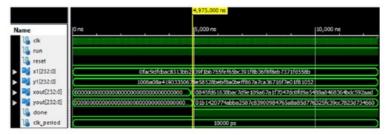

|   |     | 5.4.1         | Testing of ECSM over $GF(2^{233})$                               | 50       |

| 6 | Opt | imised        | ECC operations in $GF(2^m)$                                      | 57       |

|   | 6.1 | Modfie        | ed Binary Field Multiplication                                   | 57       |

|   |     | 6.1.1         | Design and implementation of modified multipliers                | 57       |

|   |     | 6.1.2         | Simulation of modified multipliers                               | 61       |

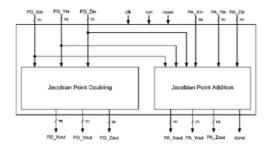

|   | 6.2 | Binary        | field Elliptic Curve Group Operations                            | 64       |

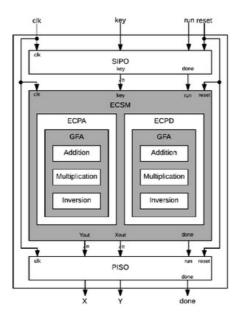

|   |     | 6.2.1         | Concurrent ECPA and ECPD                                         | 64       |

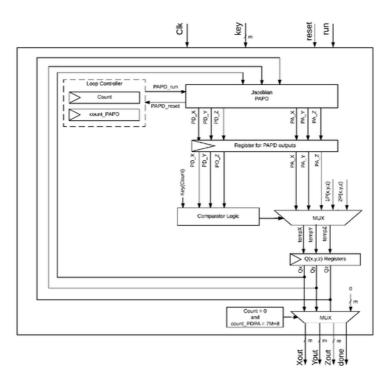

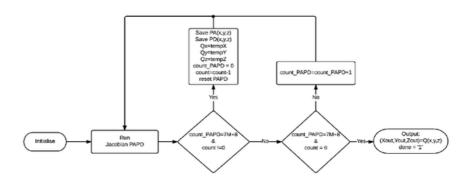

|   |     | 6.2.2         | Optimised Jacobian ECSM                                          | 66       |

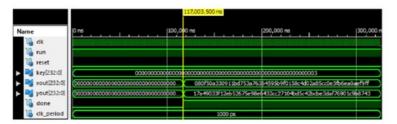

|   |     | 6.2.3         | Simulations for ECSM optimisations                               | 70       |

| 7 | Res | ults an       | nd discussion of ECC operations                                  | 73       |

|   | 7.1 | Result        | s for Galois Field Arithmetic in $GF(2^m)$                       | 73       |

|   |     | 7.1.1         | Inversion                                                        | 73       |

|   |     | 7.1.2         | Traditional Digit-Serial Multipliers                             | 73       |

|   |     | 7.1.3         | Modified Digit-Serial Multipliers                                | 74       |

|   |     | 7.1.4         | Comparison of multipliers                                        | 74       |

|   | 7.2 | Compa         | arison of ECSM hardware implementations over $GF(2^m)$           | 79       |

| CO         | ONTENTS                                                               | xi              |

|------------|-----------------------------------------------------------------------|-----------------|

| 8          | Conclusions and Future Work  8.1 Conclusions                          |                 |

| 9          | Abbreviations                                                         | 85              |

| A          | NIST curves for the binary field $GF(2^{233})$ and $GF(2^{283})$      | 87              |

| В          | Supervisor Consultations  B.1 Supervisor Consultation Attendance Form | <b>89</b><br>90 |

| $_{ m Bi}$ | bliography                                                            | 90              |

## List of Figures

| $\frac{2.1}{2.2}$ | Hierarchy of operations for elliptic curve cryptography Point addition $(P+Q)$ and point doubling $(2P)$ on an elliptic curve [20]                                                                                                   | 5<br>8 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 3.1               | Simplified top-level model for the ECSM architecture in FPGA                                                                                                                                                                         | 14     |

| 4.1               | The top level block diagrams of Addition, Multiplication, Squaring and Inversion.                                                                                                                                                    | 18     |

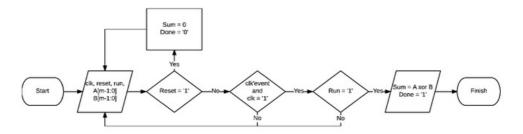

| 4.2               | Flowchart for the addition module                                                                                                                                                                                                    | 19     |

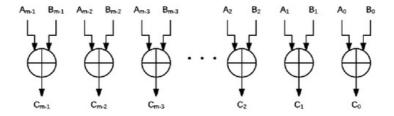

| 4.3               | Hardware design for addition over the binary field                                                                                                                                                                                   | 19     |

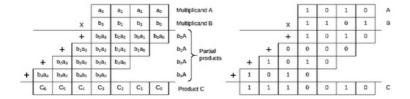

| 4.4               | General method for Galois field multiplication where an $m$ -bit multiplier and multiplicand will produce $m$ partial products and the product will have a size of $2m$ -1 bits. An example is given for the multiplication of 4-bit | 20     |

| 4.5               | binary numbers $1010_2$ and $1101_2$                                                                                                                                                                                                 | 20     |

|                   | $10011_2 = 0001_2$                                                                                                                                                                                                                   | 21     |

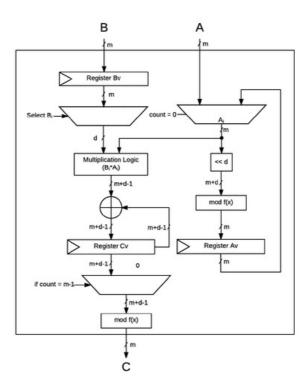

| 4.6               | Block diagram for multiplication of $m$ -bit binary polynomials where the                                                                                                                                                            |        |

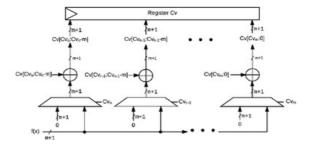

|                   | product $C = A \cdot B \mod f(x)$                                                                                                                                                                                                    | 23     |

| 4.7               | Block diagram for the reduction of a binary polynomial greater than $m$ -bits                                                                                                                                                        |        |

|                   | used to perform " $mod\ f(x)$ " during multiplication                                                                                                                                                                                | 23     |

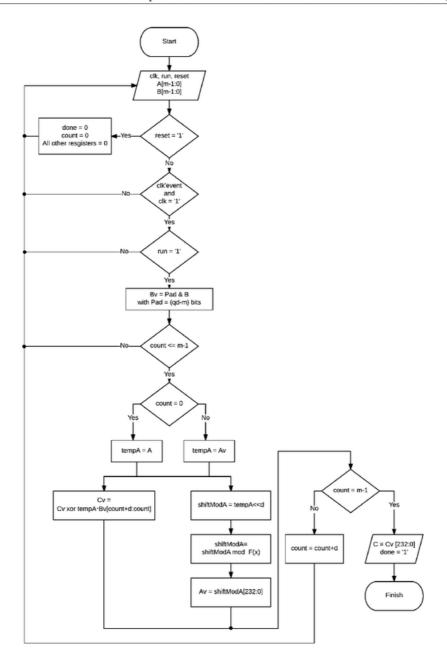

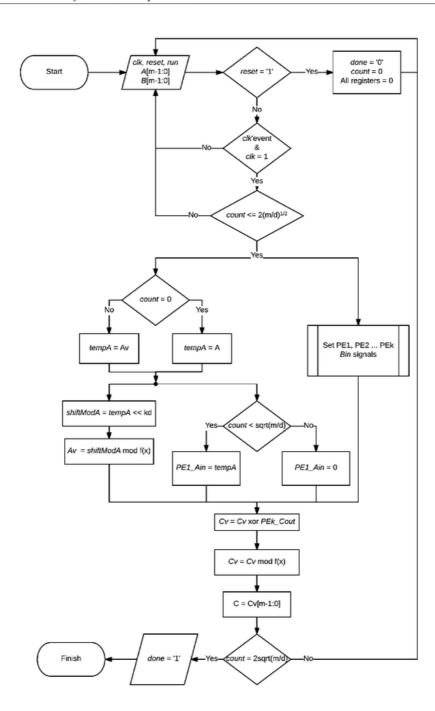

| 4.8               | Flowchart for the implementation of $m$ -bit digit-serial multiplication with                                                                                                                                                        |        |

|                   | digit size $d$                                                                                                                                                                                                                       | 24     |

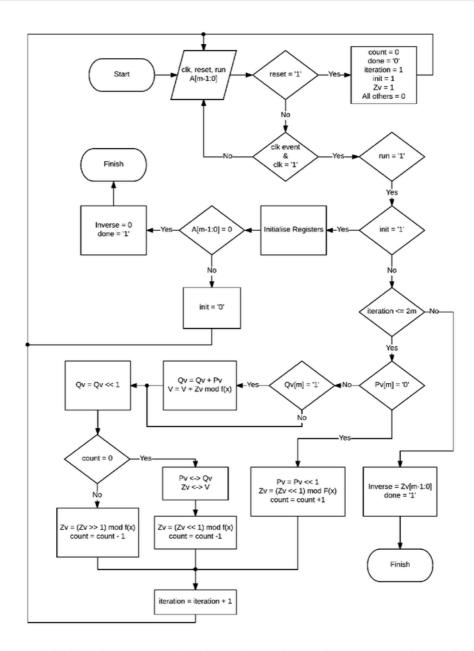

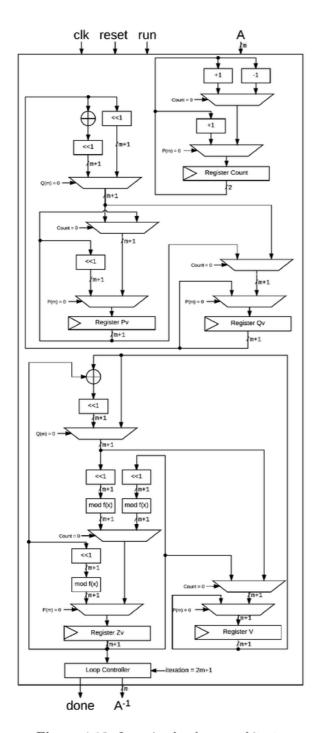

| 4.9               | Flowchart representing the hardware design of inversion over binary fields.                                                                                                                                                          | 27     |

| 4.10              | Inversion hardware architecture                                                                                                                                                                                                      | 28     |

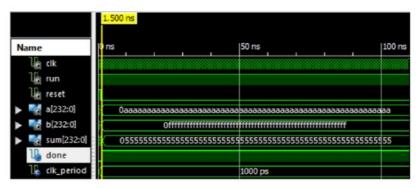

| 4.11              | The ISim simulation for the addition module in $GF(2^{233})$                                                                                                                                                                         | 29     |

| 4.12              | The ISim simulation for the addition module in $GF(2^{283})$                                                                                                                                                                         | 29     |

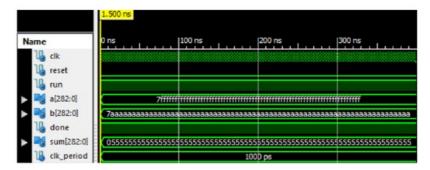

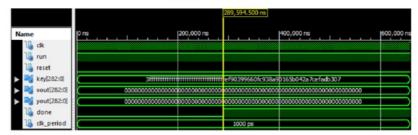

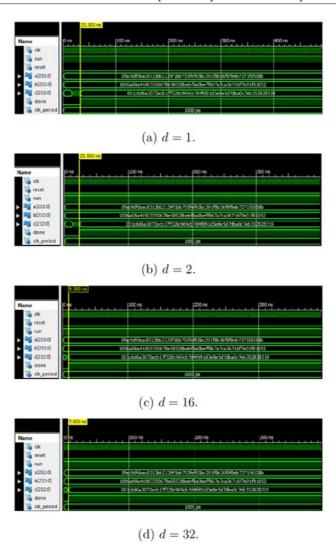

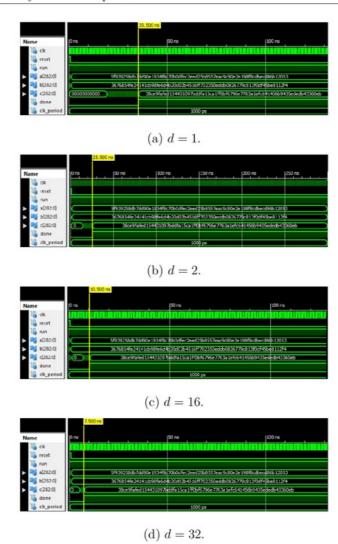

|                   | The simulations for traditional digit-serial multiplication with $d = 1, 2, 32$ , and 64 in $GF(2^{233})$                                                                                                                            | 31     |

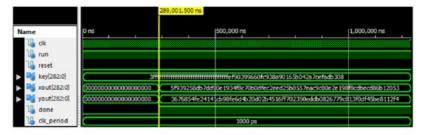

| 4.14              | The ISim simulations for the traditional digit-serial multiplication from top                                                                                                                                                        |        |

|                   | to bottom with $d = 1, 2, 4, 8, 16$ and 32 in in $GF(2^{283})$                                                                                                                                                                       | 32     |

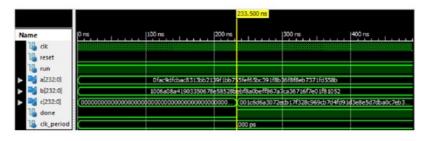

| 4.15              | The simulation for inversion in $GF(2^{233})$                                                                                                                                                                                        | 33     |

xiv LIST OF FIGURES

| 4.16 | The simulation result for multiplication of a binary polynomial and its inverse in $GF(2^{233})$                                                                                                                                                                                                                                                                             | 33 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.17 | The simulation for inversion in $GF(2^{283})$                                                                                                                                                                                                                                                                                                                                | 33 |

| 4.10 | The simulation for multiplication of a binary polynomial and its inverse in $GF(2^{283})$                                                                                                                                                                                                                                                                                    | 33 |

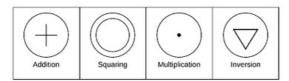

| 5.1  | Symbols used to represent addition, multiplication, squaring and inversion modules                                                                                                                                                                                                                                                                                           | 36 |

| 5.2  | Scheduling of sequential finite field operations and the connections between                                                                                                                                                                                                                                                                                                 |    |

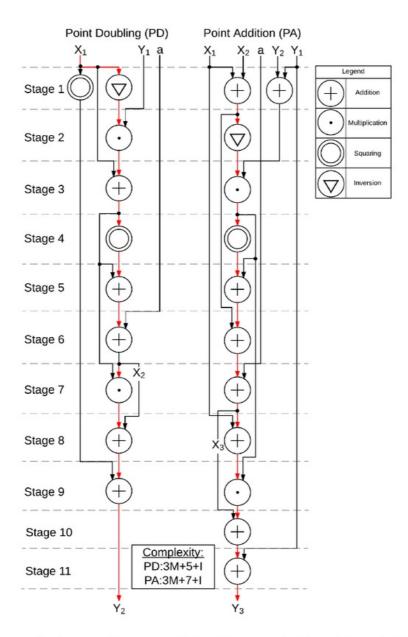

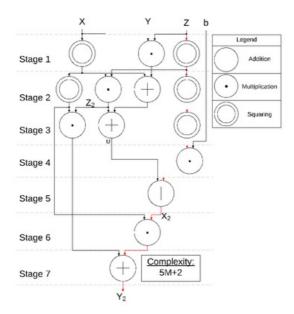

| 5.3  | each module. An example for two squaring operations is shown Hardware architecture used for affine point doubling (left) and affine point addition (right). The critical path for each is shown by the red arrow. The complexity shown is in terms of clock cycles where $M$ is the clock cycles to perform a single multiplication and $I$ is the clock cycles to perform a | 36 |

| 5.4  | single inversion                                                                                                                                                                                                                                                                                                                                                             | 37 |

| 5.5  | ECSM                                                                                                                                                                                                                                                                                                                                                                         | 40 |

| 5.6  | troller in $GF(2^m)$                                                                                                                                                                                                                                                                                                                                                         | 41 |

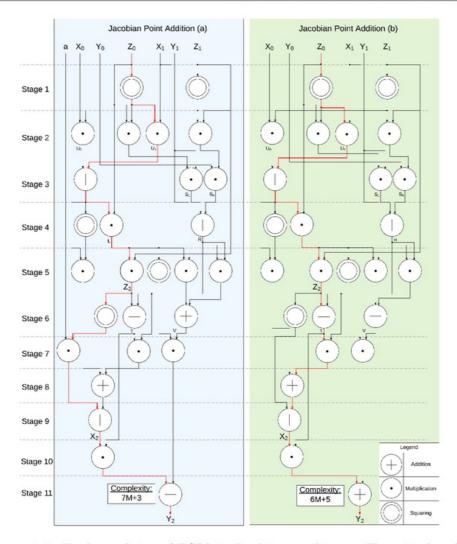

| 5.7  | shown by red wiring. The complexity given is in terms of clock cycles where $M$ is the clock cycles required for a single multiplication Hardware design of ECPA in Jacobian coordinates. The critical path is                                                                                                                                                               | 43 |

| 5.8  | shown in red. The complexity given is in terms of clock cycles where $M$ is the number of clock cycles to perform one multiplication                                                                                                                                                                                                                                         | 44 |

| 5.9  | scalar multiplication                                                                                                                                                                                                                                                                                                                                                        | 46 |

|      | nates                                                                                                                                                                                                                                                                                                                                                                        | 47 |

|      | State diagram used in the Jacobian controller                                                                                                                                                                                                                                                                                                                                | 48 |

| 5.12 | affine coordinates once point multiplication has completed                                                                                                                                                                                                                                                                                                                   | 48 |

|      | to affine coordinates using Galois field operations                                                                                                                                                                                                                                                                                                                          | 49 |

|      | an FPGA device                                                                                                                                                                                                                                                                                                                                                               | 50 |

|      | The simulation for $GF(2^{233})$ ECPD using affine coordinates                                                                                                                                                                                                                                                                                                               | 51 |

|      | The simulation for $GF(2^{233})$ ECPA using affine coordinates                                                                                                                                                                                                                                                                                                               | 51 |

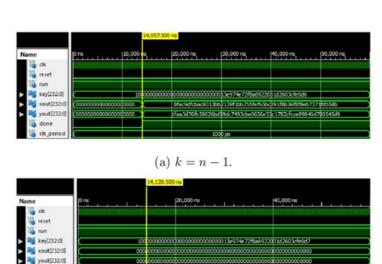

|      | The simulation for ECSM using affine coordinates with $k = 3$ in in $GF(2^{233})$ .<br>The ISim simulations for ECSM using affine coordinates with $k = n - 1$ ,                                                                                                                                                                                                             | 52 |

|      | $n$ , and $n + 1$ in $GF(2^{233})$                                                                                                                                                                                                                                                                                                                                           | 52 |

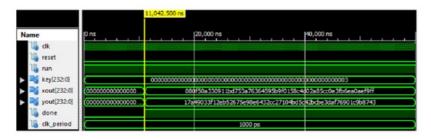

| 5.18 | Simulation results for Jacobian point doubling in $GF(2^{233})$                                                                                                                                                                                                                                                                                                              | 53 |

|      | Simulation results for Jacobian point addition in $GF(2^{233})$                                                                                                                                                                                                                                                                                                              |    |

LIST OF FIGURES xv

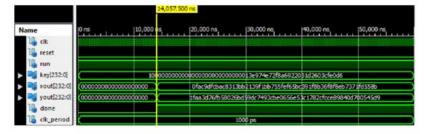

| 5.20         | The simulations for ECSM using Jacobian coordinates with $k=3$ in in $GF(2^{233})$                                                                                                                      | 53       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.21         | Simulation results for the serial output of Jacobian ECSM with $k=3$ in $GF(2^{233})$                                                                                                                   | 54       |

| 5.22         |                                                                                                                                                                                                         | 54       |

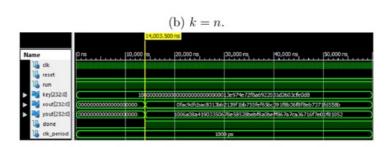

| 5.23<br>5.24 | The simulations for affine ECSM with $k = n - 1, n$ , and $n + 1$ in $GF(2^{283})$ . The simulations for Jacobian ECSM with $k = n - 1, n$ , and $n + 1$ in in $GF(2^{283})$ .                          | 55<br>56 |

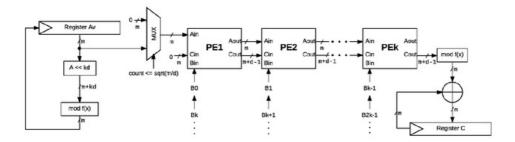

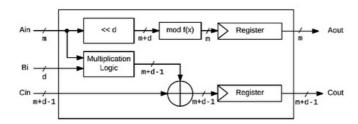

| $6.1 \\ 6.2$ | Modified digit-serial multiplier hardware architecture                                                                                                                                                  | 58       |

| 6.3          | multiplier                                                                                                                                                                                              | 58       |

| 6.4          | serial multiplier                                                                                                                                                                                       | 59       |

| 6.5          | 16, and 32 in in $GF(2^{233})$                                                                                                                                                                          | 62       |

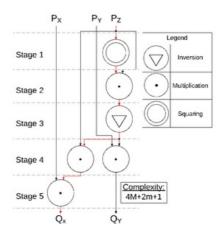

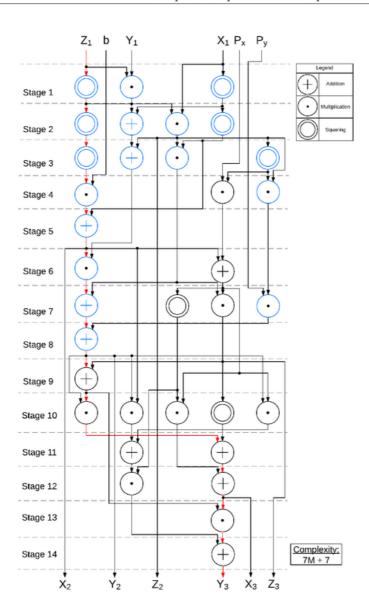

| 6.6          | 16, and 32 in $GF(2^{283})$                                                                                                                                                                             | 63<br>65 |

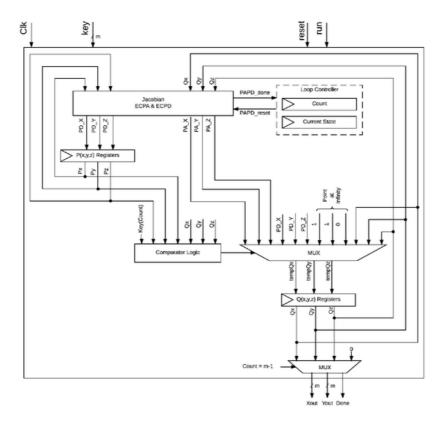

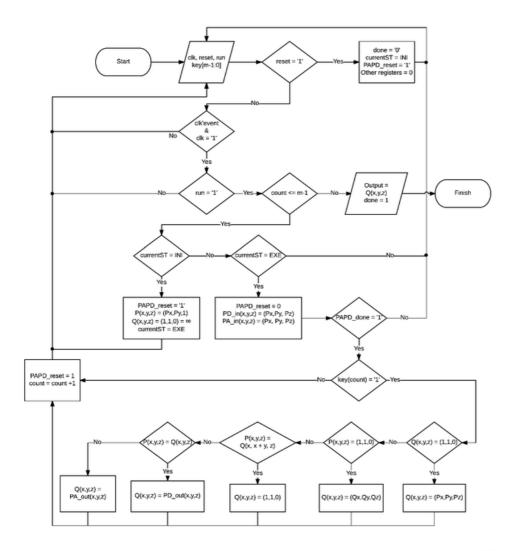

| 6.7<br>6.8   | Hardware architecture for concurrent ECSM using the "double-and-add" algorithm in Jacobian coordinates                                                                                                  | 65       |

| 6.9          | using Jacobian coordinates                                                                                                                                                                              | 66       |

| 6.10<br>6.11 | addition                                                                                                                                                                                                | 68<br>69 |

| 0.11         | temporary values which update registers $Q(x, y, z)$ is shown by the conditions in table 6.3                                                                                                            | 69       |

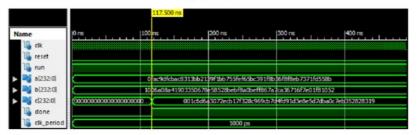

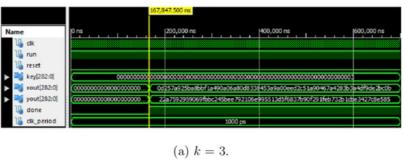

| 6.13         | Simulation results for concurrent Jacobian ECSM with $k=3$ Simulation results for concurrent Jacobian ECSM with $k=n-1$ Simulation results for Jacobian ECSM using the PAPD module with $k=1$           | 70<br>70 |

| 6.15         | n-1.                                                                                                                                                                                                    | 70<br>71 |

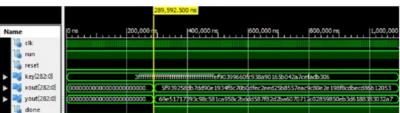

|              | Simulation results for concurrent Jacobian ECSM with $k=n$ -1 Simulation results for Jacobian ECSM using the PAPD module with $k=n$ -1                                                                  | 71<br>71 |

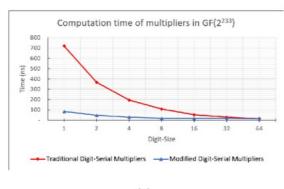

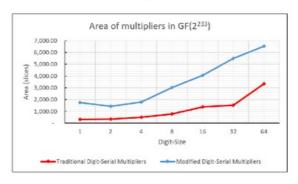

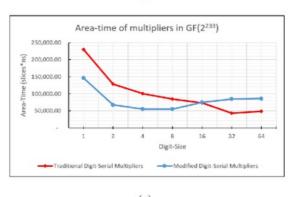

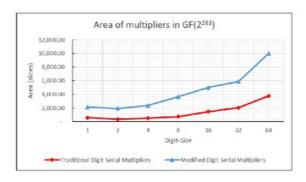

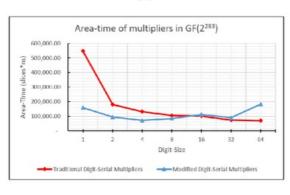

| 7.1          | Comparison of traditional and modified digit-serial multipliers with various digit-sizes in $GF(2^{233})$ . (a) shows the computation time, (b) shows the slices occupied, and (c) shows the area-time. | 77       |

| xvi | LIST OF FIGURES |

|-----|-----------------|

|     |                 |

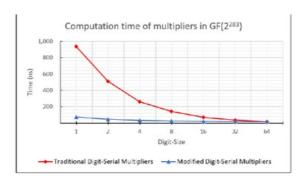

| 7.2 | Comparison of traditional and modified digit-serial multipliers with various digit-sizes in $GF(2^{283})$ . (a) shows the computation time, (b) shows the slices occupied, and (c) shows the area-time | 78 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A.1 | The NIST recommended random and Koblitz curves and parameters for the binary field $GF(2^{233})$ and $GF(2^{283})$ [7]                                                                                 | 87 |

| B.1 | Attendance sheet for the weekly consultation meetings with the supervisor.                                                                                                                             | 90 |

|     |                                                                                                                                                                                                        |    |

## List of Tables

| 1.1 | Comparison of security levels per bit in cryptosystems                                                                                                      | 2        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1 | Comparison of operations required for point addition and point doubling in affine coordinates and Jacobian coordinates                                      | 8        |

| 2.2 | Clock cycles of binary field operations using bit-serial multiplication and the modified extended Euclidean algorithm.                                      | 11       |

| 4.1 | Registers used for $GF(2^m)$ traditional digit-serial multiplication                                                                                        | 21       |

| 4.2 | Summary of register operations required when performing inversion                                                                                           | 25       |

| 4.3 | Clock cycles for 233-bit traditional digit-serial multipliers                                                                                               | 30       |

| 4.4 | Clock cycles for 283-bit traditional digit-serial multipliers                                                                                               | 30       |

| 5.1 | Summary of conditions and their corresponding results when performing point addition where $Q$ and $P$ are points                                           | 39       |

| 6.1 | The scheduling of $Bin$ inputs for each processing element in $GF(2^{233})$ when $d=8$                                                                      | 60       |

| 6.2 | The number of processing elements (PEs) and clock cycles for each digit-<br>size implemented in $GF(2^{233})$ and $GF(2^{283}, \dots, \dots, \dots, \dots)$ | 61       |

| 6.3 | The conditions for ECPA which determine the next values for the registers                                                                                   | 67       |

|     | representing $Q(x, y, z)$                                                                                                                                   | 67       |

| 7.1 | Synthesis results for inversion in $GF(2^{233})$ and $GF(2^{283})$                                                                                          | 73       |

| 7.2 | Synthesis results for the 233-bit implementation of traditional digit-serial                                                                                | 75       |

| 7.3 | multipliers                                                                                                                                                 | 75<br>75 |

| 7.4 | Synthesis results for the 283-bit implementation of traditional digit-serial                                                                                | 10       |

| 1.4 | multipliers                                                                                                                                                 | 75       |

| 7.5 | Synthesis results for the 283-bit modified digit-serial multipliers                                                                                         | 76       |

| 7.6 | Synthesis results for the ECSM over the binary field $GF(2^{233})$                                                                                          | 76       |

| 7.7 | Synthesis results for the ECSM over the binary field $GF(2^{283})$                                                                                          | 76       |

| 7.8 | Synthesis results for the most efficient ECSM over the binary field $GF(2^{233})$                                                                           |          |

|     | and $GF(2^{283})$ with serial inputs and outputs                                                                                                            | 79       |

| xviii | LIST OF TABLES                                                                                                                                                                                                                                                                                        |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7.9   | Summary of latencies for each operation involved in ECC where $m$ is the bit-size of the binary field, $M$ is the clock cycles required to perform one multiplication by either traditional digit-serial multiplication or the modified digit-serial multiplication, and $d$ is the chosen digit-size |  |

| 7.10  | Comparison of the ECSM implementations with other work 82                                                                                                                                                                                                                                             |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

|       |                                                                                                                                                                                                                                                                                                       |  |

## Chapter 1

## Introduction

Cryptography consists of techniques used to secure information on public communication networks from adversaries. There are many schemes used for encryption, decryption and digital signatures which vary in security and complexity. These schemes are separated into private-key and public-key cryptography. Private-key cryptosystems use identical keys for both the receiver and the sender. Public key cryptosystems use two asymmetric keys where a private key is derived from a public key. Elliptic Curve Cryptography (ECC) is a public-key cryptography approach introduced by Miller [14] and Koblitz [10] in 1985.

ECC is an alternative to the widely used Ron Rivest, Adi Shamir and Leonard Adleman (RSA) cryptosystem [21]. ECC provides high levels of security per bit such that 256-bit ECC provides the same level of security as 3072-bit RSA. This allows significantly smaller key sizes which are favourable for portable devices to protect data with their limited resources. For ECC to be used in practical applications, the implementation of ECC must be efficient in terms of speed, area, and power. The focus of this research is to achieve an area-efficient, high-speed hardware implementation of Elliptic Curve Scalar Multiplication (ECSM) (also known as Elliptic Curve Point Multiplication (ECPM)) over a binary field using Field-Programmable Gate Array (FPGA) technology which can then be used for ECC protocols. ECC Protocols such as the Elliptic Curve Diffie-Hellman (ECDH) and Elliptic Curve Digital Signature Algorithm (ECDSA) requires the computation of a point on a defined elliptic curve where it is infeasible to derive the private key from this point due to the elliptic curve discrete logarithm problem (ECDLP).

The main advantage of ECC over RSA is that it is computationally more efficient, useful in portable devices, and shorter operands can be used during computation. A summary comparing the Advanced Encryption Standard (AES), ECC, and RSA is shown in table 1.1 [17]. 3072-bit RSA is shown to achieve the same security level as 128-bit AES since there are lots of attacks available, so more bits are required. Although 3072-bit RSA can still be used, it is inefficient for practical use. This is where ECC is useful since the best attack used on ECC is much harder compared to RSA.

An implementation in hardware will produce results that are at least 37 times faster than software implementations of ECC [16]. An implementation in hardware also allows for modulo-2 arithmetic required for binary field operations to be efficiently implemented.

| Cryptosystem        | Equivalent Security Size |      |      |      |       |

|---------------------|--------------------------|------|------|------|-------|

| AES (symmetric key) | 80                       | 112  | 128  | 192  | 256   |

| ECC (public key)    | 163                      | 233  | 283  | 409  | 7680  |

| RSA (public key)    | 1024                     | 2048 | 3072 | 7680 | 15360 |

Table 1.1: Comparison of security levels per bit in cryptosystems.

The chosen technology for the hardware implementation is FPGA which provides high flexibility for hardware design and development. FPGA is reprogrammable by using VHDL (Very High Speed Integrated Circuit Hardware Description Language) to describe digital signals and circuits. FPGA brings a cost and time effective design approach since multiple designs can be updated on the same device which does not need to be fabricated for each new implementation. The use of Xilinx products for hardware development such as Xilinx Integrated Software Environment (ISE) allows project management of VHDL code, generation of synthesis reports, generation of programming files and the use of Xilinx ISim for waveform simulations.

#### 1.1 Project Scope

The primary goal of the project is to achieve an efficient hardware implementation of ECC over the binary field using FPGA. The scope of the project will only consist of the implementation of ECC up to the point of elliptic curve scalar multiplication. This means that the implementation of actual ECC protocols such as ECDH and ECDSA will be considered out-of-scope. The project will be completed with the following specifications:

- All implementations for FPGA will be done using VHDL.

- The implementation of Galois Field operations addition, squaring, multiplication, inversion and reduction will be over the binary fields  $GF(2^{233})$  and  $GF(2^{283})$ .

- The implementation of elliptic curve group operations elliptic curve point doubling (ECPD) and elliptic curve point addition (ECPA) will be done using the National Institute of Standards and Technology (NIST) recommended non-supersingular elliptic curves and associated parameters.

- The implementation of ECSM will be achieved using the NIST recommended curves and parameters.

The aim of this project is also to explore alternative methods, algorithms and hardware architectures which will improve the efficiency of the computation of ECSM. Some implementations will improve the speed of the system while others will produce a better result in terms of area. Through trying different solutions, the trade-off between area and time can be analysed and the optimal solution can be proposed for ECSM over the binary fields  $GF(2^{233})$  and  $GF(2^{283})$ .

Chapter 2 presents the background knowledge that is required for ECC to be used in the later chapters. The relevant theories, algorithms and hardware design is introduced for the foundations of ECC. Relevant work by other authors and the performances of their implementation is then noted which is later used as a comparison for the work of this project.

The experimental procedures used for the design, implementation and verification of the hardware architecture used for the ECSM processor is shown in chapter 3. This chapter describes the resources used and the typical design flow that was used for the implementation of each module used in this project.

In Chapter 4, the hardware design and development for Galois field arithmetic is proposed. The algorithms chosen are presented here which were then used to construct binary field addition, squaring, multiplication and inversion.

Chapter 5 then presents the hardware design and implementation for elliptic curve arithmetic using the hardware for Galois field arithmetic that was implemented in Chapter 4. In this chapter, ECPA and ECPD were constructed for affine coordinates and Jacobian coordinates. ECPA and ECPD were then used to implement the hardware which performs ECSM.

Chapter 6 reveals the optimisation techniques explored to improve the area and time efficiency of the overall ECSM hardware architecture. These include the design and implementation of modified multipliers, concurrent hardware methods, and the optimisation of ECPA and ECPD.

Chapter 7 then summarises the results of the hardware implementations proposed in chapter 4, 5, and 6. The synthesis reports generated from the VHDL design are analysed for advantages and disadvantages of the different methods used at each level of the ECSM architecture. The trade-off between area and time is then discussed where the most efficient design of ECSM in FPGA for  $GF(2^{233})$  and  $GF(2^{283})$  is proposed.

| 4 | Chapter 1. Introduction |

|---|-------------------------|

|   | *                       |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

|   |                         |

## Chapter 2

## Background and Related Work

#### 2.1 Elliptic Curve Cryptography

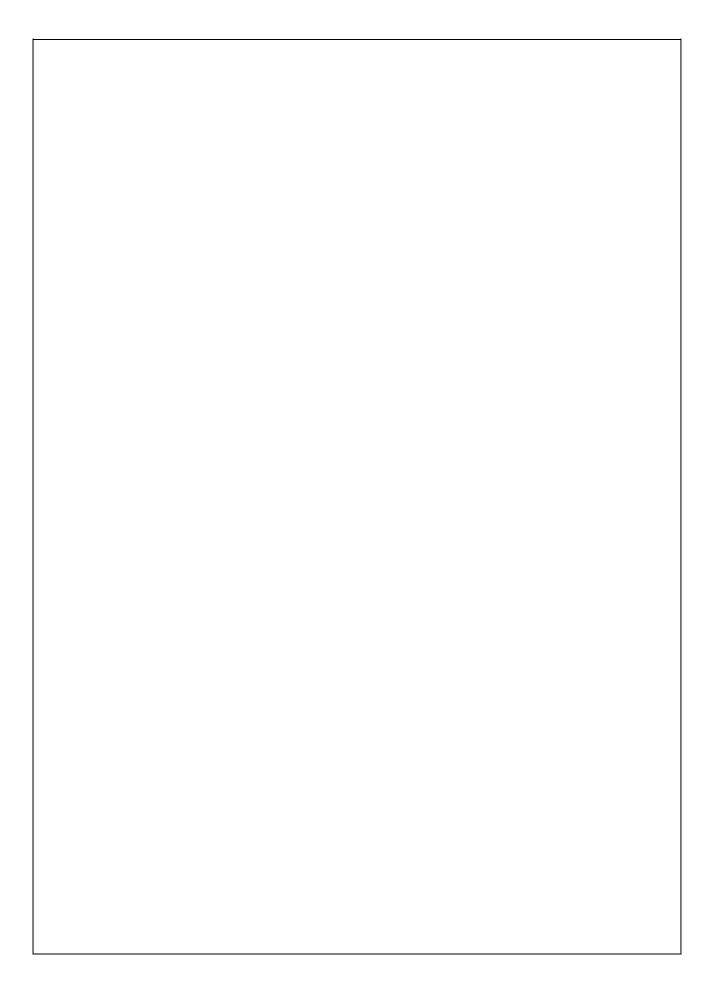

A detailed overview of ECC was presented by Hankerson et al. [7] where they present core concepts, algorithms, and explores various methods of implementation. The ECC scheme can be broken down into a hierarchy of operations as shown in figure 2.1. Each level of this hierarchy depends on the efficiency of the underlying level of operations. Because of this, it is highly important that the Galois Field operations are implemented as efficiently as possible in a bottom up approach to achieve a high performance ECSM hardware architecture. There are different techniques that can be used to improve the efficiency of operations at each level of operation that will be discussed in the following subsections.

Figure 2.1: Hierarchy of operations for elliptic curve cryptography.

#### 2.2 Galois Field Arithmetic

Galois Field Arithmetic (GFA) also known as finite field arithmetic (FFA) is crucial in the implementation of ECC. There are three types of finite fields as shown in [7], including prime fields, binary fields, and optimal extension fields. Modulo-2 arithmetic is very efficient and easily implemented in hardware and so a focus on the binary field will be used for this research. A binary field has an order of  $2^m$  with a maximum degree of m-1 and can be denoted as  $GF(2^m)$ . A polynomial basis is used to represent elements in the field such that  $x^3 + x^2 + 1$  is represented in  $GF(2^4)$  as  $1101_2$ . f(x) is used to denote the reduction polynomial with a degree of at most m for a chosen binary field. Any arithmetic using a binary field is performed modulo the corresponding reduction polynomial of the binary field used. The following subsections will introduce addition, squaring, multiplication and inversion over  $GF(2^m)$ .

#### 2.2.1 Addition over the Binary Field

Addition is the simplest operation over a binary field which can be achieved in one clock cycle. Adding two elements in  $GF(2^m)$  is done using bit-wise exclusive-or (XOR). Using bit-wise XOR is the best method of addition over a binary field and is used for all ECC implementations.

#### 2.2.2 Squaring over the Binary Field

Squaring is the multiplication of two identical binary polynomials. Squaring in  $GF(2^m)$  is performed in m clock cycles [8]. Squaring can be achieved by inserting a '0' bit between each bit of a binary polynomial followed by reduction of the result. The result of squaring must be reduced if it lies outside of  $GF(2^m)$ . A squaring method is often implemented since it can be more efficient than the multiplication of two identical numbers. This consideration will depend on the efficiency of multiplication implemented, since if multiplication becomes more efficient that squaring, then the squaring method can be replaced.

#### Reduction

Reduction may also need to be performed on the result of squaring and multiplication to ensure that the result exists within the binary field chosen. Reduction uses the reduction polynomial f(x) of the corresponding binary field so that a binary polynomial a(x) is reduced to r(x), where  $r(x) = a(z) \mod f(x)$ . Reduction can be done one bit at a time through modular reduction, or by fast reduction algorithms are also shown by Hankerson for the NIST recommended binary fields for  $GF(2^{163})$ ,  $GF(2^{233})$ ,  $GF(2^{283})$ ,  $GF(2^{409})$ , and  $GF(2^{571})$  [7].

#### 2.2.3 Multiplication over the Binary Field

Multiplication is the second most expensive operation over a binary field. Similar to squaring, multiplication can also be done through normal polynomial multiplication and addition of partial products followed by a reduction of the final result. However, this is inefficient and more popular algorithms use interleaved modular reduction so a specific reduction method is not required. The common methods to perform multiplication include multiplication with an interleaved modular reduction algorithm [8], bit-serial multiplication, radix-multipliers, digit-serial multiplication, and digit-parrallel multiplication [7] [11]. Pan have also proposed a more efficient version of the digit-serial multiplication algorithm in [11].

#### 2.2.4 Inversion over the Binary Field

Inversion is the most expensive operation of binary field arithmetic for ECC. The inverse of a non-zero element  $a \in GF(2^m)$  is  $g \in GF(2^m)$ , where  $ag = 1 \mod f(x)$  and  $g = a^{-1}$ . Inversion takes approximately double the time for multiplication in the same binary field as shown in table 2.1, [8] and [6]. Popular algorithms for inversion used for ECC implementation include the extended Euclidean algorithm and the almost inverse algorithm. Another algorithm for inversion is the Itoh-Tsuji algorithm based on Fermat's little theorem [9], where a high-speed implementation was achieved in [18]. A systolic array implementation of a modified Euclid's algorithm for inversion is also proposed in [5].

#### 2.3 Elliptic Curve Scalar Multiplication

#### 2.3.1 Elliptic Curve Group Operations

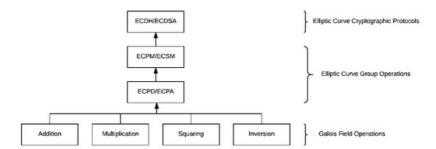

Elliptic Curve Cryptography is the use of elliptic curves over finite fields for key exchange, encryption and digital signatures. ECC is based on the elliptic curve discrete logarithm problem (ECDLP) where it is infeasible to derive a private key, k from a public key Q = kP, where k is an integer value and P is a point on the elliptic curve. There are multiple elliptic curves that can be used. However, the elliptic curves as recommended by the National Institute of Standards and Technology (NIST) [15] use a non-supersingular elliptic curve for ECC over binary fields as shown by equation 2.1. ECSM is used to compute multiples of points on an elliptic curve by the use of repeated addition and doubling of points on an elliptic curve. Elliptic curve point doubling and point addition are illustrated as shown by the graphs in figure 2.2. There are multiple algorithms that can be used for elliptic curve scalar multiplication. The simplest is the right-to-left double-and-add method. Other methods that have been implemented include the binary/window non-adjacent form (NAF) method and the Montgomery Ladder method [2,7,16].

The points on an elliptic curve can be represented using different coordinate systems such as affine coordinates and Jacobian projective coordinates which will be discussed further in section 2.3.2 and 2.3.3. The choice of coordinate system will determine how

Figure 2.2: Point addition (P+Q) and point doubling (2P) on an elliptic curve [20].

|                | Affine         |                | Jacobian       |                |

|----------------|----------------|----------------|----------------|----------------|

|                | Point Addition | Point Doubling | Point Addition | Point Doubling |

| Inversion      | 1              | 1              | 0              | 0              |

| Multiplication | 2              | 2              | 15             | 5              |

| Squaring       | 1              | 2              | 5              | 5              |

| Addition       | 9              | 5              | 7              | 4              |

**Table 2.1:** Comparison of operations required for point addition and point doubling in affine coordinates and Jacobian coordinates.

ECPA and ECPD will be constructed, as a different number and combination of underlying Galois field operations will be used. One advantage of projective coordinates over affine coordinates is the minimisation of inversion, however many more binary field operations for multiplication and squaring must be used. A summary of the operations used for ECPA and ECPD are shown in table 2.1. Other coordinate systems have also been used in literature such as Lopez-Dahab coordinates and the Montgomery method of point addition and doubling, which can offer even more improvements as shown by implementations in [19] and [4].

#### 2.3.2 Affine Coordinates

Affine coordinates can be used to represent points on an elliptic curve. The set of points for a binary field is the set of solutions to equation 2.1 of a non-supersingular elliptic curve E. A point P is shown by  $P(x,y): x,y \in GF(2^m)$ . Elliptic curve point addition and point doubling is shown in equation 2.2 and equation 2.3 respectively [7]. Point addition is used for the addition of two different points, while point doubling is used for the addition

of identical points.

$$E: y^2 + xy = x^3 + ax^2 + b (2.1)$$

$$R(x_3, y_3) = P(x_1, y_1) + Q(x_2, y_2) \in E$$

$$x_3 = \lambda^2 + \lambda + x_1 + x_2 + a,$$

$$y_3 = \lambda(x_1 + x_3) + x_3 + y_1,$$

$$\lambda = (y_1 + y_2)/(x_1 + x_2)$$

(2.2)

$$R(x_2, y_2) = 2P(x_1, y_1) \in E$$

$$x_2 = \lambda^2 + \lambda + a,$$

$$y_2 = x_1^2 + \lambda x_2 + x_2,$$

$$\lambda = (x_1 + y_1)/x_1$$

(2.3)

#### 2.3.3 Jacobian Coordinates

A projective coordinate system such as Jacobian coordinates can also be used to perform ECPD and ECPA. The non-supersingular curve used for Jacobian projective coordinates is the set of solutions to equation 2.5. Jacobian coordinates are more appealing than affine coordinates since these two operations can be performed without the need of inversion. Inversion is only needed for converting from Jacobian coordinates to affine coordinates and this can be achieved using equation 2.4. Just like affine coordinates, point addition shown in equation 2.6 is used for the addition of two different points while point doubling shown in equation 2.7, is used for the addition of two identical points [16].

$$\begin{aligned} \text{Affine}(X/Z^2,Y/Z^3) &= \text{Jacobian}(X,Y,Z), \\ where \ Z \neq 0 \end{aligned} \tag{2.4}$$

$$E: Y^2 + XYZ = X^3 + aX^2Z^2 + bZ^6$$

(2.5)

$$R(X_{2}, Y_{2}, Z_{2}) = P(X_{0}, Y_{0}, Z_{0}) + Q(X_{1}, Y_{1}, Z_{1}) \in E,$$

$$U_{0} = X_{0}Z_{1}^{2}$$

$$U_{1} = X_{1}Z_{0}^{2}$$

$$S_{0} = Y_{0}Z_{1}^{3}$$

$$S_{1} = Y_{1}Z_{0}^{3}$$

$$W = U_{0} + U_{1}$$

$$R = S_{0} + S_{1}$$

$$L = Z_{0}W$$

$$V = RX_{1} + LY_{1}$$

$$Z_{2} = LZ_{1}$$

$$T = R + Z_{2}$$

$$X_{2} = aZ_{2}^{2} + TR + W^{3}$$

$$Y_{2} = TX_{2} + VL^{2}$$

$$(2.6)$$

$$R(X_{2}, Y_{2}, Z_{2}) = 2P(X_{1}, Y_{1}, Z_{1}) \in E,$$

$$X_{2} = X_{1}^{4} + bZ_{1}^{8}$$

$$Y_{2} = X^{4}Z_{2} + UX_{2}$$

$$Z_{2} = X_{1}Z_{1}^{2}$$

$$U = Z_{2} + X_{1}^{2} + Y_{1}Z_{1}$$

$$(2.7)$$

2.4 Related Work 11

#### 2.4 Related Work

There have been many implementations of ECSM in the literature which present several approaches for the design of an efficient hardware system. In this section a focus on FPGA implementations of ECSM over a binary field will be explored. One implementation of ECSM is shown by Hossain et al [8], where their design is able to perform one point multiplication in 2.66ms and 5.54ms in the field sizes of  $GF(2^{233})$  and  $GF(2^{283})$  respectively. The methods used in their implementation present an area-efficient implementation which uses bit-serial multiplication, the modified extended Euclidean algorithm and performs ECPA and ECPD in affine coordinates. The clock cycles required for their binary field operations are shown in table 2.2. Their paper also suggests the use of Jacobian coordinates for further improvement on their design.

| Operation    | Addition | Multiplication | Squaring | Inversion |

|--------------|----------|----------------|----------|-----------|

| Clock cycles | 1        | 233            | 233      | 467       |

**Table 2.2:** Clock cycles of binary field operations using bit-serial multiplication and the modified extended Euclidean algorithm.

An implementation by Govem in [3] requires 65,000 clock cycles with a computation time of 0.24ms on a Xilinx Virtex-5 device. Lutz and Han implemented their design on the Virtex-E device and were able to achieve a computation time of 0.075ms using Lopez-Dahab projective coordinates in  $GF(2^{233})$ .

Due to the disadvantages of using inversion in affine coordinates, there has been a shift to Jacobian coordinates which will require efficient multiplication algorithms. Bitserial multiplication in  $GF(2^m)$  performs a multiplication in m clock cycles. Multiple implementations use digit-serial multiplication as shown in [7] which reduces the latency of multiplication to  $\lceil m/d \rceil$  clock cycles. Pan and Lee have worked on improvements on binary field multiplication where they propose digit-serial and digit-parrallel systolic multipliers in [11], where a binary field multiplication can be achieved in  $2 \cdot \lceil \sqrt{m/d} \rceil$  clock cycles. Another multiplication algrithm used for ECSM implementations is the Karatsuba-Ofman algorithm which was used in [12], where a ECSM is achieved in 0.059ms in  $GF(2^{163})$ , 0.084ms in  $GF(2^{233})$  and 0.102ms in  $GF(2^{283})$ . A hardware implementation which also uses digit-serial multiplication is presented in [22] which produces a latency of 0.089ms for ECSM in the binary field of  $GF(2^{233})$ .

| 12 | Chapter 2. Background and Related Work |  |  |

|----|----------------------------------------|--|--|

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

|    |                                        |  |  |

### Chapter 3

## Experimental Procedures

This chapter presents the resources and experimental procedures used in conducting research for the hardware design, implementation and testing of an ECSM processor. A description of resources used is presented in section 3.1 followed by the experimental procedures in section 3.2.

#### 3.1 Resources

The resources used consist mostly of Xilinx software products which were downloaded from www.xilinx.com/products/design-tools. A free (but restricted) Xilinx 'WebPACK' license was used for this project. The Xilinx Integrated Software Environment (ISE) was used for FPGA design and development using VHDL. The Xilinx ISE was used for compiling the design from VHDL code, waveform simulations using Xilinx ISim, generating synthesis reports, and to generate the programming file that can be used to load a design onto an FPGA hardware device. Xilinx iMPACT or Diligent Adept software can then be used for loading a hardware design onto FPGA devices. To minimise risks associated with the use of software, a private GitHub repository was used for back-up and as a version control system for all VHDL files and Xilinx ISE projects.

#### 3.2 Experimental Procedures

To conduct the experiments for this project, a design flow is required for the construction of a digital system from VHDL for FPGA devices. As identified in the background in chapter 2, this research will require the hardware design for multiple modules such as for Galois field operations (addition, squaring, multiplication and inversion) and the elliptic curve group operations (ECPA, ECPD and ECSM). A complete list of modules to be designed and implemented for both binary fields  $GF(2^{233})$  and  $GF(2^{288})$  include the following:

Addition

- Traditional digit-serial multipliers (for the digit sizes of 1, 2, 4, 8, 16, 32, and 64)

- Inversion

- Affine point doubling (APD)

- Affine point addition (APA)

- Jacobian point doubling (JPD)

- Jacobian point addition (JPA)

- ECSM controller in affine coordinates

- ECSM controller in Jacobian coordinates

- Conversion from Jacobian to Affine coordinates

- Serial-in-parallel-out (SIPO)

- Parallel-in-serial-out (PISO)

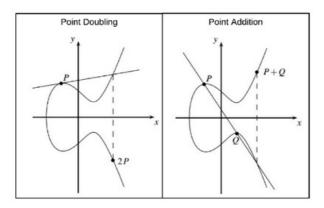

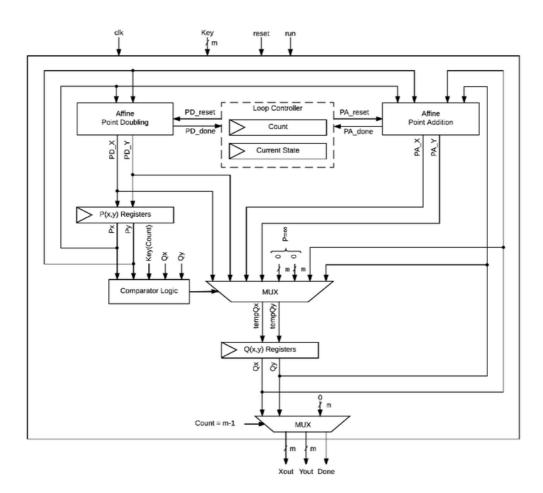

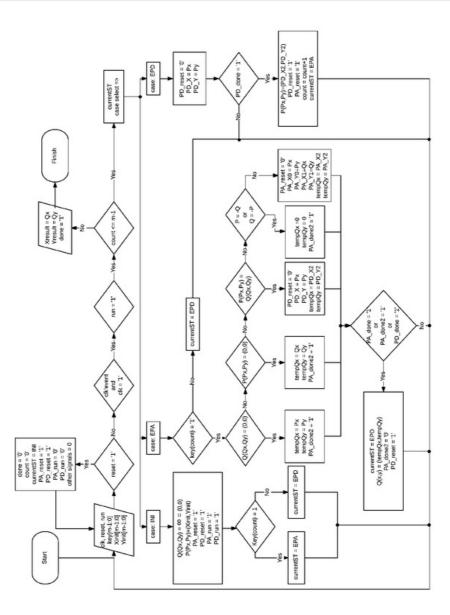

Figure 3.1: Simplified top-level model for the ECSM architecture in FPGA.

The completion of the above modules will result in the initial implementations of an ECSM hardware architecture as shown in figure 3.1. These will then be optimised with the addition of the design and implementation of the following modules which are discussed further in chapter 6:

- Modified digit-serial multipliers (for the digit sizes of 1, 2, 4, 8, 16, 32, and 64)

- Concurrent ECSM controllers for both affine and Jacobian coordinates

- Combined Jacobian point addition and point doubling (PAPD)

The design flow used will be repeated for each module to be constructed which is outlined as follows:

- 1. Algorithm selection

- 2. Logic Modeling

- 3. VHDL coding

- 4. Syntax and behavioral verification

- 5. Testing and waveform simulations

- 6. Synthesis

- Comparison and analysis of hardware designs

#### 3.2.1 Algorithm selection

This is the first step taken in the design flow to create a hardware module. The present literature related to binary field arithmetic and elliptic curve group operations were analysed for efficient methods, algorithms and hardware architectures that could be used in this research. The timing complexities and area of designs were considered before an algorithm was chosen for implementation.

#### 3.2.2 Logic Modeling

The algorithms selected were then modeled in various ways to assist in easing the transition from an algorithm to a hardware design using VHDL. Trying to implement the VHDL code for large binary fields of  $GF(2^{233})$  and  $GF(2^{233})$  can be difficult. So smaller field sizes such as  $GF(2^4)$  were initially used where examples using the algorithm could be done using pen and paper. Flow-charts were also used which were beneficial in showing the data flow of an algorithm.

#### 3.2.3 VHDL coding

Once an algorithm was modeled, the VHDL code could then be created. The VHDL code was written using Xilinx ISE. A new entity and separate VHDL file was created for each new module required.

#### 3.2.4 Syntax and behavioral verification

VHDL coding is not complete until the syntax and behaviour checks for a hardware design is successful. These checks are available as tools in the Xilinx ISE. If these checks fail then the errors must be corrected by modifying the VHDL code.

#### 3.2.5 Testing and waveform simulations

In this phase, the VHDL code for a module is verified. This requires the creation of a VHDL test bench where inputs to the designed module can be chosen. This test bench is then used for simulations using Xilinx ISim where the waveform output is checked against the expected value(s) and delays. If the results of the simulation are not correct then the VHDL code and logic models must be checked to ensure the correct hardware implementation of an algorithm that is free of errors.

#### 3.2.6 Synthesis

Once the tests are correct, then the hardware design in VHDL can be synthesised to a target FPGA device using the Xilinx Synthesis Tool (XST). The target FPGA device used in this research is the Xilinx Virtex-6 (XC6VLX760-2ff1760). The XST generates a synthesis report for the design which displays the area and timing constraints such as slice registers, slice look-up-tables (LUT), LUT flip-flop pairs, minimum clock periods, and clock frequencies. Minor changes in VHDL code can result in different hardware performances analysed from the synthesis reports in terms of time and area so the design should be optimised for the most efficient results.

#### 3.2.7 Comparison and analysis of hardware designs

Finally the hardware performances shown by the synthesis reports are recorded. Different hardware implementations are then analysed and compared against each design with a focus on area and time. The most efficient design is then chosen to be used in the final ECC processor for  $GF(2^{233})$  and  $GF(2^{283})$ .

For this research, the hardware performances from the synthesis reports were recorded as the results in chapter 7. For the implementation on an FPGA device, a bit file would need to be generated using Xilinx ISE. This bit file is then loaded onto the FPGA from a computer using a JTAG cable and either Xilinx iMPACT or Digilent Adept software.

## Chapter 4

# Hardware for Galois field arithmetic over $GF(2^m)$

This chapter will show the hardware design and implementation of Galois field arithmetic for this research using VHDL for FPGA devices. Each section will discuss the design process leading up to creation of VHDL code including algorithms chosen, flow chart models, and block diagrams. The related background shown in section 2.2 identifies that addition, multiplication, squaring and inversion modules will be necessary for ECC. The design methods used for this project can be used for any sized binary field. However, only the hardware designs for  $GF(2^{233})$  and  $GF(2^{283})$  have been implemented as specified by the project scope.

The design of each module is shown in figure 4.1, where each module also has the inputs 'clock', 'run', and 'reset', and output 'done'. The input 'reset' is used to reset all internal signals of a module, 'run' is used to start a module and keep it running for the duration that run is '1'. The 'done' signal then indicates when the module has produced a final output. The designs use an asynchronous reset. These external signals aid the correct timing of Galois field operations in ECPA and ECPD since each operation will have different delays. The modular design of finite field arithmetic will allow for modifications of the system which can easily be achieved by replacing an individual module.