#### VERILOG-A MODELING OF TRANSISTOR

Zhili Yang

Bachelor of Engineering Electronic Engineering Major

Department of Electronic Engineering Macquarie University

April 4, 2016

Supervisor: Dr Oya Sevimli and Prof. Tony Parker

#### ACKNOWLEDGMENTS

I would like to gratefully and sincerely thank Associate Professor Tony Parker and my department supervisor Oya Sevimli for their guidance, patience, understanding and most importantly, their friendship during my thesis at Macquarie University.

I would like to thank my engineering friends for their help when I needed it the most. Finally, I would like to extend my gratitude to the Department of Engineering for offering me the opportunity to undertake this thesis.

#### STATEMENT OF CANDIDATE

I, (Zhili Yang), declare that this report, submitted as part of the requirement for the award of Bachelor of Engineering in the Department of Electronic Engineering, Macquarie University, is entirely my own work unless otherwise referenced or acknowledged. This document has not been submitted for qualification or assessment an any academic institution.

Student's Name: Zhili Yang

Student's Signature: Zhili Yang

Date: 4 April 2016

#### ABSTRACT

Industry standard transistor models used for computer aided circuit design are not always accurately predicting transistor performance under all circuit conditions, include RF and analog circuit behavior. Transistor model are expected not only circuit performance but also reliability and accuracy. Improved accuracy may need concern access to the internal currents and voltages of the transistor or add extra internal features such as low-frequency noise sources. Circuits that have very stringent accuracy requirements require modeling techniques with higher accuracy. In contrast, Verilog-A enables full control of transistor model and can be integrated with the circuit design software. This document report presents how effective approach to investigate and implement our transistor model in two different environments-AWR and Verilog-A. This is useful for circuit-level design purposes to allow the designer manipulates transistor models have direct access to model equation sets and program structure. A comparison of results between simulation and measurements to transistor model has been illustrated in details.

# Contents

| A             | cknov                            | wledgn           | nents                                                                                                                                                                                  | iii                                |

|---------------|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| A             | bstra                            | ict              |                                                                                                                                                                                        | vii                                |

| Ta            | able o                           | of Con           | tents                                                                                                                                                                                  | ix                                 |

| Li            | ist of                           | Figure           | es x                                                                                                                                                                                   | ciii                               |

| $\mathbf{Li}$ | ist of                           | Tables           | 5                                                                                                                                                                                      | xv                                 |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3 | 1.1.1<br>Thesis  | ion         ation                                                                                                                                                                      | 1<br>1<br>2<br>3<br>3<br>4         |

| 2             | Lite<br>2.1                      | erature          | <b>Review and Theory</b> HBT Model         Introduction         Overview over HBT Model Features         Model topology         Iarge-signal Equivalent Circuit         Thermal Effect | <b>5</b><br>5<br>5<br>6<br>6<br>7  |

|               | 2.2                              | $2.1.6 \\ 2.1.7$ | Importance of HBT modeling                                                                                                                                                             | 8<br>8<br>9<br>9<br>10<br>10<br>11 |

|               |                                  | 2.2.5            | Enhance VBIC model for HBT model                                                                                                                                                       | 12                                 |

|          | 2.3 | Noise Sources                                                                                                                                                               | റ        |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | 2.0 |                                                                                                                                                                             |          |

|          |     | 2.3.1 Noise Phenomena $\dots$ 12                                                                                                                                            |          |

|          |     | 2.3.2 Thermal noise                                                                                                                                                         |          |

|          |     | 2.3.3 Shot noise                                                                                                                                                            |          |

|          |     | 2.3.4 Diffusion Noise                                                                                                                                                       |          |

|          |     | 2.3.5 Flicker noise $(1/f \text{ noise})$                                                                                                                                   |          |

|          |     | 2.3.6 Generation-Recombination noise $\ldots \ldots \ldots$ | 4        |

|          | 2.4 | Low-Frequency Noise Characteristics                                                                                                                                         | 4        |

|          |     | 2.4.1 Low-Frequency Noise in Nonlinear Systems                                                                                                                              | 4        |

|          |     | 2.4.2 HBT Noise Model $\ldots \ldots \ldots$                | 4        |

|          |     | 2.4.3 How the low-frequency noise sources are implemented 1                                                                                                                 | <b>5</b> |

|          | 2.5 | Verilog-A                                                                                                                                                                   | 6        |

|          |     | 2.5.1 Verilog-A Modules                                                                                                                                                     |          |

|          |     | 2.5.2 Advantages of Verilog-A                                                                                                                                               |          |

|          |     |                                                                                                                                                                             | '        |

| 3        | PD  | K Development Training 22                                                                                                                                                   | 1        |

|          | 3.1 | PDK Overview                                                                                                                                                                | 1        |

|          | 3.2 | Installation Guide for AWR Foundry SDK and the Model Wizards 22                                                                                                             |          |

|          | 3.3 | Getting started with the model Wizard                                                                                                                                       |          |

|          | 0.0 | 3.3.1 Overview                                                                                                                                                              |          |

|          |     | 3.3.2 MIM Cap imported from schematic                                                                                                                                       |          |

|          |     |                                                                                                                                                                             |          |

|          |     |                                                                                                                                                                             |          |

|          |     | 3.3.4 Measure Internal Branch Current/Voltages                                                                                                                              |          |

|          |     | 3.3.5 Analysis of issues                                                                                                                                                    | 0        |

| 4        | Cro | ate models in NI AWRDE PDK 29                                                                                                                                               | n        |

| 4        |     |                                                                                                                                                                             |          |

|          | 4.1 | The Procedure of creating models                                                                                                                                            |          |

|          |     | 4.1.1 Define the model $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                                                                  | 2        |

| <b>5</b> | Res | ults and Discussion 43                                                                                                                                                      | 3        |

| 0        | 5.1 | Resistor Model                                                                                                                                                              |          |

|          | 0.1 | 5.1.1 A Linear Resistor in Verilog-A                                                                                                                                        |          |

|          |     | 5.1.2 The simulation result of reisstor model in NI AWRDE                                                                                                                   |          |

|          | 5.2 | Diode Model                                                                                                                                                                 |          |

|          | 0.2 |                                                                                                                                                                             |          |

|          | E 9 | 8                                                                                                                                                                           |          |

|          | 5.3 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                        |          |

|          | F 4 | 5.3.1 A Nonlinear Transistor in Verilog-A                                                                                                                                   |          |

|          | 5.4 | Chapter Summary 48                                                                                                                                                          | 3        |

| 6        | Cor | clusions and Future Work 53                                                                                                                                                 | 1        |

| U        | 6.1 | Future Work   5     Future Work   5                                                                                                                                         |          |

|          | 0.1 |                                                                                                                                                                             |          |

|          |     | 6.1.1 Add Noise to the Verilog-A Resistor                                                                                                                                   |          |

|          |     | 6.1.2 Add an Internal Node to the diode                                                                                                                                     |          |

|          |     | 6.1.3 Add limiting to the diode for get better convergence                                                                                                                  | 2        |

|              | 6.1.4 The Verilog-A of transistor         | 52 |

|--------------|-------------------------------------------|----|

| 7            | Abbreviations                             | 53 |

| $\mathbf{A}$ | Verilog-A Code                            | 55 |

|              | A.1 Overview                              | 55 |

|              | A.2 Resistor in Verilog-A                 | 55 |

|              | A.3 Diode in Verilog-A                    | 55 |

|              | A.4 Transistor in Verilog-A               | 55 |

| в            | Project Plan and Attendance Form          | 65 |

|              | B.1 Overview                              | 65 |

|              | B.2 Consultation Meetings Attendance Form | 66 |

|              | B.3 Project Plan                          |    |

|              | B.4 Project Consultation meetings         |    |

|              | B.5 LOGBOOK                               |    |

| Bi           | bliography                                | 67 |

#### $\mathbf{x}\mathbf{i}$

# List of Figures

| 2.1          | Schematic cross section of a single finger HBT [8]                           | 7               |

|--------------|------------------------------------------------------------------------------|-----------------|

| 2.2          | Extrinsic section of equivalent circuit. The model parameters are denoted    |                 |

|              | in oblique magenta letters []                                                | 8               |

| 2.3          | Intrinsic section of large-signal equivalent circuit. The model parameters   |                 |

|              | are denoted in oblique magenta letters []                                    | 9               |

| 2.4          | Equivalent circuit for the VBIC bipolar transistor model [2]                 | 11              |

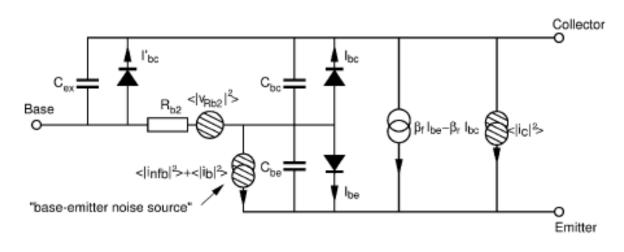

| 2.5          | Intrinsic large-signal of HBT and noise equivalent circuit []                | 15              |

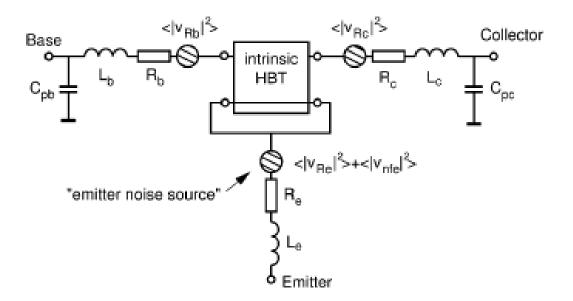

| 2.6          | Extrinsic large-signal of HBT and noise equivalent circuit []                | 16              |

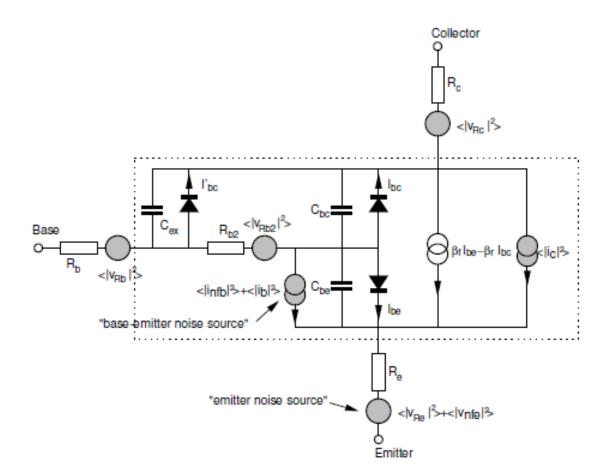

| 2.7          | Large-signal and noise HBT equivalent circuit []                             | 17              |

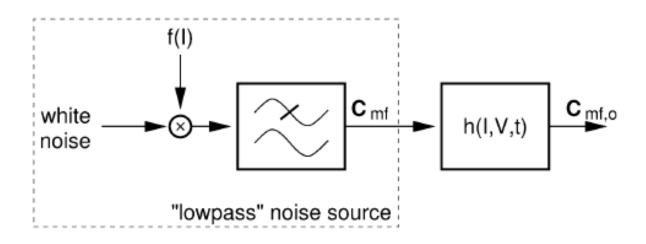

| 2.8          | Schematics illustrating the behaviour of low-frequency noise in large-signal |                 |

|              | excitation (low-pass noise) []                                               | 18              |

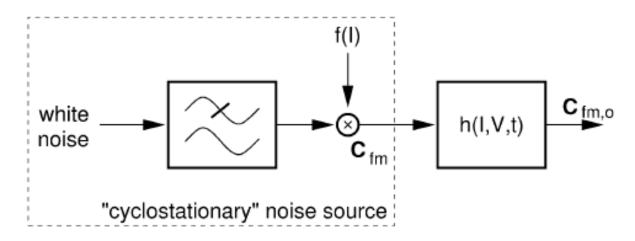

| 2.9          | Schematics illustrating the behaviour of low-frequency noise in large-signal |                 |

|              | excitation (cyclostationary noise) []                                        | 19              |

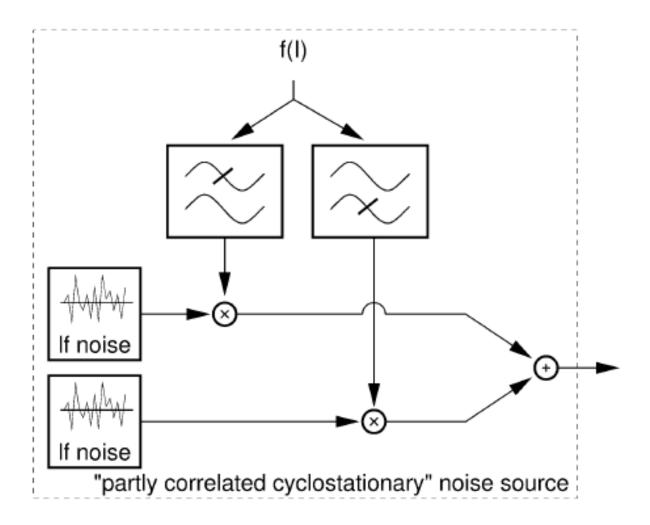

| 2.10         | Schematic indicating implementation of the partly correlated cyclostation-   |                 |

|              | ary noise source []                                                          | 20              |

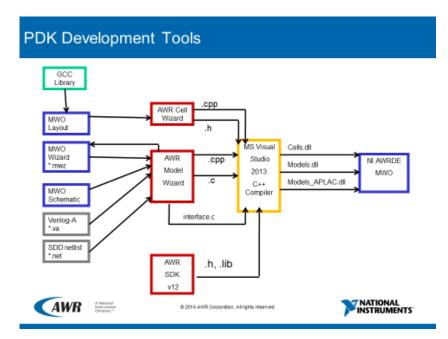

| 3.1          | PDK Development Tools [5]                                                    | 21              |

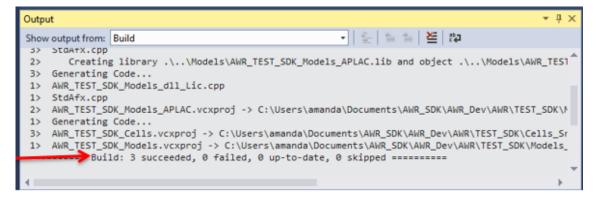

| $3.1 \\ 3.2$ | The output window of Visual studio [5]                                       | $\frac{21}{22}$ |

| 3.3          | The "New AWR PDK Source Builder" dialog [5]                                  | 23              |

| $3.3 \\ 3.4$ | Result of Code change [5]                                                    | $\frac{23}{24}$ |

| 3.5          | CURTICE Model [5]                                                            | $24 \\ 25$      |

| 3.6          | NI AWRDE element browser [5]                                                 | $\frac{20}{26}$ |

| 3.7          | Connect the VSWEEP_step param to 1.0 to the Curtice_2P [5]                   | 20              |

| 3.8          | Resistor Model [1]                                                           | $27 \\ 27$      |

| 3.9          | Resistor in Verilog-A [1]                                                    | $\frac{21}{28}$ |

| 0.5          |                                                                              | 20              |

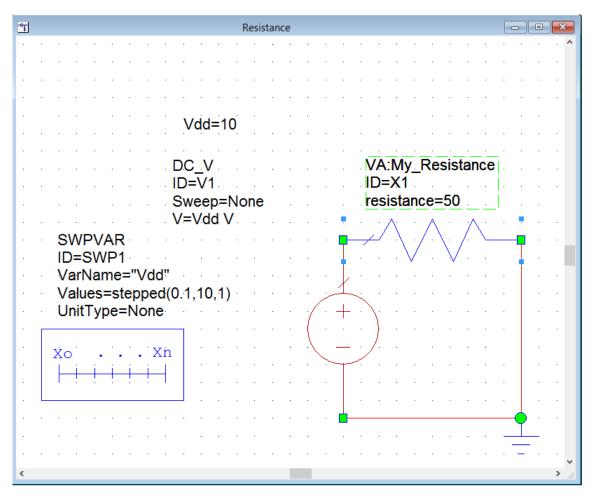

| 5.1          | Circuit of Our Resistance                                                    | 44              |

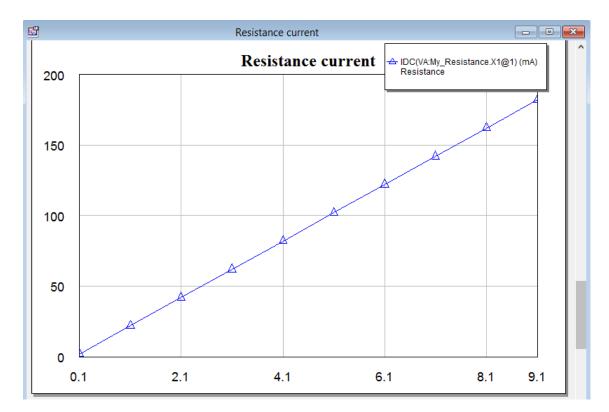

| 5.2          | I-V characteristic Curves of our resistor in both Harmonic Balance simula-   |                 |

|              | tor and APLAC DC simulator                                                   | 45              |

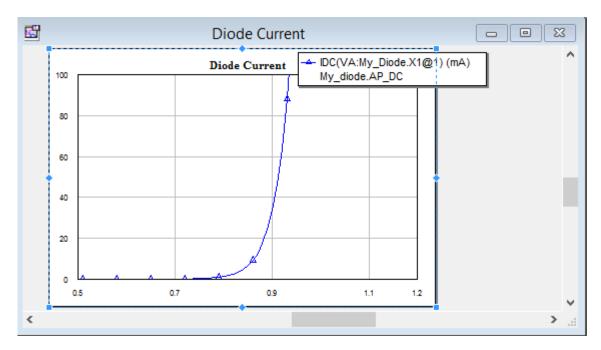

| 5.3          | Circuit of Our Diode                                                         | 47              |

| 5.4          | I-V Characteristic Curve of Our diode in both Harmonic Balance simulator     |                 |

|              | and APLAC DC simulator                                                       | 48              |

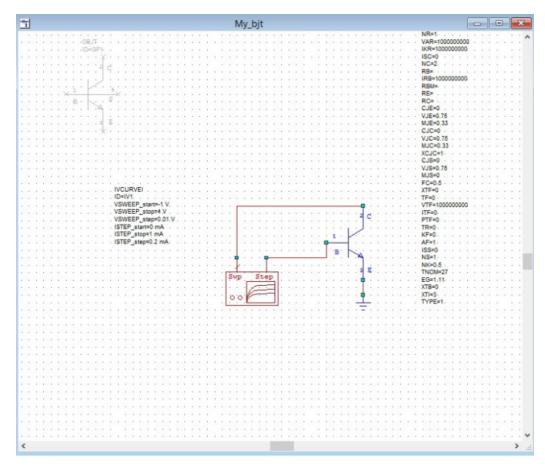

| 5.5          | Circuit of Our Transistor                                                    | 49              |

|              |                                                                              |                 |

# List of Tables

| 1.1 | Time Budget | Summary |  |  |  |  |  |  |  |  |  |  |  |  | • |  |  |  |  |  |  |  |  |  |  | 4 | 1 |

|-----|-------------|---------|--|--|--|--|--|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|--|--|--|---|---|

|-----|-------------|---------|--|--|--|--|--|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|--|--|--|---|---|

# Chapter 1 Introduction

Circuit simulation allows circuit designers to successfully optimize and validate their design. To simulate a circuit, circuit simulators convert the schematic into a system of linear and/or nonlinear differential equations. In order to achieve a schematic to become a system of equation, each component in the circuit must be represented by a smaller system of linear and/or nonlinear differential equations. The smaller system for a component or block is named as the compact model for component [7].

The availability of accurate, efficient compact models is important to the successful utilization of any circuit simulation software. The need for rapid development and distribution of advanced transistor device models becomes more acute than ever.

Traditionally, Transistor device models that are built-in circuit simulators have been developed using general purpose programming languages, such as C, C++, or Fortran. Therefore, they are targeted specifically to the interface and internal data structures of their host simulator. However, this kind of interfaces have typically been not-portable, not standard and inefficient, which result a time consuming and error-prone endeavor in new model creation.

The rapidly increasing availability and utilization of analog HDLs such as Verilog-A provides the promise of a valid outcome to transistor model development and deployment problem. Over the past several years, Verilog-A has become a leading candidate for compact model development. Recently, the compiled solution of Verilog-A become available, which improve the performance of simulation.

# 1.1 Motivation

The compact transistor model is at core of circuit-level design of analog and radio frequency integrated circuits(RFICs) enabling the designer to efficiently achieve design goals. They are used for almost all modern electronic design work. Complete and accurate modeling is based on correct design and analysis of electronic internal circuits especially the analogs ones, which allows design to work earlier. Modern circuit are normally very complex. The performance of such circuit is difficult to predict without accurate transistor models.

The motivation behind the works presented in this thesis is importance of compact transistor modeling in Verilog-A.

Industry standard transistor models used for computer aided circuit design. As system become more complex and as devices become more sophisticated, smaller compact models are necessary for describe the behavior of systems and circuits. Therefore, industry standard transistor models are not always suitable for all situations. Improved accuracy may need access to the internal currents and voltages of the transistor or may be required to add extra internal features such as low- frequency noise sources. Verilog-A language is used for integrated with the circuit design software and allows transistor model designer to focus on their area of expertise, which enable full control of the transistor model. The aim of this thesis project is to investigate and implement Verilog-A models for our transistors and compare with measurements.

## 1.1.1 Challenges

Challenges to designer:

- The compact model developers must be familiar with the Verilog-A computer program.

- Required to familiar with how NI AWRDE operate with visual studio

- The developers require have good understanding about the characteristic of transistor models.

- PDK development training the way it present, which is not clear.

- Required good undestanding in C, C++ code.

# 1.2 Thesis Overview

A brief description of the entire project will be summarized here in this section. TThe project plan and deliverables can be found in Appendix B.3 of this document. This thesis project is supervised by Dr Oya Sevimli, senior lecturer in the Department of Engineering, Macquarie University and co-supervised by Prof. Tony Parker. Regular weekly meetings with the academic supervisor are required which ensure the project is in the right track with the set goals for every weeks. Consultation Meetings Attendance Form can be found in Appendix B.2 of this thesis report.

There are 6 chapters in this thesis report. Chapter 1 gives introduce the whole thesis, which includes the main purpose of this thesis project. Chapter 2 gives specific background

information from the literature and discuss the related transistor models. Topics discussed include The physical HBT, FBH HBT model, VBIC model, Noise sources and Low-Frequency Noise Characteristics. It presents the characteristic of transistor and how noise sources effect the behaviour of transistor.

Chapter 3 discuss how implement model wizard in AWR and using Microsoft visual studio to create model. It also discuss what issues we encounter when implement the software and how we solve it. Furthermore, the simulation results will be used to verify our transistor model are accuracy or not.

Chapter 4 will include the procedure of how we create model in NI AWRDE PDK by using NI AWRDE and visual studio

Chapter 5 will include summary about the thesis and demonstrate the contribution. It include a linear resistor in Verilog-A and a nonlinear diode in Verilog-A. Compare the simulation of our model to theoretical solutions. To investige error of models and how to figure out. Following by a discussion about our project to the future work.

Chapter 6 discusses the possible future work base on the current model in Verilog-A and look at its benefits.

#### **Project Objectives**

- Revision of transistor models.

- Familiarize with simulation software such as AWR, visual studio and Verilog-A.

- Verification of transistor models through AWR nonlinear simulation.

- To investigate how noise sources effect the characteristic of transistor model.

# 1.3 **Project Baseline Review**

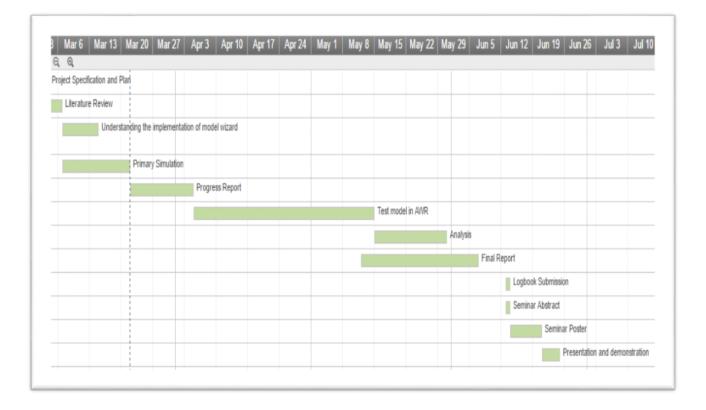

The project was planned to be executed from 1st of March through 24th of June, 2016. Baseline plan was generated with the intention of using only the weekdays, including mid-semester break, for project activities.

#### 1.3.1 Time Budget Review

Table 1.1 summarizes the time budget comparison, according to which 42 days of work has been completed within 35 days. The rest days shall be used for composing the project report, therefore no amendments to the time schedule is required.

Although the allotted time for each activity was followed closely, the order of accomplishment varied. Overall, the progress of the report is followed with the project schedule done at start of the semester. Full detail of actual and planned order of accomplishment and duration of each project activity is depicted in Table 1.3.

| Estimated Work        | 80 days |

|-----------------------|---------|

| Realized Work         | 42 days |

| Percentage Completion | 50%     |

Table 1.1: Time Budget Summary

#### 1.3.2 Financial Budget Review

The project was initially allocated \$300. The project didnt require to buy anything except it required AWR and Visual studio software which I have downloaded from DreamSpark and installed in my laptop. Therefore, there is no further purchasing is required, thus the budget surplus may not need.

# Chapter 2

# Literature Review and Theory

## 2.1 FBH HBT Model

#### 2.1.1 Introduction

Device models are usually used in circuit simulation for the design of integrated circuits. The Heterojunction Bipolar Transistor(HBT) is based either on the GaAs/AIGaAs or GaInP/GaAs compound semiconductor material. In recent years, heterobipolar transistors can be achieved by using commercial GaAs MMIC technology. Due to their advantages able to operate at high power densities they are the devices suit for power amplifiers, such as in mobile phones. Although technology is mature and industry already has a large amount of HBT-based MMICs, the model development in circuit design lacks behind. The designer has a batch build-in models for GaAs-based FETs in standard circuit simulators, however models for GaAs-based HBTs are scarce. The choice to use neither the simple SPICE-type Gummel-Poon model nor full design with a linear S-parameter based model. None of them are satisfy the requirement.

It leads to deal with extension of the GP model that are required for the description of HBTs, and finally tend to the development of FBH model. The state-of-the-art GaAsbased HBTs have characteristics as below:

- The semi-insulating substrate to avoid parasitic substrate effects that have to be considered in silicon.

- In a sophisticated technology, surface or interface involved problems such as parasitic currents are inappreciable, and even thermal runaway can be restrained by using base feedback or proper emitter or by using thermal shunt technology.

Two effects are necessary to be considered in simulate HBTs. The first one is self-heating, the second one is the current dependence of the transit frequency, effected by high current injection into the collector.

#### 2.1.2 Overview over HBT Model Features

The FBH model consider:

- Differentiation of intrinsic and extrinsic base-collector diode

- Non-ideal base currents (Base-Collector and Base-Emitter)

- Thermal interaction and self-heating (by a thermal port)

- Collector transit time and current-dependence of base-collector capacitance

- Charge differentiation

- Break-down involved with base-emitter and base-collector

- Strengthened noise model

- Scaling with transistor size

- Unclear analytic parameter extraction from measurements

## 2.1.3 Model topology

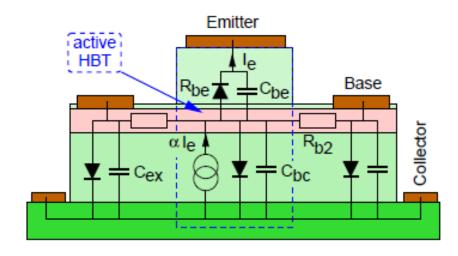

Since substrate effects are inappreciable, it leaves a very simple equivalent-circuit topology as shown Figure 2.1. Because of the structure of the HBTs, the total base-collector junction separates into an active part below the emitter, and a parasitic part below the base contacts. Due to current flows nearly vertically from emitter to sub-collector, the parasitic section has an extra PN diode which is reverse biased in usual operation. The section under the emitter is named as active HBT in order to differentiate it from the parasitic BC-diode which conveys no current. But, both of them are portion of the intrinsic HBT, because the parameters are bias dependent. Only the passive embedding network is named as extrinsic HBT.

## 2.1.4 large-signal Equivalent Circuit

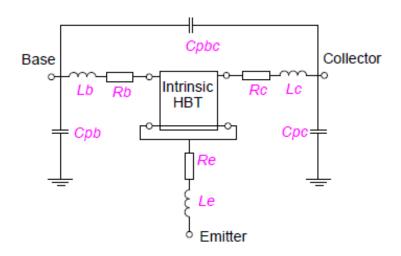

The extrinsic section of the large-signal equivalent circuit is shown in Figure 2.2. It shows the passive feeding structures and contact resistances. Assume all parameters are independent of bias and therefore are same to the small-signal parameters.

The intrinsic large-signal equivalent circuit is shown in Figure 2.3. The extra electrical section, it contains a thermal sub circuit to determine the self-heating of device because of dissipation of power. The current source uses to amplify the base currents in forward and backward operation. Only the current flow through the resistances is amplified, as determined in the figure. The current amplification factors are called BF.

The diode symbols depict bias dependent resistances with diode characteristics. The forward operation case, the collector current is structured by the current source. The

Figure 2.1: Schematic cross section of a single finger HBT [8]

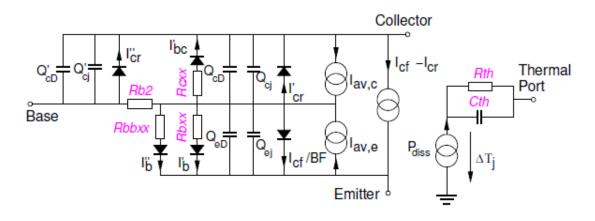

current  $I_{cf}/BF$  depicts the ideal base-emitter current which is amplified. The currents  $I'_{b}$ ,  $I''_{b}$ , and  $I'_{bc}$  depicts the nonideal (parasitic) base currents. The circuit contains bias independent resistors Rbxx, Rbbxx, and Rcxx to generate the possible saturation of these current elements. The base-collector current is divided into two components because of the mesa structure of the HBT: The active HBT include the current  $I'_{cr}$  and the parasitic current  $I''_{cr}$ .  $I'_{cr}$  is effected by the voltage across the parasitic section of diode. Both diodes are split by the resistance of the intrinsic base layer Rb2 that is assumed as a constant value.

Two current sources  $I_{av,c}$  and  $I_{av,e}$  are used to break down base-collector and base-emitter.

Two charges are used for both junctions, a depletion  $(Q_{xj})$  capacitance and a diffusion  $(Q_{xD})$ .

The total dissipated power  $P_{diss}$  is supplied to a thermal subcircuit.

The voltage  $\Delta T_j$  is equal to the temperature rise at the emitter junction because of self-heating of the device.

#### 2.1.5 Thermal Effect

Because of the large thermal resistivity of GaAs, thermal effect containing self-heating are very important in GaAs-based HBTs and must be taken into account when determine the large signal performance of the device. The equivalent circuit denoted in Figure 2.3, the temperature increase at the emitter junction can be figure out. The emitter junction temperature replace the device temperature is used since the temperature distribution is no uniform through the device and the most meaningful effect in temperature rise on

Figure 2.2: Extrinsic section of equivalent circuit. The model parameters are denoted in oblique magenta letters []

device performance happen at the emitter junction. The  $R_{th}$  in the circuit stands for thermal resistance corresponding to the junction temperature increase. Normally,  $R_{th}$  is a constant value in order to simplify the circuit. (A New Large Signal HBT Model)

#### 2.1.6 Importance of HBT modeling

Heterojunction Bipolar Transistor(HBTs) offer substantially great power gain cut-off frequencies. In GaAs/AlGaAs or GaAs/GaInP devices, the wide bandgap emitter allows large base doping without significant charge enter into emitter, giving low base resistance even the device with small base widths.

Physically significant HBT models provide the ability no only to predict and to design a practical circuit with good accuracy, but also to estimate the device parameters how they affecting the circuit performance. This could achieve the optimization of device design with respect to a particular application and the evaluation of the manufacturing process [9].

#### 2.1.7 Challenge of achieve HBT modeling

The problem of how to construct a precise model for GaAs/AlGaAs or GaAs/GaInP HBT can becomes a prominent issue.

An accurate device model that allows the reliable for a wide range of operating biases and signal frequencies is need for the design of high performance microwave circuits. Recently, existing bipolar transistor models used in most commercial circuit simulators, which are based on the Gummel-Poon model. It does not consider several effects which are important for predict the performance of HBT. Especially, the self-heating effect has been

Figure 2.3: Intrinsic section of large-signal equivalent circuit. The model parameters are denoted in oblique magenta letters []

recognized as critical factor in determine the operation of HBT at high power dissipations, because of the low thermal conductivity of GaAs. To design circuits in which thermal effects are critical, dependence of junction depletion capacitance and transit time on collector current, and variation of effective electron barrier in an emitter heterojunction [12]. The thermal and electrical behavior of the circuit must be modeled and solved consistently, which can be complicated. No only this, but also a circuit model for GaAs/AlGaAs HBT is required in nearly all software and simulators to effectively regenerate the physical properties of the device in any new design. Modeling of GaAs/AlGaAs HBT can be very tedious task due to its complexity of device geometry, long process of linear and non-linear model parameter extraction and non-linear properties of the device.

# 2.2 VBIC Model

#### 2.2.1 Compare Gummel-Poon model to VBIC model

Since the early 1970s, the SPICE Gummel-Poon model has become the workhorse for silicon bipolar junction transistor modeling. The construction of the Gummel-Poon(GP) model has consideration in the pivotal physical parameters and mechanisms that allow to control BJT behavior in intuitive and consistent manner. However, the approximation that underlie the Gummel-Poon model ignores the effects, which are critical for sufficiently accurate modeling of BJTs. [4] Such as:

- Parasitic transistor, self-heating, avalanche multiplication is not modeled.

- Collector resistance modulation is not take into account

- Simplified Early effect model is not accurate

The VBIC model for bipolar transistors is an extension of the Gummel-Poon model for Si bipolar transistors. The VBIC models has been improved base on the Gummel-Pool model in the follow aspects:

- Improved temperature

- Improved Early effect on transit time

- Parasitic substrate

- Parasitic transistors

- Parasitic fixed (oxide) capacitance

- Quasi-saturation modeling

- Avalanche multiplication

- Decoupled base current from collect current

- Electro thermal (self-heating effect) modeling [10]

### 2.2.2 Review of VBIC model

Before talk about the VBIC model, we give a brief review about the SGP model. It is a three-terminal model such as emitter, base, and collector terminals and contains three current sources  $I_{CC}$ ,  $I_{bc}$  and  $I_{be}$ , two capacitances related with the charges  $Q_{bc}$  and  $Q_{be}$  stored between the base and collector terminals and between the base and emitter terminals, respectively, and four series resistances.

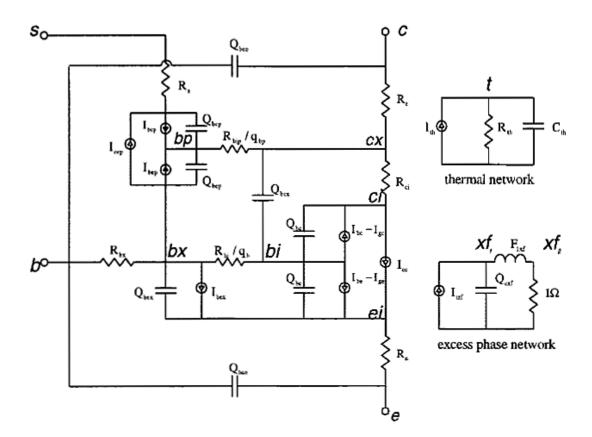

Basic on Figure 2.4 presents the equivalent circuit if the new VBIC model. Different with the conventional SGP model, which is three terminals, the VBIC has four terminal model including the base, emitter, collector, and substrate expressed by the letters b, e, c and s, respectively, and the current entering into these terminals are  $I_b, I_e, I_c$  and  $I_s$ . The other node of VBIC model are extrinsic base bx ,intrinsic base bi, parasitic base bp, intrinsic emitter ei, intrinsic collector ci, and extrinsic collector cx [2].

## 2.2.3 VBIC model more suitable than Gummel-Poon model for HBT modeling

The VBIC bipolar junction transistor model is a candidate for GaAs HBT modeling for a couple of reasons:

- Self-heating and excess-phase effects is included in VBIC model

- It offers a base current model that is a more accurate approximation to the actual device than the one which is used in the conventional Gummel-Poon(G-P) model

Figure 2.4: Equivalent circuit for the VBIC bipolar transistor model [2]

- The base current and the collector current are not relevant through a constant current gain as in the G-P situation

- Quasi-saturation behavior in VBIC model

- It is available in commercial circuit simulators

#### 2.2.4 Issues of VBIC model for HBT modeling

Currently, Existing industry models such as Gummel-Poon(G-P) model and VBIC model are not sufficient to characterize the GaAs/AlGaAs HBT device. VBIC is not perfectly suitable for GaAs/AlGaAs HBT devices because:

- The ideality factors of base-collector and base-emitter current components in HBT is variation with temperature, which is not modeled by VBIC model [3].

- The physical effects involve with high current effects in VBIC model dose not match the GaAs/AlGaAs HBT device.

- The thermal resistance of HBTs is usually to be temperature dependent, which is not modeled by VBIC model [3].

- Relatively high operation current densities make HBTs very sensitive to the base push-out (Kirk) effects, which are required more accurate modeling of transistor time and the current-dependent collector capacitance [3].

- The transistor time frequency is not right when VBIC model is adopted to the GaAs/AlGaAs HBT device.

- The relatively lightly doped collector of GaAs/AlGaAs HBTs make the mobile charge modulation, which is required to be take into account in collector capacitance [11]

- Collector punch-through has a no negligible effect on the capacitance [11]

#### 2.2.5 Enhance VBIC model for HBT model

In order to perfectly match the GaAs/AlGaAs HBT device, a modified VBIC models required in improve with transport current, transits-time and collector capacitance. And also the extraction and optimization of VBIC model parameters are required to be developed. Therefore, the advance VBIC model keeps all of the features of the existing VBIC model while consist of new features with a couple of additional model parameters that are capable of solve the previously effects.

# 2.3 Noise Sources

#### 2.3.1 Noise Phenomena

There is various style of noise phenomena in electronic devices which result in a fluctuation of the signals. The most significant styles are thermal noise, shot noise, diffusion noise, generation-recombination noise, and flicker noise (1/f). The amount of influence of one noise phenomena to the whole noise not only due to the device and its characteristic of operation but also on the operation conditions which is included temperature, bias point, and frequency. A detail of description of noise phenomena is presented in the following parts.

#### 2.3.2 Thermal noise

Thermal noise is produced in any physical resistance that indicates dissipation when current is flowed through it. Thermal noise is a type of electronic noise effected by the random thermal motion of the charge carriers producing microscope current fluentuations. It was formulated first by Nyquist and Johnson in 1926, and is named as Johnson-Nyquist noise. Thermal noise is directly affected by the absolute temperature T and is not related to applied voltage or current. In a resistor, thermal noise is called as white Gaussian noise. A series voltage generator or shunt current used to model thermal noise, which is defined as

$\underline{\phantom{a}} = 4kTR \bigtriangleup f$

or

$$\frac{v^2}{i^2} = 4kT\frac{1}{R}\bigtriangleup f$$

Where R refers to circuit resistance, k refers to Boltmanns constant.  $\Delta f$  refers to bandwidth in hertz and T stands for absolute temperature, which is at the room temperature approximate 300°K.

#### 2.3.3 Shot noise

Different to thermal noise, shot noise is always depending on a direct current flow. It involves in diode and transistors. Shot noise is determined by fluctuation in current that is effected by carriers flowing through the potential barrier at the junction. Such as the emitter-base or base-collector junction in transistor. The noise current generated by shot noise can be defined as:

$$\frac{1}{i^2} = 2qI_D \bigtriangleup f$$

Where q refers to the electronic charge which is equal to  $1.6 * 10^{-19}$  C,  $I_D$  is the bias current.

The shot noise is also called as white noise and it is proportional to the bias current.

#### 2.3.4 Diffusion Noise

Diffusion noise happens in semiconductors with electron density gradient  $d_n/d_x$  where the thermally activated electrons move from places with a high electron concertation to places with a low concentration. The noise is effected by collisions of the moving carriers with the lattice.

#### **2.3.5** Flicker noise (1/f noise)

Flicker noise refers to a physical property in all active devices. It has an enormous influence on circuit. Flicker noise is a low- frequency noise. It is also called as 1/f noise because noise is produced with a slope inversely proportional to the frequency. There is not lower frequency limit for the 1/f noise and the overall noise power can be infinite. Flicker noise can be expressed in term of voltage noise spectrum  $S_V$  or resistance noise spectrum  $S_R$ or current noise spectrum  $S_I$  or conductance noise spectrum  $S_G$ , and these spectra are normally standardized. Such as  $S_V/V^2$ ,  $S_R/R^2$ ,  $S_G/G^2$ . In 1969, Hooge suggested that the fluctuations in conductivity will cause 1/f noise. Flicker noise is normally defined as

$$\frac{1}{i^2} = K_f \frac{I_{DC}^{AF}}{f^{f^{FE}}} \bigtriangleup f$$

Where  $K_f$  refers to level fitting,  $A_f$  refers to the current dependency factor, and  $f_{FE}$  refers to the frequency dependent power factor.

#### 2.3.6 Generation-Recombination noise

Generation-Recombination (G-R) noise is one style of electrical noise produced by fluctuations in the amount of free carriers in semiconductor materials.

# 2.4 Low-Frequency Noise Characteristics

#### 2.4.1 Low-Frequency Noise in Nonlinear Systems

There are two dominant noises at low frequency which are flicker noise and G-R noise. Because of up conversion effects, low-frequency noise can play a crucial role in HBT model. Traditionally, bipolar large-signal models only consider low frequency noise produced at the base-emitter junction. The low-frequency noise behaviour of HBTs is important. To find out where the noise sources are located and which of these sources dominate, it is require to consider the dependences of the noise behaviour on transistor geometry, bias point, temperature and frequency.

#### 2.4.2 HBT Noise Model

The large-signal model employed is the FBH model developed for GaAs-based HBTs. The equivalent circuit containing noise sources is indicated in Figure 2.5. All resistances  $R_b, R_{b2}, R_e, R_c$  shows thermal noise at the actual junction temperature  $T_j$ . Shot noise is contained by two correlated noise sources. The current  $I_{be}$  is drive the base-emitter shot noise. The current  $I_f = \beta_f * I_{be}$  is drive the collector-emitter shot noise.

In Figure 2.6, all resistances generate thermal noise,  $\langle |i_b|^2 \rangle$  and  $\langle |i_c|^2 \rangle$  present shot noise. The sources at the base-emitter junction  $\langle |i_n * f_b|^2 \rangle$ , and at the emitter resistance  $\langle |v_n * f_e|^2 \rangle$  generate low-frequency noise. Additionally, the model considers the second noise source which represent the Hooge noise contribution of the bulk emitter.

In the equivalent circuit of combination for both intrinsic and extrinsic of HBT, Figure 2.7, the location of this noise is defined as "base-emitter noise source". In case of HBT models, the noise is effected by current and frequency.

Figure 2.5: Intrinsic large-signal of HBT and noise equivalent circuit []

In Figure 2.7, the base and emitter resistances  $R_b$ ,  $R_{b2}$ , and  $R_e$  are very low value in modern HBTs in order to achieve very low collector noise currents. Therefore, the base-emitter noise source is almost short circuited. The Oppositely, the noise for highimpedance source is not affected, because the emitter branch is almost connected to an open circuit which result the voltage noise source does not drive any current. The emitter noise source is mainly determined by the collector noise current.

#### 2.4.3 How the low-frequency noise sources are implemented

• Low-pass noise sources

The modelling interface of the circuit simulator provide low-frequency noise sources. In Figure 2.8, the noise level is effected by a function of current f (I), and the output of noise signal is low pass filtered.

• Cyclostationary noise sources

In Figure 2.9, a function of current f(I) is multiplied with a constant low-frequency noise. A sub circuit is implemented by using the instantaneous current when calculating the noise source through the simulator in order to get a cyclostationary source.

• Partly correlated cyclostationary noise sources

In Figure 2.10, the implementation is quite similar to the cyclostationary source, however it need to separated noise sources, and high-pass and low-pass filtering of the current.

Figure 2.6: Extrinsic large-signal of HBT and noise equivalent circuit []

# 2.5 Verilog-A

Verilog-A is a procedural language, with constructs similar to C and other languages. It offers simple constructs to describe the behavior of model for the simulator program. The program language allows circuit designers to create modules (behavioral blocks in a circuit) and define the characteristic of modules by specifying the mathematical relationships between the currents and voltages terminals of the modules. Verilog-A was recently enhanced to offer greater support for compact modeling. The NI AWR Design Environment provides a complete software solution, which promotes the compact model development. Due to its ease of use, efficient system design and powerful circuit simulation. Verilog-A can be used directly in circuit simulators - as well as parameter extraction of NI AWR Design Environment, which enable to handing measured data.

#### 2.5.1 Verilog-A Modules

A module is a unit of Verilog-A code that is used to describe a component. In Verilog-A, the built-in primitives depict common circuit components, such as capacitors, inductors, resistors and semiconductor devices. A module that simplify refers to other modules is known as a structural model. In Verilog-A, components are constructed by using branches and nodes. A node is defined as a point where endpoints of braches may connect, and a branch is defined as a single path between two terminal nodes. Nodes and braches are constrained by Kirchhoffs laws, which is represented as below:

- The flow enter into a node must always sum to zero.

- The potential is the same everywhere on a node

Figure 2.7: Large-signal and noise HBT equivalent circuit []

- The potential on a branch is equal to the difference potential between two nodes, which are connected.

- The flow enter into one terminal of a branch is always equal to the flow out of other terminal [1].

#### 2.5.2 Advantages of Verilog-A

The main reason for preferring Verilog-A for compact modeling rather than other generalpurpose programming languages is free the model developer from the burden of dealing with the simulator interface.

Generally, the modeling user interface of simulator in Brand A is quite difference to other modeling user interface of simulator in using and definition of variables. As a result of this, is very hard to implement the same model in different simulators without extra programing errors and compiling warnings, at the first trial. With Verilog-A, new models

Figure 2.8: Schematics illustrating the behaviour of low-frequency noise in large-signal excitation (low-pass noise) []

can be added nearly as quickly as the equations can be defined. Furthermore, it can maintain control of the intellectual performance of the model within various simulators.

Verilog-A also offers a powerful system for defining model parameters. The declaration statement contains the default value and can specify the range of effective values. The default value may also define as a function of other parameters, which is very useful to determine the relationship between input signal and output signal. As a result, Verilog-A is an extremely efficient program language for writing compact models [4].

**Figure 2.9:** Schematics illustrating the behaviour of low-frequency noise in large-signal excitation (cyclostationary noise) []

**Figure 2.10:** Schematic indicating implementation of the partly correlated cyclostationary noise source []

# Chapter 3

## **PDK Development Training**

## 3.1 PDK Overview

A process Design Kit is a complete set of files used within the semiconductor industry to model a fabrication process as the design tools, which are critical for design an integrated circuit. The PDK is identify by the foundry defining a certain technology variation for their process. The PDK can be used for design, simulate, draw and verify design, which improving design more efficiency, reducing the design cycle times and ensuring quality [6]. Basic on Figure 3.1 explains the detailed information of PDK and how it operation. The elements of a PDK are Device Symbols Device Symbols & View, Model, Parameterized Cell(PCell), Technology File, PV Rule and Documentation. These elements are required for each design state.

Figure 3.1: PDK Development Tools [5]

## 3.2 Installation Guide for AWR Foundry SDK and the Model Wizards

In order to approach the thesis project, we start with PDK development training. To get familiar with how implement model wizard in AWR and using Microsoft visual studio to test model. The NI AWR version 12 and Microsoft visual studio 2013 is required to download. The software development Kit(SDK) is download from the AWRCorp. web site. The AWR\_Dev Folder includes:

- AWR Folder includes the sample solution TEST\_SDK, which is used for verifying SDK installation and working samples

- Documentation Folder-includes training presentations and reference documents

- Generic-includes a sample PDK used for training

- SDKv12-includes the Model and Cell Wizards, and also contain the Lib files required to build PDK Solutions

- Supporting Files-include example projects [5]

According to instruction, we registering Model and Cell Wizards, ensure wizard installed correctly. Open the file AWR\_Dev\AWR\AWR.sln in Microsoft Visual Studio. We got the below message, which confirms the visual studio and AWR SDK setup correctly.

Figure 3.2: The output window of Visual studio [5]

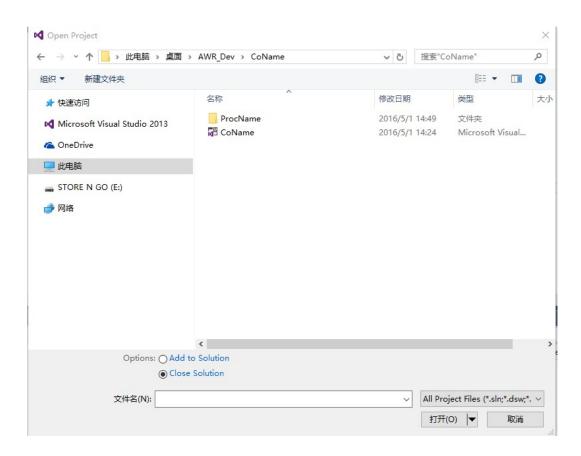

The Script is used to generate a new PDK process with a different name. We use companyName, CoName, and ProName as general names, which is showed as below:

The new PDK directory structure has all Visual Studio project. Open Microsoft visual studio allows to build the projects and verify the project build.

| 🎦 New AWR PDK              | Source Builder        | <b>—</b> × |

|----------------------------|-----------------------|------------|

| Foundry Name<br>CompanyNam | Foundry Abv<br>CoName | ОК         |

| Process Name<br>ProcName   |                       | Cancel     |

Figure 3.3: The "New AWR PDK Source Builder" dialog [5]

## 3.3 Getting started with the model Wizard

## 3.3.1 Overview

- The NI AWR design environment has various circuit simulators. Two simulator is named as AWR and Aplac. Both of them has linear and non-linear simulator. Both AWR and Aplac simulators can be used for any linear model. Non-linear models will require a dll for AWR and a different dll for Aplac simulator.

- Creating an aggregate model by importing it from the AWR schematic into the model wizard. Schematic can include both linear and nonlinear elements.

- The Model Wizard will produce C++ code, which is used for defines a new element.

- The following is an training by using the wizard to get code for a MIM capacitor [5].

## 3.3.2 MIM Cap imported from schematic

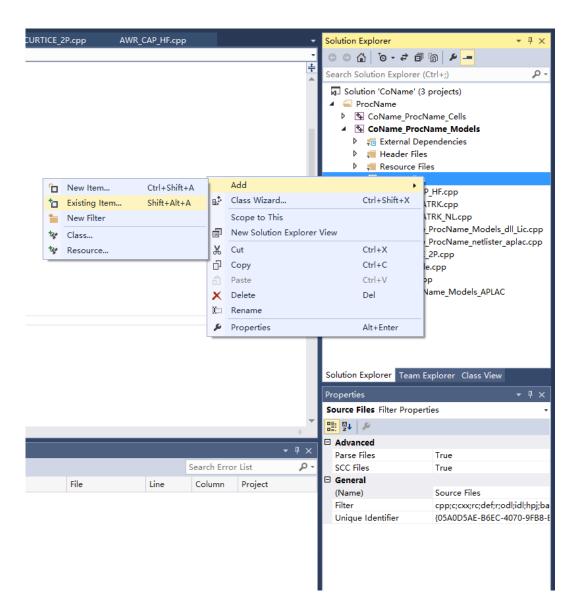

Start NI AWRDE and open the 'AWR\_CAP\_HF.emp' project file. No only we are allowed to fill the properties by modify Model parameters, and also allows to enter parameter formula, which define the behavior of capacitance. We launch Visual studio after the

model wizard create the .cpp file. Open the solution file by using MS Visual Studio. MS visual studio allows source code of AWR\_CAP\_HF to be add into the project. Therefore, we can test the model.

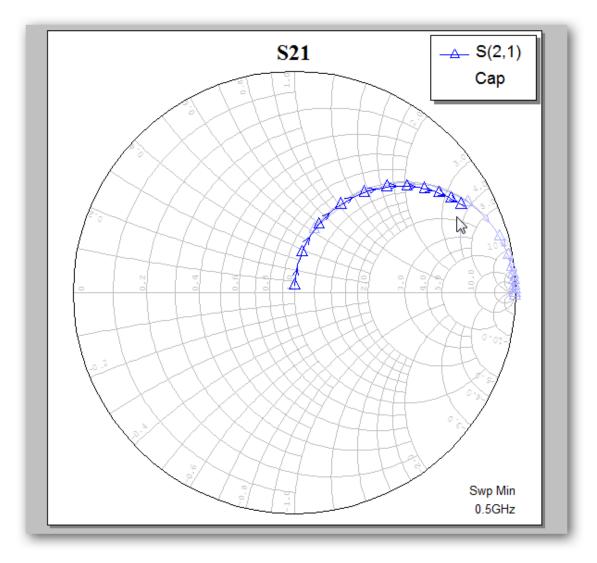

Create the schematic of cap and add S21 Smith Chart Graph. Edit and continue option in Visual Studio enables the user to debug a model source code by inspecting at the code and the simulation results in NI AWRDE simultaneously. By modify the equation for C to read C=CA\*W\*L. S21 Smith chart Graph is changed shows as below:

Figure 3.4: Result of Code change [5]

Edit and continue is effective for debugging models and making modify easily.

#### 3.3.3 Curtice FET with Parasitics

#### Overview

- This time will again be an aggregate model from a schematic

- The model is a Curtice FET with some extra parasitic.

- We add an Enumerate parameter to set a gate-gate pitch value

- The parasitic as a read-only parameter [5]

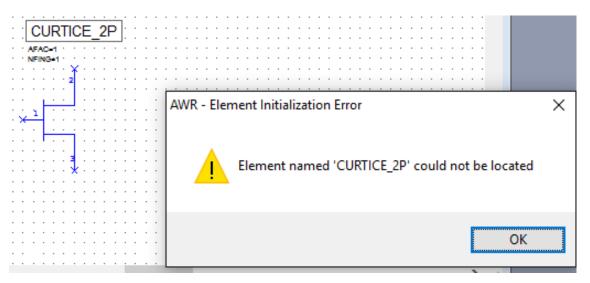

The execute procedure is pretty much similar to MIN Cap, instead we use Curtice FET and add more extra parasitic. There are some issues when add the model, which is named as Curtice\_2P. It shows as below:

Figure 3.5: CURTICE Model [5]

Figure 3.6 , because we tick hide model name. Therefore, NI AWR could not find element, which is named as 'CURTICE\_2P'.

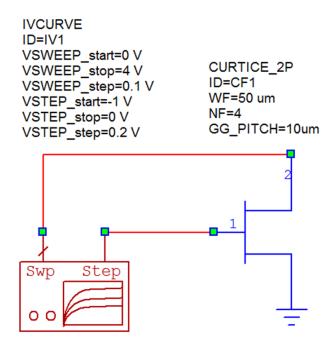

Basic on Figure 3.7, to determine the IV curve of CURTICE \_2P.

#### 3.3.4 Measure Internal Branch Current/Voltages

AWR nonlinear models allow to access the internal nodes of a nonlinear model by using branch labels. Adding branch labels directly to the Verilog-A allows the model wizard to deal with all of the branch labels automatically. Understanding Verilog-A is very important for achieve accurate models.

| Options         I hide model name         I hide model name         I hide model with same name and version         Is passive with default thermal noise         Create model block version. Mod block name:         Options         Dynamic symbols and/or number of terminals         Vue linear dass for linear dynamic models         Model Type         Y parameter representation         Paper specified (e.g., substrate definition)         Data model (e.g., substrate definition)         Shell model (can't be simulated with native simulators) | del Definition Parameters Implementation Netlist / Admittances Utility                                                                                           | Functions Source                                               |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| Create model block version. Mod block name: CURTICE_2Pd Binned model block. Instance name: CURTICE_2Pm CURTICE_2Pm CURTICE_2Pm Dynamic symbols and/or number of terminals Variable name Variable name Variable name Variable type Complex Variable name Variable initialization Complex New Delete Edit Variable Initialization Code Aggregate Model (can't be simulated with native simulators) Aggregate Model Options Suppress component warning messages                                                                                                  |                                                                                                                                                                  | Cache the model computation results                            |  |  |  |  |

| Dynanic symbols and/or number of terminals     Use linear dass for linear dynamic models  Model Type     Y-parameter representation     2-port branch model (no connection to ground)     Aggregate model (notific described)     Data model (e.g., substrate definition)     Shell model (can't be simulated with native simulators)                                                                                                                                                                                                                         | CURTICE_2Pd                                                                                                                                                      |                                                                |  |  |  |  |

| model (spe       New       Delete         2-port branch model (no connection to ground)       Aggregate model (netist described)       Edit Variable Initialization Code         © Data model (e.g., subtrate definition)       Shell model (can't be simulated with native simulators)       Aggregate Model Options                                                                                                                                                                                                                                         | Dynamic symbols and/or number of terminals                                                                                                                       |                                                                |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Y-parameter representation     2-port branch model (no connection to ground)     Aggregate model (netlist described)     Data model (e.g., substrate definition) | New         Delete           Edit Variable Initialization Code |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                  |                                                                |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                  |                                                                |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                  |                                                                |  |  |  |  |

Figure 3.6: NI AWRDE element browser [5]

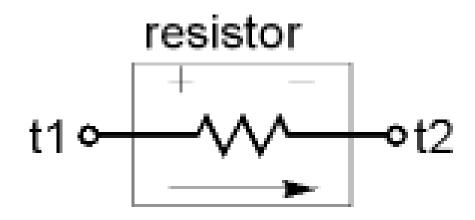

According to Figure 3.9, the first line defines the name of the component, in this case is resistor. Two pins, which are nodes are t1 and t2. The second line declares the nodes as being electrical, meaning that the potential of each node is a voltage and the flow into the node is a current. Verilog-A defines the flow into the pin to be positive if the motion is into the component. The third line declares a parameter, r for the component. The values of parameter can be specified when we instantiate the resistor. The value given in the parameter declaration is set as the default value of the parameter. The value of r is keep constant within the module. The fourth line declares a branch is named as res and it present t1 and t2 pins are connected [1].

$V(res) <+ r^*I(res)$  using of the contribution operator (<+) achieve this a contribution statement. It represents an equation that the voltage on branch res must equal to the current through branch multiplied by r [1].

#### 3.3.5 Analysis of issues

There are some issues occur during PDK development training. These may involve with AWR Version issue in simulation. The one we use is AWR V12, however the PDK development training is implement in AWR V11. Somehow, the simulation is not running in AWR V12, which may because some properties of AWR V12 is different with AWR V11. Configurations for Win32 platform and x64 platform used for test the model in Visual Studio, which only operate successful in x64 platform, but not Win32 platform. It may because our computer is running at 64-bits, that may not compatibility with Win32 platform.

Figure 3.7: Connect the VSWEEP\_step param to 1.0 to the Curtice\_2P [5]

Figure 3.8: Resistor Model [1]

# module resistor (t1, t2); electrical t1, t2; parameter real r=1; branch (t1, t2) res;

# analog V(res) <+ r\*I(res); endmodule

Figure 3.9: Resistor in Verilog-A [1]

## Chapter 4

# Create models in NI AWRDE PDK

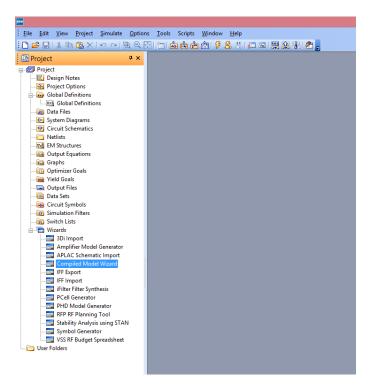

## 4.1 The Procedure of creating models

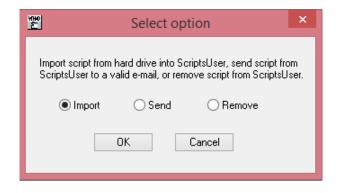

• Start NI AWRDE and choose Scripts  $\rightarrow$  Configuration  $\rightarrow$  Import\_Send\_Remove\_Script

Select Import and press OK.

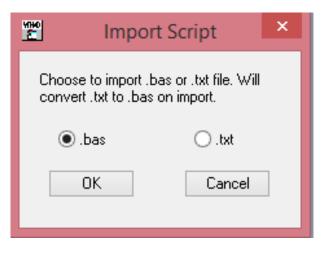

Select .bas and press OK.

- Browse to AWR\_Dev\SDKv12\ scripts\ MakeNewPDKProcess.bas to import it as a global script. The script will be appear in the Scripts menu when we restart Microwave office.

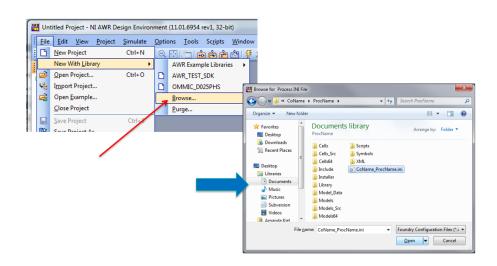

- Choose Scripts $\rightarrow$ PDK $\rightarrow$ Make\_New\_PDK\_Process

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |        |                                                                                                                                                                                                         |              |               |             | l                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-------------|------------------------------------------|

| <u>Eile Edit View Project Simulate Options</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>T</u> ools | Script | s <u>W</u> indow                                                                                                                                                                                        | <u>H</u> elp |               |             |                                          |

| <ul> <li>Inc and rew rote protect protect protect protect</li> <li>Project</li> <li>Project</li> <li>Design Notes</li> <li>Obsect options</li> <li>Optimizer Goals</li> <li>Output Files</li> <li>Output Files</li> <li>Output Files</li> <li>Output Files</li> <li>Simulation Filters</li> <li>Switch Lists</li> <li>User Folders</li> </ul> |               |        | Show_Help_P;<br>Configuration<br>Data<br>EM<br>Equations<br>Graphs<br>Layout<br>Load Pull<br>Models<br>Netlist<br>PDK<br>Project<br>Schematic<br>Simulation<br>VSS<br>Global Scripts<br>Project Scripts | ages_For_GI  | iobal_Scripts | <pre></pre> | Make_New_PDK_Process PDK_Version_Checker |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |        |                                                                                                                                                                                                         |              |               |             |                                          |

• The "New AWR PDK Source Builder" dialog is appeared. Fill it out.

| New AW                | /R PDK Source Builder    |

|-----------------------|--------------------------|

| Foundry<br>CompanyNam | Foundry Abv<br>CoName OK |

| Process<br>ProcName   | Cancel                   |

| Browse For Folder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Select the AWR SDK Directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _        |