### HIGH-SPEED LOW-POWER MODULAR ARITHMETIC FOR ELLIPTIC CURVE CRYPTOSYSTEMS BASED ON THE RESIDUE NUMBER SYSTEM

by

Shahzad Asif

Dissertation submitted in fulfilment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Engineering Faculty of Science and Engineering Macquarie University Sydney, Australia

December 2016

Copyright © 2016 Shahzad Asif

All Rights Reserved

#### STATEMENT OF CANDIDATE

I certify that the work in this thesis has not previously been submitted for a degree nor has it been submitted as part of the requirements for a degree to any other university or institution other than Macquarie University.

I also certify that the thesis is an original piece of research and it has been written by me.

In addition, I certify that all information sources and literature used are indicated in the thesis.

. . . . . . . . . . . . . . . . . . .

Shahzad Asif

Dedicated to

Hannan,

and

My parents, and my wife for their ongoing support and prayers.

#### ACKNOWLEDGMENTS

First of all I would like to thank my supervisor Dr Yinan Kong for his endless support and encouragement throughout my PhD candidature. His continuous encouragement, guidance, and feedback helped me to achieve the milestones in an efficient manner. I am also thankful to my fellow group members for their friendly discussion and appreciation. I wish to thank Selim Hossain for his help in the design and testing of proposed ECC architectures.

I express my sincere gratitude to Professor Joachim Rodrigues of the Department of Electrical and Information Technology (EIT) of Lund University, Sweden for providing me the opportunity to work under his guidance for the ASIC fabrication. His valuable feedback on my work greatly improved the quality of my research work. I am thankful for the digital ASIC research team at Lund University for their friendly and valuable discussions on my work and in general. My special thanks to Oskar Andersson for his continuous help and discussion in chip tapeout and measurement. I would like to thank Niras C.V. and Babak Mohammadi for their help in ASIC measurement. I am very grateful to ST Microelectronics for their financial support for the ASIC fabrication.

I am grateful to Dr Keith Imrie for his feedback and valuable comments on my thesis. I am thankful to the staff in the Department of Engineering for their support. Finally, I would like to acknowledge Macquarie University for awarding me an International Macquarie University Research Excellence Scholarship (iMQReS).

#### ABSTRACT

This thesis presents designs and hardware implementations of modular arithmetic for elliptic curve point multiplication (ECPM). The aim is to speed up elliptic curve cryptography (ECC) architectures and optimise their power consumption. Improvements are made in existing algorithms, and conventional number systems are replaced by residue number systems (RNS) to achieve a high speed for basic arithmetic operations. The proposed ECPM architectures are generic and can be scaled for different key sizes; the hardware implementations in this work are for 256-bit ECPM over prime field  $\mathbb{F}_p$ .

ECPM architectures are optimised in two ways. Firstly, three different hardware architectures are developed for the implementation of an efficient modular multiplier (MM). These architectures, named parallel, serial, and serial-parallel, offer a trade-off between area and delay. The performance of the proposed MM architectures is compared, based on their ASIC (Application Specific Integrated Circuit) and FPGA (Field Programmable Gate Array) implementation results. Moreover, the feasibility of serial MM architecture for practical implementation is proved by its ASIC fabrication using 65 nm CMOS technology. The measurement results for the fabricated chip show that the proposed MM is better than other state-of-the-art MM architectures.

Secondly, two ECPM architectures, named multi-key ECPM and single-key ECPM, are proposed; they differ in terms of throughput and hardware complexity. Multi-key ECPM provides a high throughput by processing twenty one keys simultaneously within deep pipeline stages. Single-key ECPM attempts to optimise the hardware cost by resource sharing. Power optimisation techniques are employed to reduce the power consumption of the single-key ECPM. The proposed architectures are implemented on FPGA and ASIC platforms and the results are analysed to discuss the suitability of the proposed ECPM architectures for different applications.

# Contents

| Ta            | Table of Contents     xiii |        |                                  |             |  |

|---------------|----------------------------|--------|----------------------------------|-------------|--|

| $\mathbf{Li}$ | st of                      | Figur  | es x                             | xi          |  |

| $\mathbf{Li}$ | st of                      | Table  | s xx                             | ٢V          |  |

| $\mathbf{Li}$ | st of                      | Publi  | cations xxv                      | 7 <b>ii</b> |  |

| 1             | Intr                       | oducti | ion                              | 1           |  |

|               | 1.1                        | Motiv  | ation for this Research          | 3           |  |

|               | 1.2                        | Objec  | tives of this Research           | 4           |  |

|               | 1.3                        | Thesis | Outline                          | 4           |  |

| <b>2</b>      | Bac                        | kgrou  | nd                               | 7           |  |

|               | 2.1                        | Introd | uction                           | 7           |  |

|               | 2.2                        | Residu | ie Number System                 | 8           |  |

|               |                            | 2.2.1  | Arithmetic Operations in the RNS | 9           |  |

|               |                            | 2.2.2  | The Chinese Remainder Theorem    | 10          |  |

|               |                            | 2.2.3  | RNS Moduli Set Selection         | 11          |  |

|               |                            | 2.2.4  | Scaling in the RNS               | 12          |  |

|               |                            | 2.2.5  | Modular Reduction in RNS         | 12          |  |

|   | 2.3 | Modul   | ar Multipliers                                                          | 13 |

|---|-----|---------|-------------------------------------------------------------------------|----|

|   |     | 2.3.1   | Overview of Existing Modular Multiplication Architectures in Bi-        |    |

|   |     |         | nary Number System                                                      | 13 |

|   |     | 2.3.2   | Overview of Existing Modular Multiplication Architectures in Residue    |    |

|   |     |         | Number System                                                           | 16 |

|   | 2.4 | Ellipti | c Curve Point Multiplication                                            | 18 |

|   |     | 2.4.1   | Mathematical Background                                                 | 18 |

|   |     | 2.4.2   | Elliptic Curve Parameters over $\mathbb{F}_p$ on Koblitz Curve          | 22 |

|   |     | 2.4.3   | Overview of Existing ECPM Architectures in Binary Number Sys-           |    |

|   |     |         | tem over $\mathbb{F}_p$                                                 | 22 |

|   |     | 2.4.4   | Overview of Existing ECPM Architectures in Residue Number System        | 24 |

| 3 | Cou | inter-E | Based Wallace Multipliers                                               | 29 |

|   | 3.1 | Introd  | uction                                                                  | 29 |

|   | 3.2 | Wallac  | e Multipliers                                                           | 29 |

|   | 3.3 | High-S  | Speed Counters                                                          | 31 |

|   |     | 3.3.1   | 7:3 Counter                                                             | 31 |

|   |     | 3.3.2   | 6:3 Counter                                                             | 32 |

|   |     | 3.3.3   | 5:3 Counter                                                             | 32 |

|   |     | 3.3.4   | 4:3 Counter                                                             | 34 |

|   |     | 3.3.5   | 3:2 Counter (Full Adder) and 2:2 Counter (HA)                           | 35 |

|   | 3.4 | Propo   | sed Counter-Based Wallace Multipliers                                   | 36 |

|   |     | 3.4.1   | Architecture-1 – Maximum Usage of Counters                              | 40 |

|   |     | 3.4.2   | Architecture-2 – Reduced Utilisation of 2:2 Counters                    | 40 |

|   |     | 3.4.3   | Architecture-3 $-$ Reduced Utilisation of 2:2 and 3:2 Counters $\ .$    | 43 |

|   |     | 3.4.4   | Architecture-4 $-$ Reduced Utilisation of 2:2, 3:2, and 4:3 Counters .  | 45 |

|   |     | 3.4.5   | Architecture-5 – Reduced Utilisation of 2:2, 3:2, 4:3, and 5:3 Counters | 47 |

\_\_\_\_\_

|                         | 3.4.6                                                                   | Architecture-6 – Reduced Utilisation of 2:2, 3:2, 4:3, 5:3, and 6:3                                                                                                                                                                        |                                                                                                            |

|-------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                         |                                                                         | Counters                                                                                                                                                                                                                                   | 47                                                                                                         |

|                         | 3.4.7                                                                   | Architecture-7 – Maximum Utilisation of 3:2 Counters $\ldots$ .                                                                                                                                                                            | 50                                                                                                         |

|                         | 3.4.8                                                                   | Final Adder Design                                                                                                                                                                                                                         | 52                                                                                                         |

|                         | 3.4.9                                                                   | Interconnection Complexity Analysis of Proposed Architectures                                                                                                                                                                              | 55                                                                                                         |

| 3.5                     | Propo                                                                   | sed Booth-Encoded Wallace Multiplier                                                                                                                                                                                                       | 56                                                                                                         |

| 3.6                     | Refere                                                                  | ence Multiplier                                                                                                                                                                                                                            | 59                                                                                                         |

| 3.7                     | Imple                                                                   | mentation of the Proposed Architectures                                                                                                                                                                                                    | 63                                                                                                         |

|                         | 3.7.1                                                                   | Functional Verification                                                                                                                                                                                                                    | 63                                                                                                         |

|                         | 3.7.2                                                                   | Synthesis Tool                                                                                                                                                                                                                             | 63                                                                                                         |

|                         | 3.7.3                                                                   | Power Analysis                                                                                                                                                                                                                             | 65                                                                                                         |

| 3.8                     | Analy                                                                   | sis and Comparison of Synthesis Results                                                                                                                                                                                                    | 65                                                                                                         |

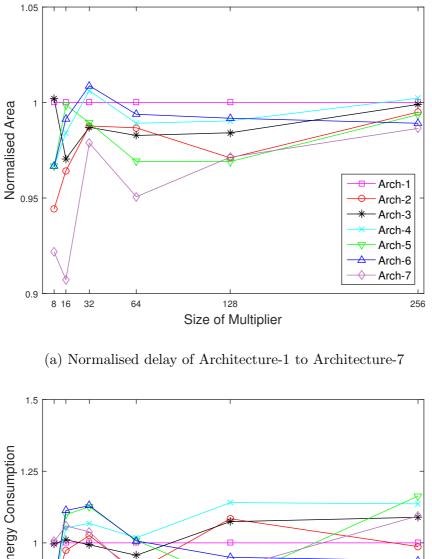

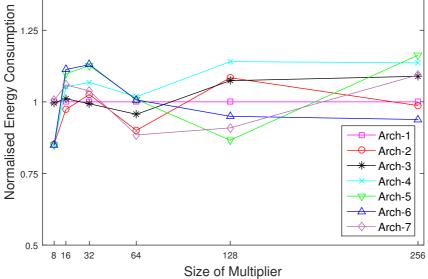

|                         | 3.8.1                                                                   | CBW Multipliers (Architectures 1–7)                                                                                                                                                                                                        | 65                                                                                                         |

|                         | 3.8.2                                                                   | Wallace, Booth-Wallace, CBW, and Booth-CBW Multipliers                                                                                                                                                                                     | 68                                                                                                         |

|                         |                                                                         | · · · · · ·                                                                                                                                                                                                                                |                                                                                                            |

| 3.9                     | Summ                                                                    | ary of Results                                                                                                                                                                                                                             | 72                                                                                                         |

|                         |                                                                         |                                                                                                                                                                                                                                            | 72<br><b>73</b>                                                                                            |

|                         | dular I                                                                 | ary of Results                                                                                                                                                                                                                             |                                                                                                            |

| Mo                      | <b>dular</b> 1<br>Introd                                                | Multiplier Using Sum of Residues in RNS                                                                                                                                                                                                    | 73                                                                                                         |

| <b>Mo</b><br>4.1        | dular I<br>Introd<br>The M                                              | Multiplier Using Sum of Residues in RNS                                                                                                                                                                                                    | <b>73</b><br>73<br>74                                                                                      |

| <b>Mo</b><br>4.1        | dular I<br>Introd<br>The M                                              | hary of Results                                                                                                                                                                                                                            | <b>73</b><br>73<br>74                                                                                      |

| <b>Mo</b><br>4.1        | dular 1<br>Introd<br>The M<br>4.2.1<br>4.2.2                            | hary of Results                                                                                                                                                                                                                            | <b>73</b><br>73<br>74<br>74                                                                                |

| <b>Mo</b><br>4.1<br>4.2 | dular 1<br>Introd<br>The M<br>4.2.1<br>4.2.2                            | hary of Results                                                                                                                                                                                                                            | <b>73</b><br>73<br>74<br>74<br>76                                                                          |

| <b>Mo</b><br>4.1<br>4.2 | dular I<br>Introd<br>The N<br>4.2.1<br>4.2.2<br>The R                   | hary of Results                                                                                                                                                                                                                            | <b>73</b><br>73<br>74<br>74<br>76<br>78                                                                    |

| <b>Mo</b><br>4.1<br>4.2 | dular I<br>Introd<br>The M<br>4.2.1<br>4.2.2<br>The R<br>4.3.1          | Multiplier Using Sum of Residues in RNS         Juction         Iduction within RNS Channels         The Barrett Modular Reduction Algorithm         Bound Deduction         CNS Modular Multiplication Algorithm         Moduli Selection | <ul> <li>73</li> <li>73</li> <li>74</li> <li>74</li> <li>76</li> <li>78</li> <li>79</li> </ul>             |

| <b>Mo</b><br>4.1<br>4.2 | dular I<br>Introd<br>The M<br>4.2.1<br>4.2.2<br>The R<br>4.3.1<br>4.3.2 | hary of Results                                                                                                                                                                                                                            | <ul> <li>73</li> <li>73</li> <li>74</li> <li>74</li> <li>76</li> <li>78</li> <li>79</li> <li>80</li> </ul> |

|                         | 3.6<br>3.7                                                              | 3.4.7<br>3.4.8<br>3.4.9<br>3.5 Propo<br>3.6 Refere<br>3.7 Impler<br>3.7.1<br>3.7.2<br>3.7.3<br>3.8 Analy<br>3.8.1                                                                                                                          | Counters                                                                                                   |

|   |                   | 4.3.6                                                                                    | Proposed RNS Moduli and Pre-computed Values                                                                                                                                                                                                                                                                                               | <i>)</i> 1                                                     |

|---|-------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|   |                   | 4.3.7                                                                                    | A Design Example                                                                                                                                                                                                                                                                                                                          | 94                                                             |

|   |                   | 4.3.8                                                                                    | Complexity Analysis                                                                                                                                                                                                                                                                                                                       | 97                                                             |

|   | 4.4               | Propo                                                                                    | sed Architectures                                                                                                                                                                                                                                                                                                                         | )1                                                             |

|   |                   | 4.4.1                                                                                    | Parallel Architecture                                                                                                                                                                                                                                                                                                                     | )1                                                             |

|   |                   | 4.4.2                                                                                    | Serial Architecture                                                                                                                                                                                                                                                                                                                       | )3                                                             |

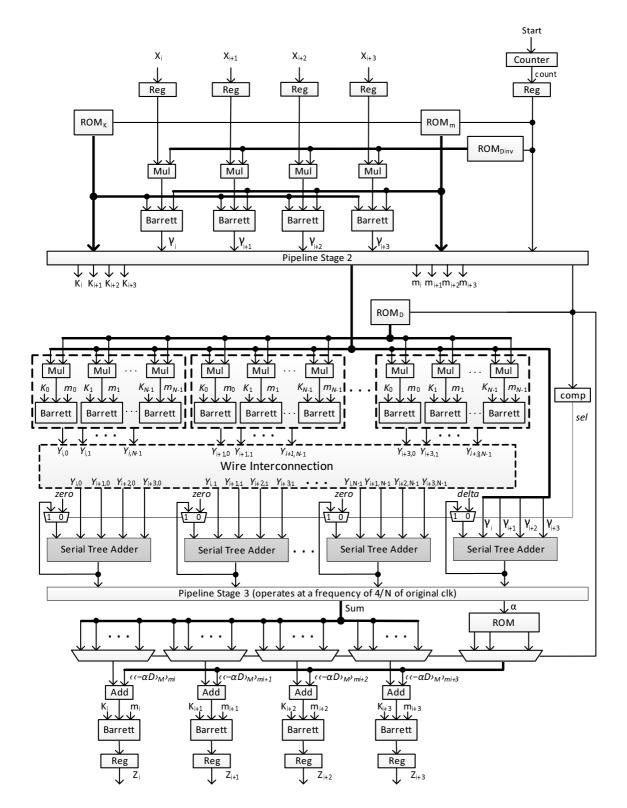

|   |                   | 4.4.3                                                                                    | Serial-Parallel Architecture                                                                                                                                                                                                                                                                                                              | )7                                                             |

|   | 4.5               | Imple                                                                                    | mentation of the Proposed Architectures                                                                                                                                                                                                                                                                                                   | )9                                                             |

|   |                   | 4.5.1                                                                                    | FPGA Implementation                                                                                                                                                                                                                                                                                                                       | )9                                                             |

|   |                   | 4.5.2                                                                                    | ASIC Implementation                                                                                                                                                                                                                                                                                                                       | 12                                                             |

|   |                   | 4.5.3                                                                                    | Power Analysis                                                                                                                                                                                                                                                                                                                            | 12                                                             |

|   | 4.6               | Analy                                                                                    | sis and Comparison of Results                                                                                                                                                                                                                                                                                                             | 13                                                             |

|   | 4.7               | Summ                                                                                     | ary of Results                                                                                                                                                                                                                                                                                                                            | 17                                                             |

|   |                   |                                                                                          |                                                                                                                                                                                                                                                                                                                                           |                                                                |

| 5 | $\mathbf{Chi}$    | p Fabr                                                                                   | ication for RNS-based Modular Multiplier 11                                                                                                                                                                                                                                                                                               | .9                                                             |

| 5 | <b>Chi</b><br>5.1 | -                                                                                        | ication for RNS-based Modular Multiplier 11 Modular Multiplier                                                                                                                                                                                                                                                                            |                                                                |

| 5 |                   | -                                                                                        | -                                                                                                                                                                                                                                                                                                                                         | 19                                                             |

| 5 |                   | Serial                                                                                   | Modular Multiplier                                                                                                                                                                                                                                                                                                                        | 19<br>19                                                       |

| 5 |                   | Serial<br>5.1.1                                                                          | Modular Multiplier                                                                                                                                                                                                                                                                                                                        | 19<br>19<br>21                                                 |

| 5 |                   | Serial<br>5.1.1<br>5.1.2<br>5.1.3                                                        | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12                                                                                                                                                                                                                                    | 19<br>19<br>21<br>23                                           |

| 5 | 5.1               | Serial<br>5.1.1<br>5.1.2<br>5.1.3                                                        | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12         Buffer Selection       12                                                                                                                                                                                                  | 19<br>19<br>21<br>23<br>25                                     |

| 5 | 5.1               | Serial<br>5.1.1<br>5.1.2<br>5.1.3<br>Chip 7                                              | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12         Buffer Selection       12         Fapeout       12                                                                                                                                                                         | 19<br>19<br>21<br>23<br>25<br>25                               |

| 5 | 5.1               | Serial<br>5.1.1<br>5.1.2<br>5.1.3<br>Chip 7<br>5.2.1                                     | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12         Buffer Selection       12         Fapeout       12         Synthesis using Synopsys Design Compiler       12                                                                                                               | 19<br>19<br>21<br>23<br>25<br>25<br>27                         |

| 5 | 5.1               | Serial<br>5.1.1<br>5.1.2<br>5.1.3<br>Chip 7<br>5.2.1<br>5.2.2                            | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12         Buffer Selection       12         Fapeout       12         Synthesis using Synopsys Design Compiler       12         Place and Route using Cadence Encounter       12                                                      | 19<br>19<br>21<br>23<br>25<br>25<br>27<br>30                   |

| 5 | 5.1               | Serial<br>5.1.1<br>5.1.2<br>5.1.3<br>Chip 7<br>5.2.1<br>5.2.2<br>5.2.3                   | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12         Buffer Selection       12         Fapeout       12         Synthesis using Synopsys Design Compiler       12         Place and Route using Cadence Encounter       12         Power Analysis       13                      | 19<br>19<br>21<br>23<br>25<br>25<br>27<br>30<br>30             |

| 5 | 5.1               | Serial<br>5.1.1<br>5.1.2<br>5.1.3<br>Chip 7<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | Modular Multiplier       11         Design Modification       11         Design of Test Bench       12         Buffer Selection       12         Fapeout       12         Synthesis using Synopsys Design Compiler       12         Place and Route using Cadence Encounter       13         Chip Tapeout Using Cadence Virtuoso       13 | 19<br>19<br>21<br>23<br>25<br>25<br>25<br>27<br>30<br>30<br>36 |

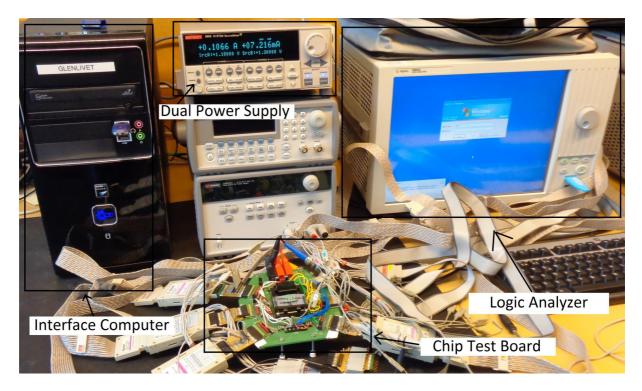

|   |      | 5.3.2   | Measurement Setup                                                                                                                           |

|---|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

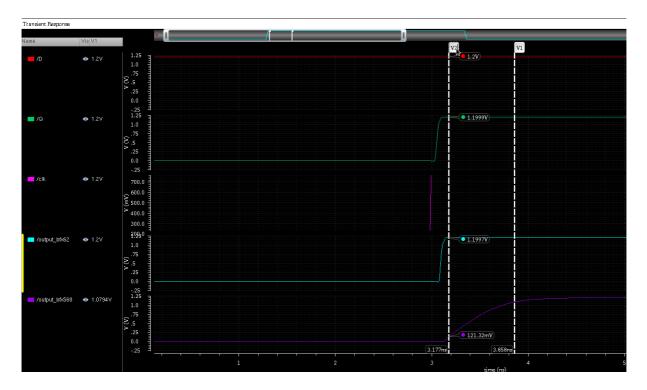

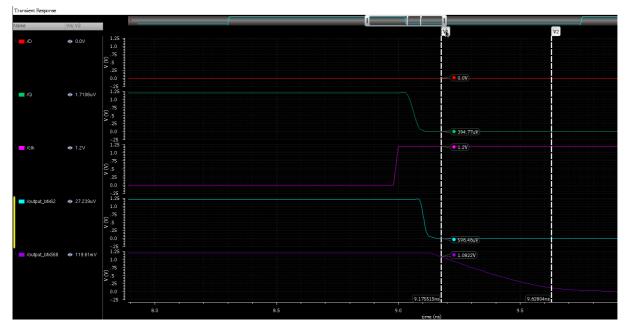

|   |      | 5.3.3   | Observation of Results                                                                                                                      |

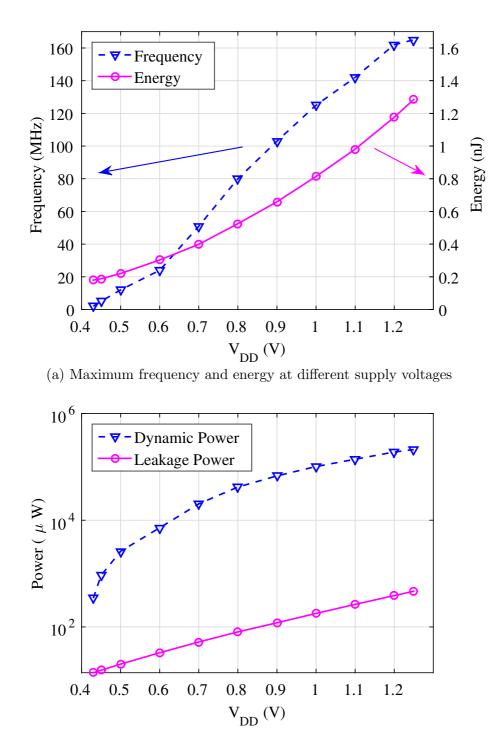

|   | 5.4  | Analy   | sis and Comparison of Results                                                                                                               |

|   |      | 5.4.1   | ASIC Measurement Results                                                                                                                    |

|   |      | 5.4.2   | Comparison with State-of-the-art                                                                                                            |

|   | 5.5  | Summ    | ary of Results                                                                                                                              |

| 6 | Elli | ptic C  | urve Point Multiplication 151                                                                                                               |

|   | 6.1  | Introd  | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $151$                                                                          |

|   | 6.2  | Modu    | lar Reduction using Sum of Residues                                                                                                         |

|   |      | 6.2.1   | Serial Architecture of Modular Reduction                                                                                                    |

|   |      | 6.2.2   | Serial-Parallel Architecture of Modular Reduction                                                                                           |

|   | 6.3  | RNS I   | Modular Subtraction                                                                                                                         |

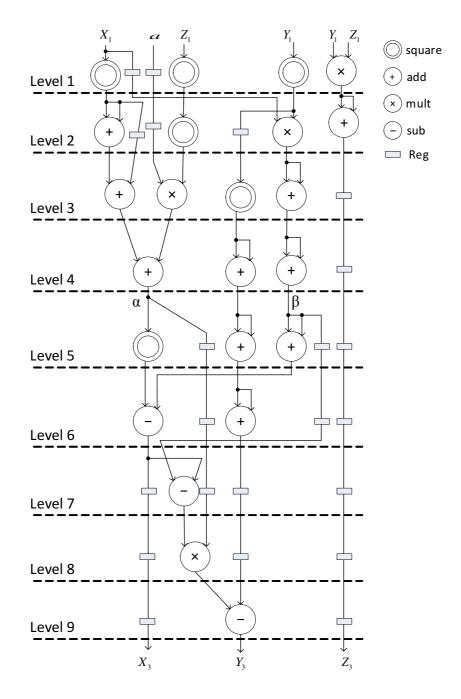

|   | 6.4  | Ellipti | c Curve Point Doubling in Jacobian Coordinates                                                                                              |

|   |      | 6.4.1   | Optimisation – Elimination of Unnecessary Modular Reductions 162                                                                            |

|   |      | 6.4.2   | RNS Subtraction - Modified for Larger Inputs                                                                                                |

|   |      | 6.4.3   | Elliptic Curve Point Doubling Implementation                                                                                                |

|   | 6.5  | Ellipti | c Curve Point Addition in Jacobian Coordinates                                                                                              |

|   |      | 6.5.1   | Optimisation – Elimination of Unnecessary Modular Reductions 169                                                                            |

|   |      | 6.5.2   | Elliptic Curve Point Addition Implementation                                                                                                |

|   | 6.6  | Ellipti | c Curve Point Multiplication – Multi-Key Based on Serial Modular                                                                            |

|   |      | Reduc   | tion $\ldots \ldots \ldots$ |

|   |      | 6.6.1   | Cycles for One Iteration of Multi-Key ECPM                                                                                                  |

|   |      | 6.6.2   | Invalid inputs for ECPA                                                                                                                     |

|   |      | 6.6.3   | Clock Cycles for Multi-Key ECPM                                                                                                             |

|   | 6.7  | Ellipti | c Curve Point Multiplication - Single-Key With Resource Sharing $181$                                                                       |

|   |      | 6.7.1   | Sub-Modules of Single-Key ECPM Architecture                                                                                                 |

|              |     | 6.7.2   | Area Optimisation – Reordering of Operations in ECPD and ECPA  | 188 |

|--------------|-----|---------|----------------------------------------------------------------|-----|

|              |     | 6.7.3   | Delay Optimisation - Merging ECPD and ECPA                     | 191 |

|              |     | 6.7.4   | Area Optimisation – Reordering of Merged ECPD-ECPA to Reduce   |     |

|              |     |         | Concurrent Modular Reductions                                  | 193 |

|              |     | 6.7.5   | Power Optimisation – Switching Off Idle Components             | 195 |

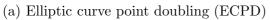

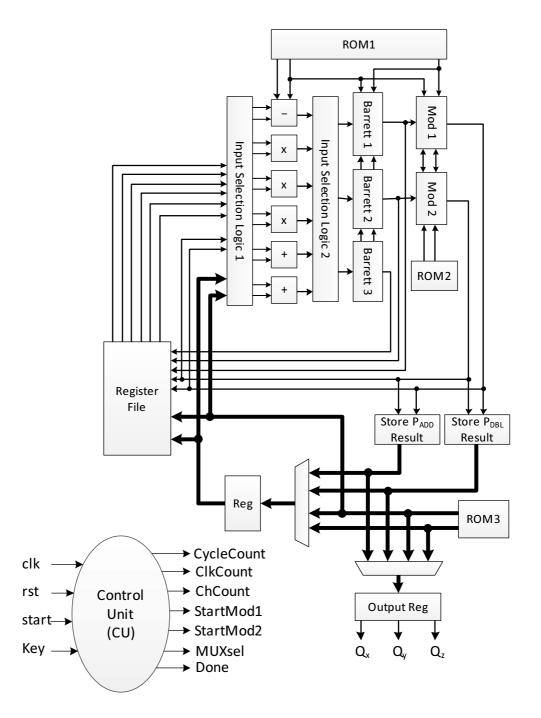

|              |     | 6.7.6   | Block Diagram of Optimised Single-Key ECPM Architecture        | 195 |

|              |     | 6.7.7   | Clock Cycles for Single-Key ECPM Based on Serial Modular Re-   |     |

|              |     |         | duction                                                        | 196 |

|              |     | 6.7.8   | Clock Cycles for Single-Key ECPM Based on Serial-Parallel Mod- |     |

|              |     |         | ular Reduction                                                 | 198 |

|              | 6.8 | Hardw   | vare Implementation and Analysis of Results                    | 199 |

|              |     | 6.8.1   | FPGA Implementations of Proposed ECPM Architectures            | 199 |

|              |     | 6.8.2   | ASIC Implementations of Proposed ECPM Architectures            | 202 |

|              | 6.9 | Summ    | ary of Results                                                 | 204 |

| 7            | Con | clusio  | ns and Future Work                                             | 207 |

|              | 7.1 | Conclu  | usions                                                         | 207 |

|              | 7.2 | Future  | e Research Directions                                          | 212 |

| $\mathbf{A}$ | TC  | L Scrip | ots for Counter-Based Wallace Multiplier                       | 215 |

|              | A.1 | TCL s   | cript for Synthesis in Design Compiler                         | 215 |

|              | A.2 | TCL S   | Script for Power Analysis in Prime Time                        | 218 |

| в            | TC  | L Scrip | ots for Modular Multipliers                                    | 219 |

|              | B.1 | Pipeli  | ned Parallel Modular Multiplier                                | 219 |

|              |     | B.1.1   | TCL script for Synthesis in Design Compiler                    | 219 |

|              |     | B.1.2   | TCL Script for Power Analysis in Prime Time                    | 223 |

|              |     |         |                                                                |     |

|              |                       | B.2.1   | TCL script for Synthesis in Design Compiler               | . 223      |

|--------------|-----------------------|---------|-----------------------------------------------------------|------------|

|              |                       | B.2.2   | TCL Script for Power Analysis in Prime Time               | . 227      |

| С            | Scri                  | pts foi | r Chip Fabrication of Serial Modular Multiplier           | 229        |

|              | C.1                   | Synthe  | esis in Design Compiler                                   | . 229      |

|              | C.2                   | Multip  | ble Power Domains Using Common Power Format (CPF)         | . 232      |

|              | C.3                   | Locati  | on of Pads (pads.io)                                      | . 234      |

|              | C.4                   | Floorp  | blan, Power Planning, and Placement                       | . 236      |

|              | C.5                   | Clock   | Tree Synthesis (CTS)                                      | . 240      |

|              | C.6                   | Routir  | ng and Verification                                       | . 241      |

|              | C.7                   | SKILI   | scripts                                                   | . 243      |

| D            | TC                    | L Scrip | ots for Elliptic Curve Point Multiplication Architectures | <b>245</b> |

|              | D.1                   | Multi-  | key ECPM Based on Serial Modular Reduction                | . 245      |

|              |                       | D.1.1   | TCL script for Synthesis in Design Compiler               | . 245      |

|              |                       | D.1.2   | TCL Script for Power Analysis in Prime Time               | . 249      |

|              | D.2                   | Single  | -Key ECPM Based on Serial-Parallel Modular Reduction      | . 249      |

|              |                       | D.2.1   | TCL script for Synthesis in Design Compiler               | . 249      |

|              |                       | D.2.2   | TCL Script for Power Analysis in Prime Time               | . 253      |

| $\mathbf{E}$ | FPO                   | GA Pla  | atforms Used in the Implementations                       | 255        |

| $\mathbf{F}$ | $\operatorname{List}$ | of Ac   | ronyms                                                    | 257        |

| Re           | efere                 | nces    |                                                           | 260        |

# List of Figures

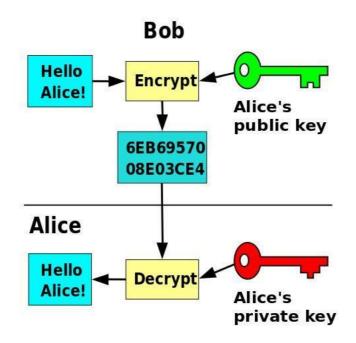

| 1.1  | Classical example of public-key cryptography                  | 2  |

|------|---------------------------------------------------------------|----|

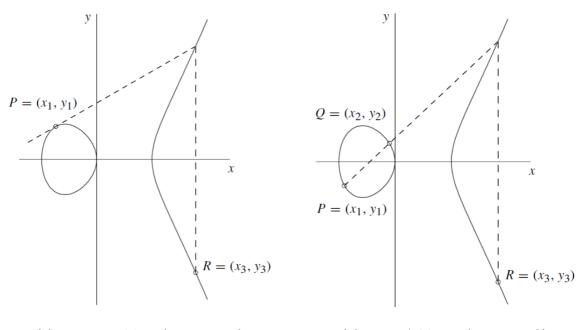

| 2.1  | Point Doubling and Point Addition on Elliptic Curve [1]       | 19 |

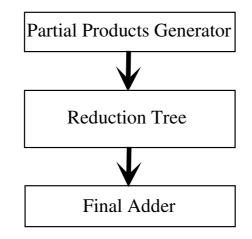

| 3.1  | Block diagram of Wallace multipliers                          | 30 |

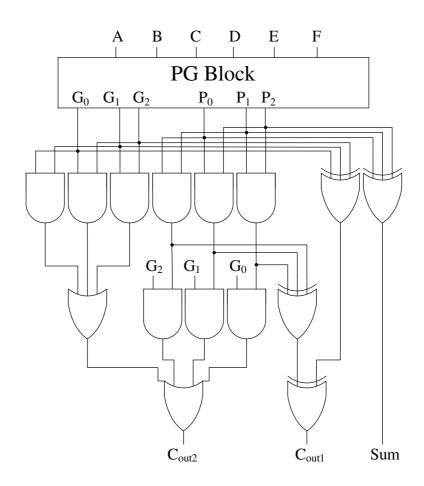

| 3.2  | 6:3 Counter                                                   | 33 |

| 3.3  | 5:3 Counter                                                   | 34 |

| 3.4  | 4:3 Counter                                                   | 35 |

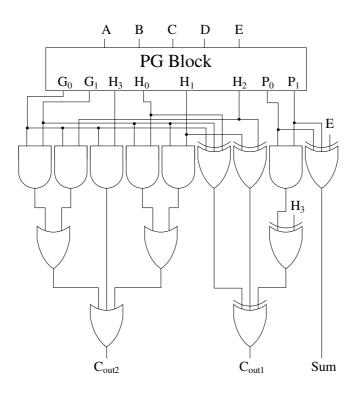

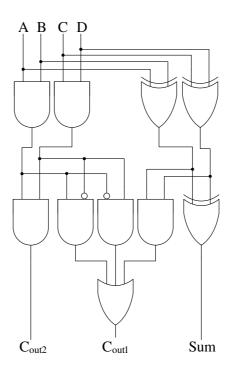

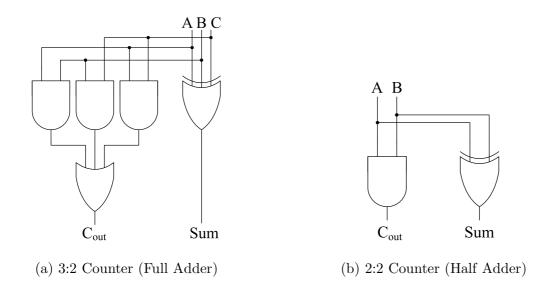

| 3.5  | Circuit Diagrams of 3:2 and 2:2 Counters                      | 36 |

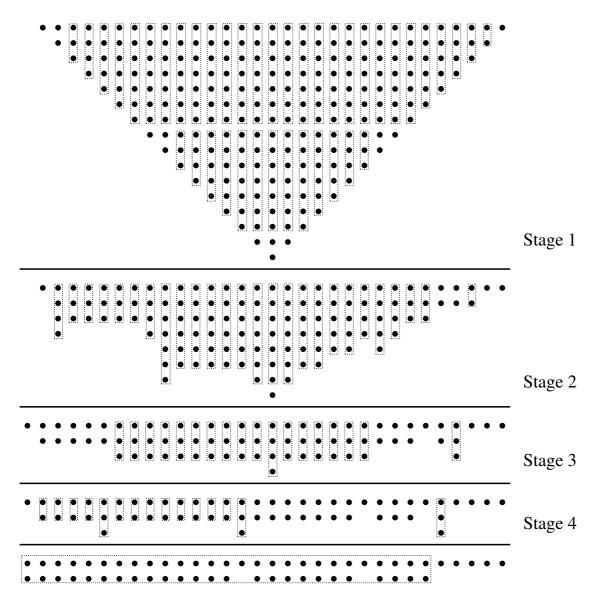

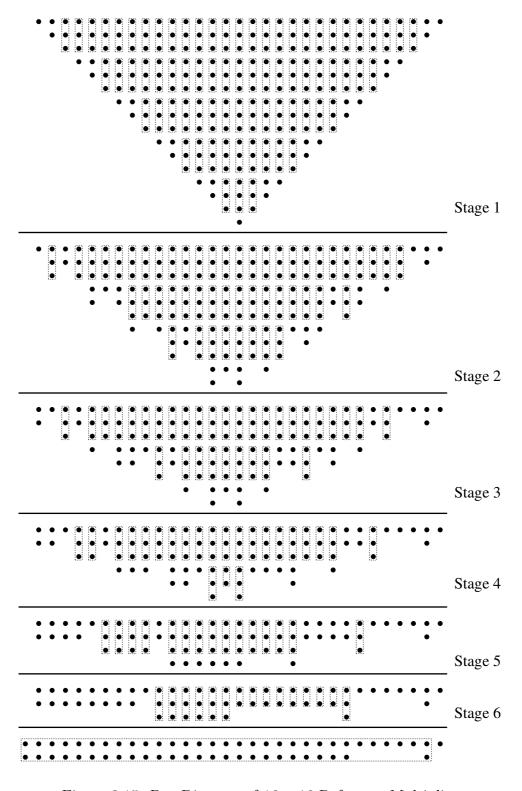

| 3.6  | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-1 | 41 |

| 3.7  | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-2 | 42 |

| 3.8  | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-3 | 44 |

| 3.9  | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-4 | 46 |

| 3.10 | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-5 | 48 |

| 3.11 | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-6 | 49 |

| 3.12 | Dot Diagram of 16 $\times$ 16 CBW Multiplier - Architecture-7 | 51 |

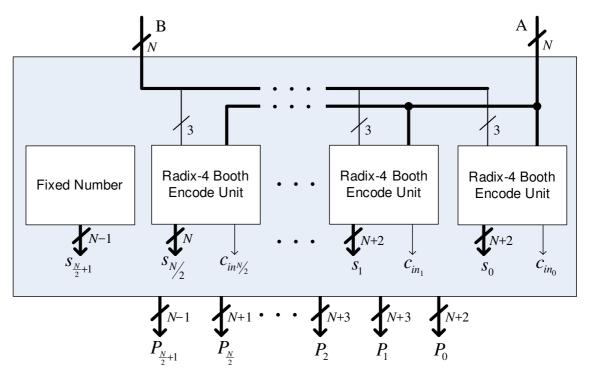

| 3.13 | Block diagram of radix-4 Booth encoding                       | 57 |

| 3.14 | Illustration of an 8-bit Radix-4 Booth Encoder                | 60 |

| 3.15 | Dot Diagram of $16 \times 16$ Reference Multiplier            | 61 |

| 3.16 | Area and energy results of proposed CBW architectures         | 66 |

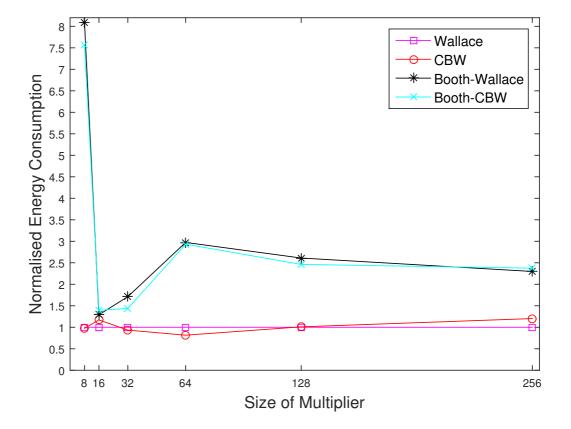

| 3.17 | Normalised energy dissipation of proposed and reference multipliers 71               |

|------|--------------------------------------------------------------------------------------|

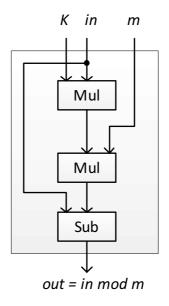

| 4.1  | Barrett modular reduction within RNS channels                                        |

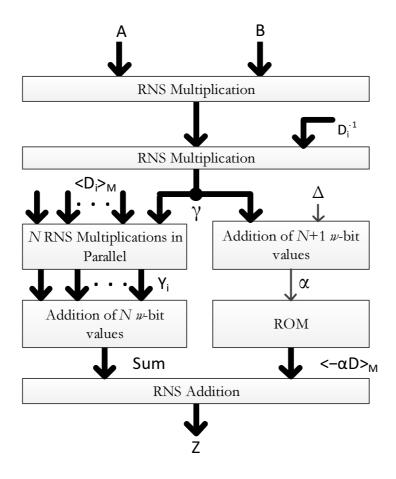

| 4.2  | RNS modular multiplication flow chart of Algorithm 6 90                              |

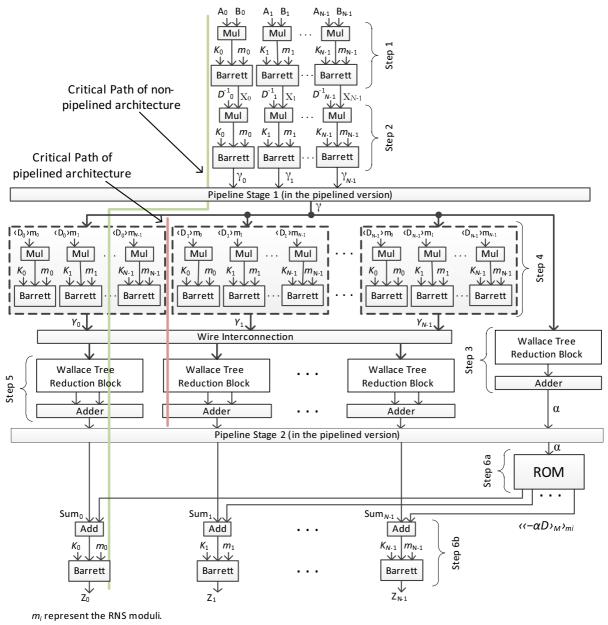

| 4.3  | Highly Parallel Architecture of RNS MM                                               |

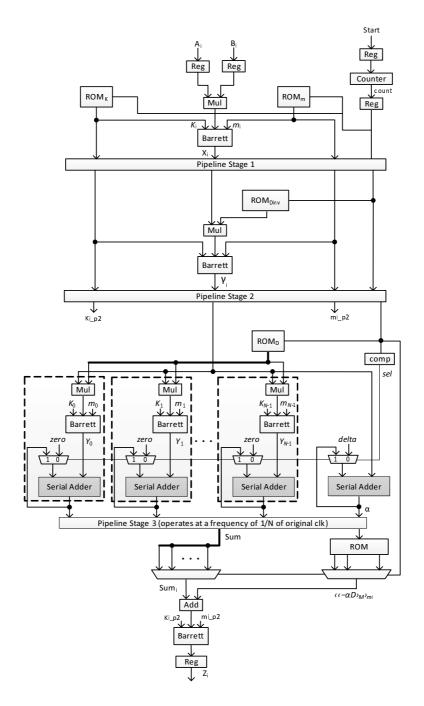

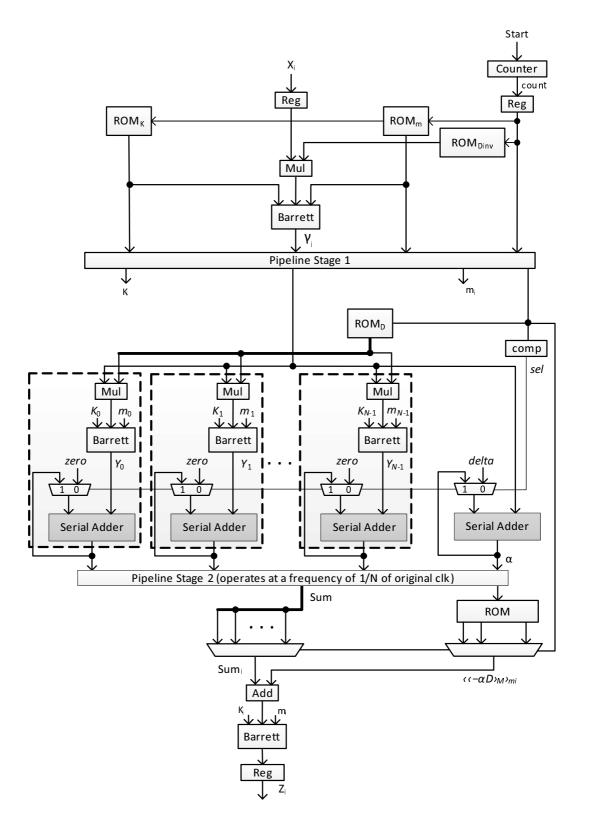

| 4.4  | Serial Architecture of RNS MM                                                        |

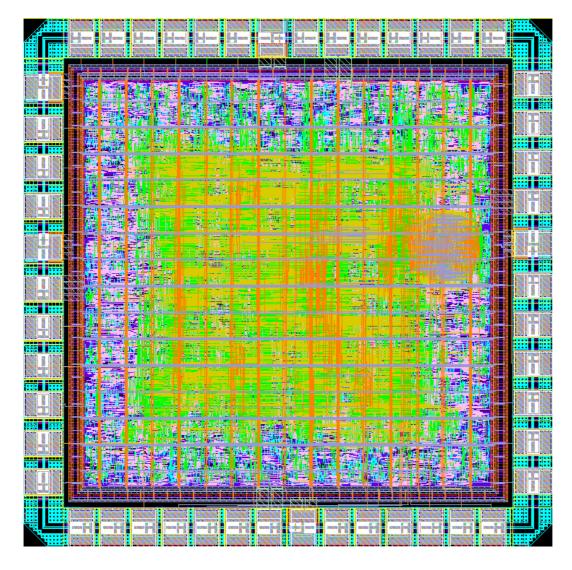

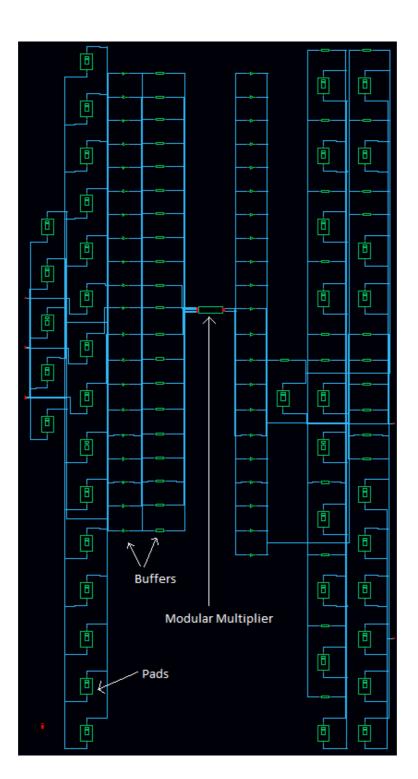

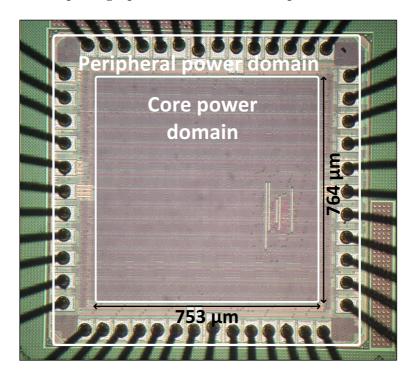

| 4.5  | RNS-based modular multiplier chip layout                                             |

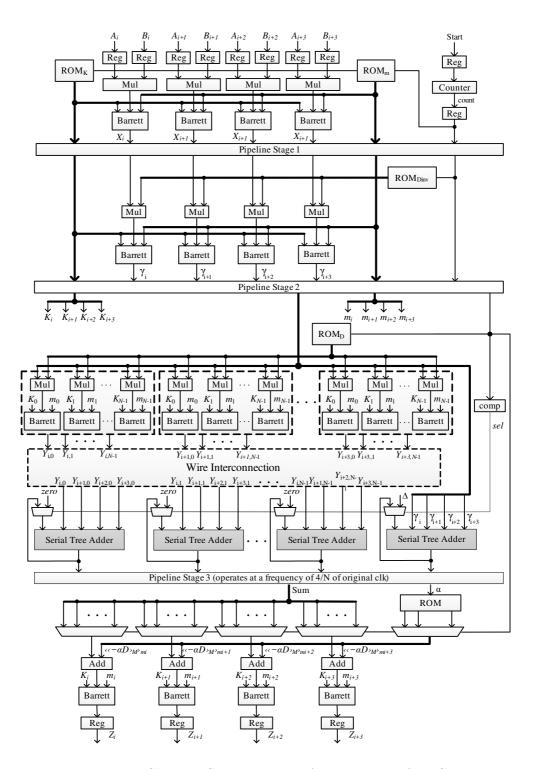

| 4.6  | 4-Channel Serial-Parallel Architecture of RNS MM                                     |

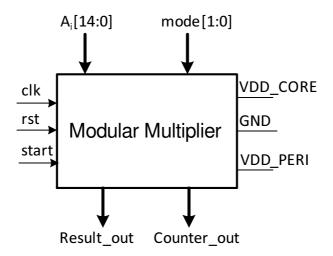

| 5.1  | Block diagram of the fabricated design of modular multiplier                         |

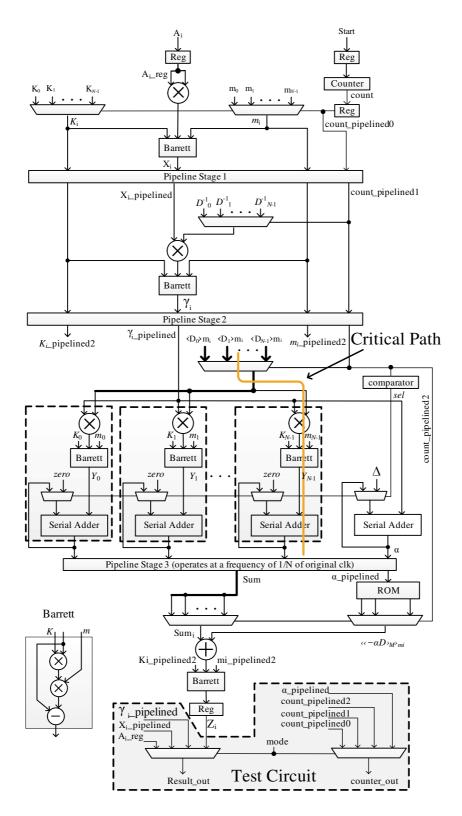

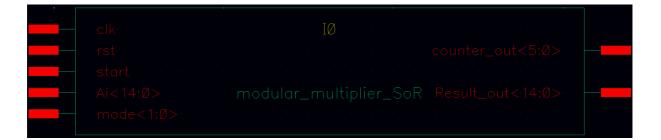

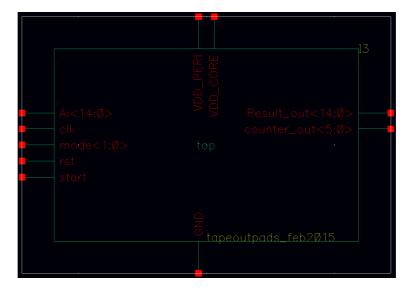

| 5.2  | Circuit diagram of the fabricated design of modular multiplier                       |

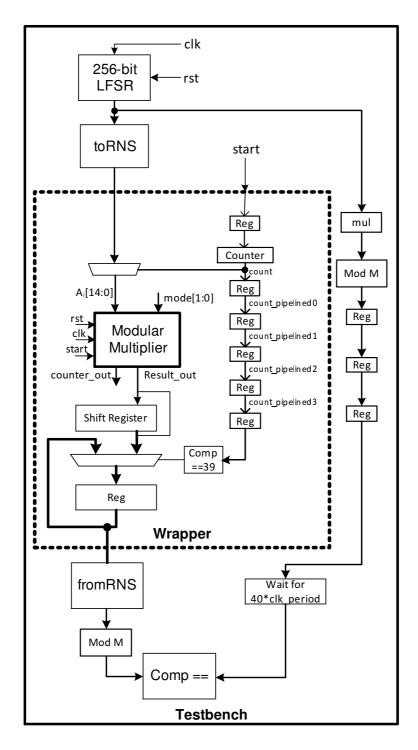

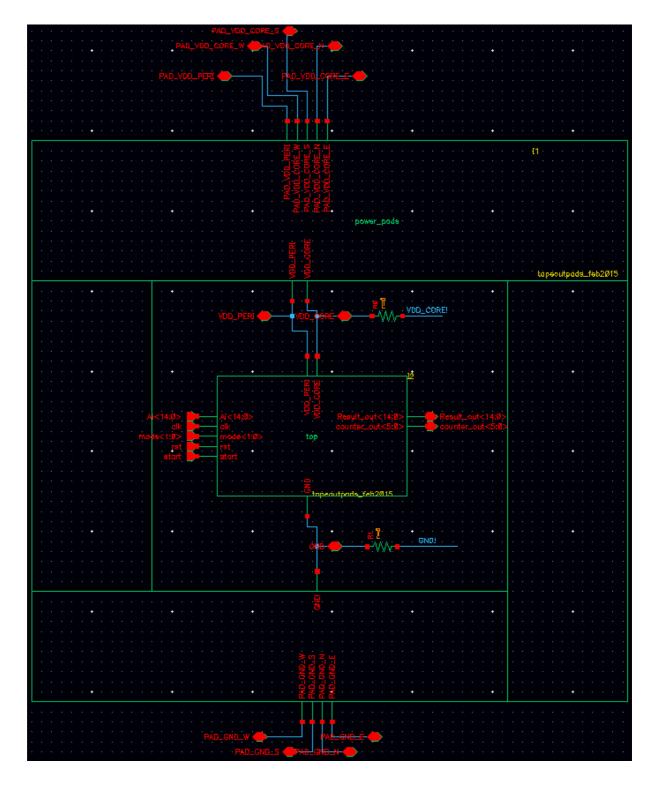

| 5.3  | Test bench for post-layout simulation of modular multiplier                          |

| 5.4  | Simulation waveform of selected I/O buffer for modular multiplier chip $$ . $$ . 126 |

| 5.5  | Schematic of the top cell of modular multiplier chip from Virtuoso 132               |

| 5.6  | Symbol of top cell of modular multiplier chip from Virtuoso                          |

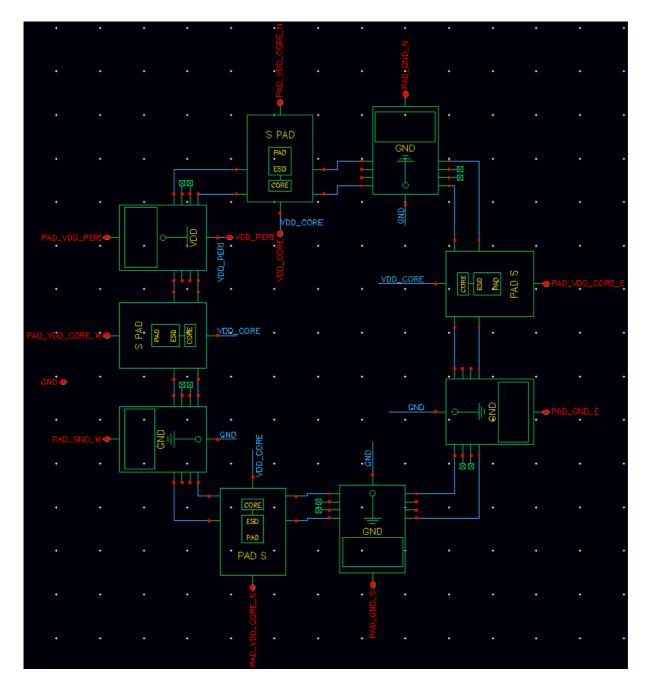

| 5.7  | Schematic of power supply pads for modular multiplier chip                           |

| 5.8  | Modified symbol of top cell of modular multiplier chip                               |

| 5.9  | Final schematic of top cell of modular multiplier chip                               |

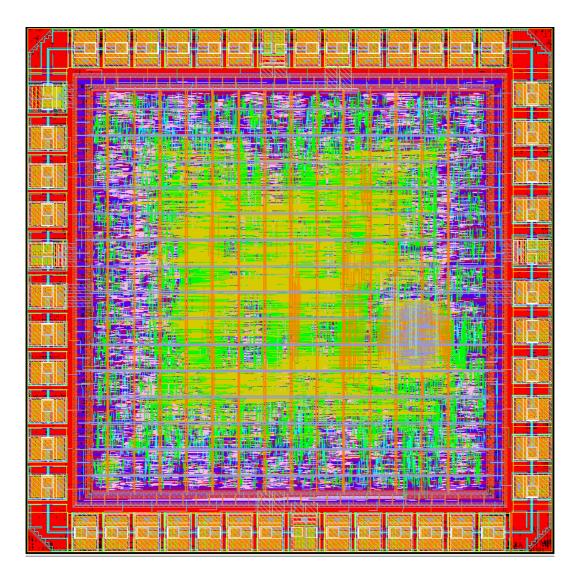

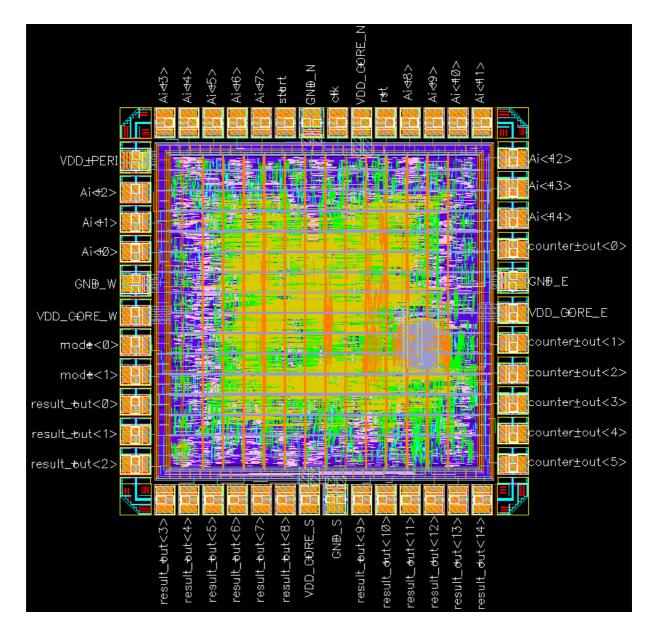

| 5.10 | Screenshot of the modular multiplier chip layout after tiling                        |

| 5.11 | Screenshot of the modular multiplier chip layout with I/O labels 139 $$              |

| 5.12 | Microphotograph of the fabricated chip of modular multiplier                         |

| 5.13 | Measurement setup for fabricated chip of modular multiplier                          |

| 5.14 | Observation of measurement results of modular multiplier chip in Logic               |

|      | Analyzer                                                                             |

| 5.15 | Frequency, energy, and power consumption of modular multiplier chip at               |

|      | different voltage levels                                                             |

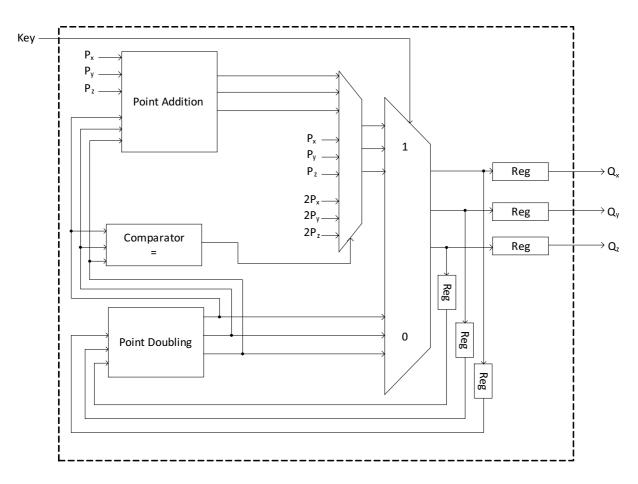

| 6.1  | General block diagram of elliptic curve point multiplication in Jacobian |

|------|--------------------------------------------------------------------------|

|      | coordinates                                                              |

| 6.2  | Serial architecture of modular reduction                                 |

| 6.3  | Serial-parallel architecture of modular reduction                        |

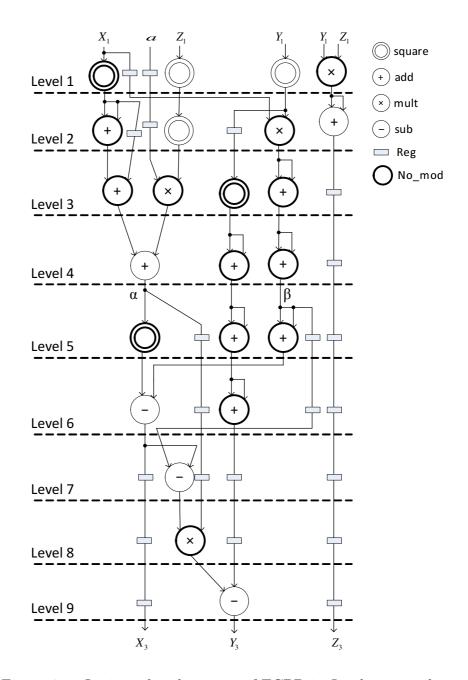

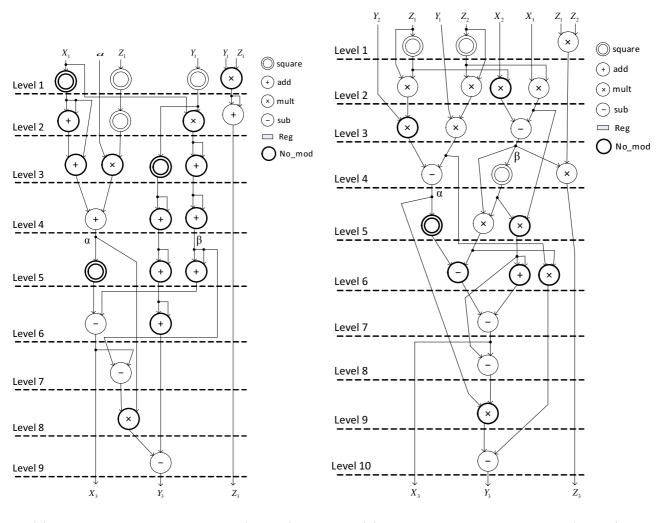

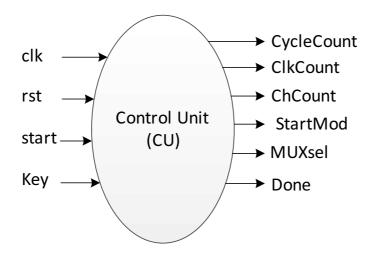

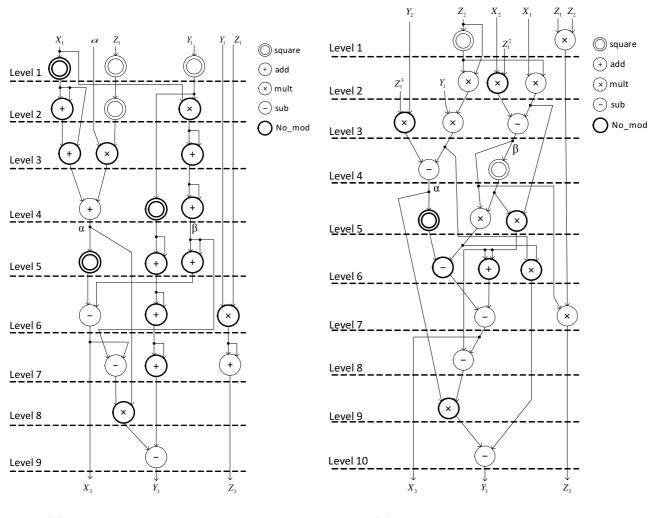

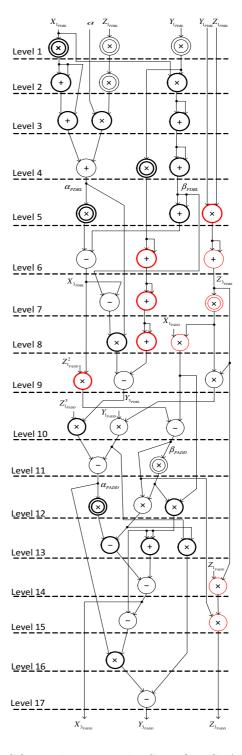

| 6.4  | Architecture of ECPD in Jacobian coordinates                             |

| 6.5  | Optimised architecture of ECPD in Jacobian coordinates                   |

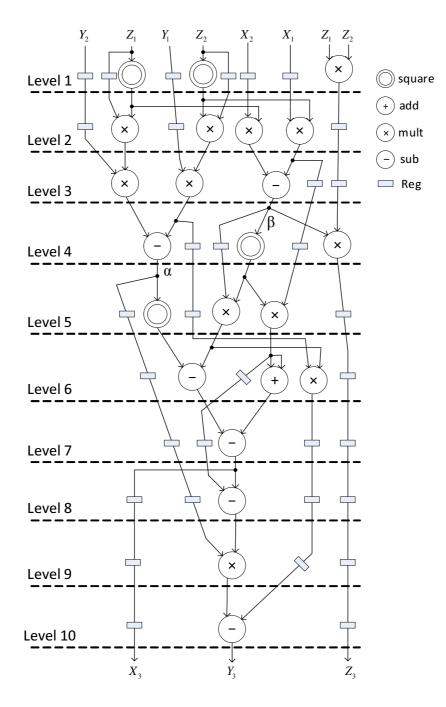

| 6.6  | Architecture of ECPA in Jacobian coordinates                             |

| 6.7  | Optimised architecture of ECPA in Jacobian coordinates                   |

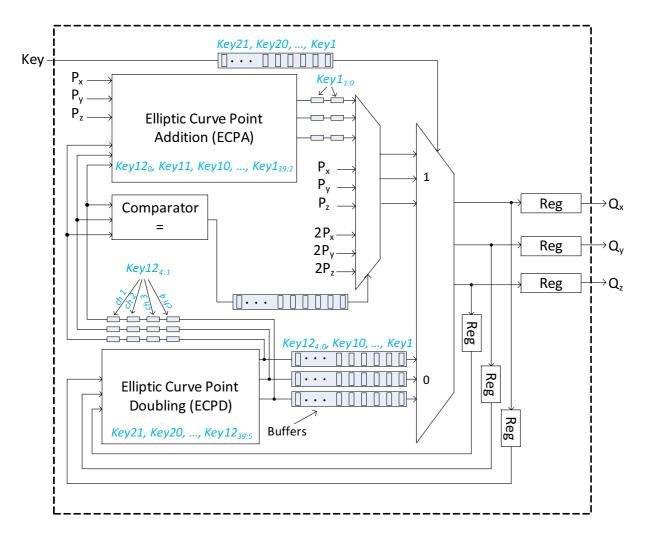

| 6.8  | Multi-Key architecture of ECPM in Jacobian coordinates                   |

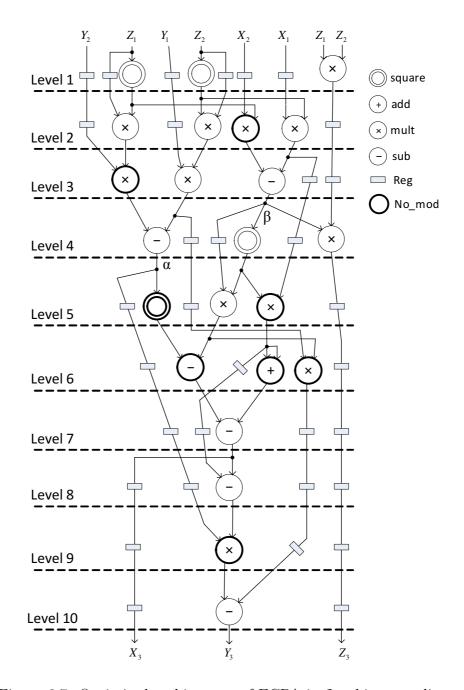

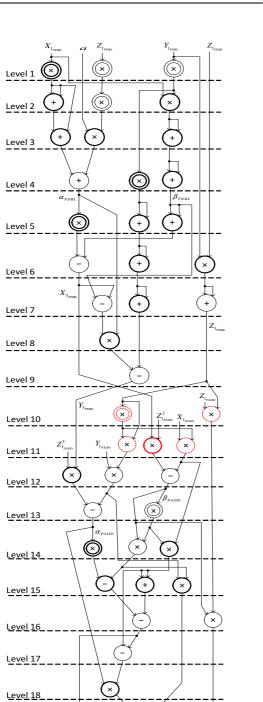

| 6.9  | Optimised architectures of ECPD and ECPA                                 |

| 6.10 | Single-key ECPM architecture in Jacobian coordinates                     |

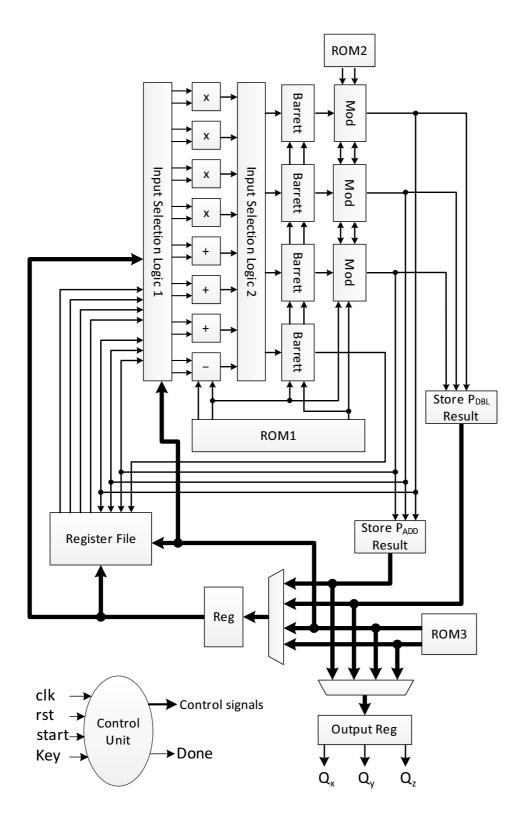

| 6.11 | Control unit for single-key ECPM                                         |

| 6.12 | Optimised and reordered architectures of ECPD and ECPA 190               |

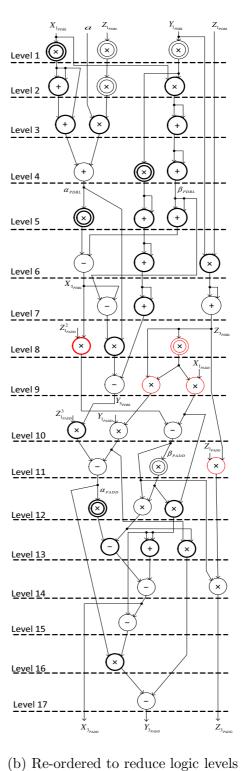

| 6.13 | Combined and re-ordered ECPD and ECPA architectures                      |

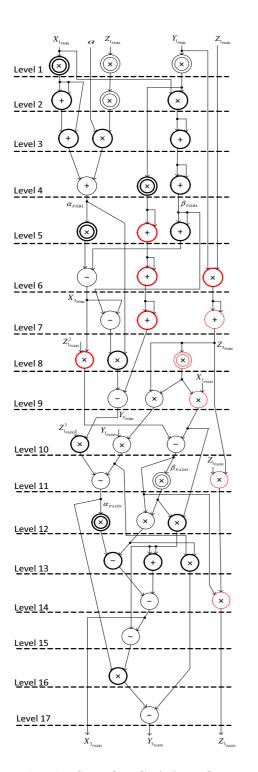

| 6.14 | Final optimisation of combined ECPD and ECPA architectures 194           |

| 6.15 | Optimised single-key ECPM architecture in Jacobian coordinates 197       |

# List of Tables

| 2.1 | Existing modular multipliers in binary number system                              | 15  |

|-----|-----------------------------------------------------------------------------------|-----|

| 2.2 | Existing modular multipliers in residue number system                             | 17  |

| 2.3 | NIST-recommended domain parameters over $\mathbb{F}_{256}$ on Koblitz Curve $[2]$ | 23  |

| 2.4 | Existing ECPM architectures in binary number system over $\mathbb{F}_{256}$       | 25  |

| 2.5 | Existing RNS-based ECPM designs over $\mathbb{F}_{256}$                           | 27  |

| 3.1 | Comparison of reduction stages for traditional and counter-based Wallace          |     |

|     | multipliers                                                                       | 39  |

| 3.2 | Total wires in top module of the proposed CBW multipliers $\ldots \ldots \ldots$  | 56  |

| 3.3 | Radix-4 Booth Encoding Values                                                     | 58  |

| 3.4 | Total Reduction Stages for Wallace and Counter-Based Wallace Multipliers          | 62  |

| 3.5 | Synthesis parameters for Synopsys DC                                              | 64  |

| 3.6 | Synthesis results of proposed and reference multiplier implementations $\ . \ .$  | 69  |

| 4.1 | Maximum possible N against $w$ in new RNS modular multiplication                  | 92  |

| 4.2 | Proposed RNS moduli set for a dynamic range of 560 bits                           | 94  |

| 4.3 | Pre-computed parameters for Algorithm 5 and Algorithm 6                           | 95  |

| 4.4 | Complexity analysis of the proposed architecture                                  | 98  |

| 4.5 | Number of $w$ -bit modular multiplications in the considered RNS MM Al-           |     |

|     | gorithms                                                                          | 100 |

| 4.6 | Synopsys Design Compiler parameters used for the synthesis of modular   |

|-----|-------------------------------------------------------------------------|

|     | multiplier architectures                                                |

| 4.7 | Synthesis results of proposed modular multiplier implementations on 90  |

|     | nm CMOS                                                                 |

| 4.8 | Post-place&route results of proposed modular multiplier implementations |

|     | on Virtex-6 and Virtex-7 FPGA                                           |

| ۲ 1 |                                                                         |

| 5.1 | Different operating modes of the modular multiplier chip                |

| 5.2 | Chip measurement results of the proposed modular multiplier             |

| 5.3 | Comparison of proposed modular multiplier with state-of-the-art modular |

|     | multiplication architectures                                            |

| 6.1 | Post-place&route results of proposed ECPM implementations on Virtex-6   |

|     | and Virtex-7 FPGA                                                       |

| 6.2 | Synthesis results of proposed ECPM implementations on 90 nm CMOS $$ 203 |

| E.1 | Virtex-6 and Virtex-7 FPGA Details used in this research [3,4]          |

\_\_\_\_\_

### List of Publications

Publications where the author appeared as first author.

- S. Asif, S. Hossain, Y. Kong, "High-throughput multi-key elliptic curve cryptosystem based on residue number system", *IET Computers and Digital Techniques* (submitted).

- S. Asif, Y. Kong, "Highly parallel modular multiplier for elliptic curve cryptography in residue number system", *Circuits, Systems, and Signal Processing*, pp. 1–25, 2016.

- S. Asif, Y. Kong, "Analysis of different architectures of counter based Wallace multipliers", *International Conference on Computer Engineering and Systems (ICCES)*, pp. 139-144, 23-24 December 2015, Cairo, Egypt.

- S. Asif, Y. Kong, "Design of an algorithmic Wallace multiplier using high speed counters", *International Conference on Computer Engineering and Systems (IC-CES)*, pp. 133-138, 23-24 December 2015, Cairo, Egypt.

- S. Asif, Y. Kong, "Performance analysis of Wallace and radix-4 Booth-Wallace multipliers", *Electronic System Level Synthesis Conference (ESLsyn)*, pp.17-22, 10-11 June, 2015, San Francisco, USA.

S. Asif and Y. Kong, "Low-area Wallace multiplier", VLSI Design, vol. 2014, Article ID 343960, 6 pages, 2014.

Publications where the author is not the first author in the paper.

• Y. Kong, S. Asif, M. A. U. Khan, "Modular multiplication using the core function in the residue number system", *Applicable Algebra in Engineering, Communication and Computing*, pp. 1-16, vol. 27, no. 1, 2015.

### Chapter 1

### Introduction

Since the advent of computers and the Internet, the security of confidential information has been a huge concern. The information is most vulnerable during transmission over the Internet, during which anyone with adequate expertise can steal this information. In order to ensure secure data transmission two major techniques are used, steganography and cryptography. Both of these techniques have been in use (with different names) since long before the invention of computers, but the following text discusses these in the context of computing applications.

In steganography, the secret message is concealed within another message, where the messages can be in the form of text file, image, or video. The message which is used to hide the secret message is selected in such a way that it does not attract any attention, to avoid scrutiny. Messages protected in this way rely on the assumption that no one tries to check for any hidden messages, and therefore this technique is not suitable for transmissions where all messages are scrutinised.

In cryptography, the secret message is encrypted in such a way that retrieval of the original message is almost impossible. Cryptography does not try to hide the fact that a secret message is transmitted, instead it relies on the strength of an encryption algorithm to ensure that the message cannot be decrypted without the necessary information. Hence this method is more suitable for highly sensitive data transmission.

Cryptography is divided into two major categories: 1) Symmetric-key cryptography, 2) Public-key cryptography. In symmetric-key cryptography, the same key is used for encryption and decryption of a message, whereas public-key cryptography uses a set of interrelated keys called private key and public key. In public-key cryptography, the public key is used to encrypt the message whereas decryption is performed by the private key. A public key is available publicly and anyone can use it to encrypt a message intended for the person who has the private key corresponding to that specific public key. A private key – which must remain secret – is used to decrypt the message. A classical example of public-key cryptography is shown in Fig. 1.1.

Figure 1.1: Classical example of public-key cryptography

Elliptic curve cryptography (ECC) is one of the most widely used public-key cryptosystems due to its high level of security while still using a smaller key than the other

public-key cryptosystems. The standard curves and key size of ECC systems has been standardised by IEEE [5], ANSI [6], and NIST [7]. Various methods are developed to improve the speed of existing ECC algorithms. Among the proposed methods, the use of residue number systems (RNS) in the construction of ECC architectures has gained popularity due to the high-speed nature of arithmetic operations in RNS. In an RNS, a large number is represented as a set of small independent numbers, and arithmetic operations are performed concurrently on all the numbers, resulting in fast processing of results.

This thesis makes a contribution to the existing literature by proposing a number of hardware architectures to perform high-speed low-power ECC based on an RNS. The implementation results of the proposed architectures are analysed in detail along with the suitability of the architectures for different applications.

#### **1.1** Motivation for this Research

The need for high-throughput cryptosystems is undeniable as they are required in a number of applications where thousands of encryptions are performed per second, e.g. banking and email servers. These systems make little effort to reduce the power consumption due to the availability of an unlimited power supply. On the other hand, power consumption is a major issue in portable applications which operate on the limited capacity of batteries e.g. personal digital assistants (PDAs), mobile phones, tablets, laptops, etc. Cryptography is used in these applications for secure transmission of sensitive data, e.g. online banking, emails, online shopping, etc.

Since its invention in 1985, ECC has become increasingly popular in many computing applications due to its high efficiency. Nowadays, ECC has replaced the other publickey cryptosystems in many applications including smart cards, ATMs, EFTPOS, online banking, mobile phones, email servers, banking servers, etc., so the development of highspeed low-power ECC architectures is of great importance.

Most of the existing research is focused on reducing the delay of the ECC algorithms, with little focus on power consumption. In digital systems, a decrease in delay usually results in an increased power consumption due to the techniques used for delay reduction. Therefore, a suitable metric for analysis of the overall performance of digital systems is a product of delay and power (PDP) which represents the energy dissipation to perform a given operation. In this research, several hardware architectures are proposed for highspeed ECC with optimised power consumption.

#### 1.2 Objectives of this Research

The most frequent and time-consuming operation in ECC is elliptic curve point multiplication (ECPM) and therefore the existing research aims to reduce the delay of this operation. The objective of this thesis is to improve the efficiency of ECPM in terms of speed and power consumption. Firstly, a number of architectures are developed for highspeed modular multiplication by using an RNS. These modular multipliers are then used in the construction of ECPM architectures. Detailed analysis is performed to optimise the proposed architectures in terms of delay, area, and power consumption.

#### **1.3** Thesis Outline

This thesis is organised as follows:

• Chapter 2: Background

This chapter provides the necessary background required to understand the development of the proposed algorithms and architectures. The theory of residue number systems (RNS) and some mathematical operations are briefly discussed along with the benefits and drawbacks of an RNS. A brief literature review is given for binary and RNS-based modular multipliers as well as important results from the existing literature. The theory of elliptic curves and their use in elliptic curve cryptography (ECC) is explained, and the mathematical theory of elliptic curve operations in elliptic curve point multiplication (ECPM) is discussed. The use of different coordinate systems in ECC is discussed and the ECC standard used in the proposed architectures is provided. Finally, an overview of the existing ECPM architectures in binary and RNS is provided.

• Chapter 3: Counter-Based Wallace Multipliers

This chapter discusses the importance of Wallace multipliers for high-speed applications. The specific focus is on counter-based Wallace (CBW) multipliers and incorporation of Booth encoding to speed up the multiplication. Different architectures for CBW multipliers are proposed and a detailed analysis is performed to analyse the benefits and drawbacks of different architectures. Furthermore, a generic algorithm is developed to construct high-speed CBW multipliers of any size. The performance of CBW and Booth-encoded CBW multipliers are compared to show that the use of Booth encoding degrades the performance of Wallace multipliers.

• Chapter 4: Modular Multipliers Using Sum of Residues in RNS

This chapter discusses the development of a modular multiplication (MM) algorithm based on a sum of residues. The existing MM algorithm is improved and three variants of the algorithm are proposed. Criteria for the selection of an RNS moduli set are established and a 40-channel RNS moduli set is proposed for 256-bit modular multiplication. Three hardware architectures – parallel, serial, and serial-parallel – are proposed and their implementation on FPGA and ASIC platforms is discussed. Finally, synthesis results of proposed architectures are analysed for timing, area, and power consumption.

• Chapter 5: Chip Fabrication for RNS-based Modular Multiplier

In this chapter, the chip fabrication is presented for the RNS-based serial MM architecture which was proposed in Chapter 4. The serial MM architecture of Chapter 4 is modified and test circuitry is added to enable on-chip verification of the fabricated ASIC. A brief description of the chip tapeout procedure is provided along with information on the EDA (electronic design automation) tools used in the process. Finally, the measurement of the fabricated ASIC is explained and measurement results are discussed in detail.

• Chapter 6: Elliptic Curve Point Multiplication

This chapter presents the proposed architectures for elliptic curve point multiplication (ECPM). The MM architectures of Chapter 4 are modified to construct modular reduction architectures (modulus operation) which are then used in the implementation of elliptic curve point doubling (ECPD) and elliptic curve point addition (ECPA). We propose a new multi-key ECPM architecture which uses deep pipelining to process 21 keys simultaneously. To the best of our knowledge this is the first implementation of a multi-key ECPM architecture. Furthermore, a singlekey ECPM architecture is proposed which optimises the hardware cost by resource sharing. The proposed architectures are implemented on FPGA and ASIC platforms and results for timing, area, and power consumption are discussed in detail to highlight the benefits of the proposed architectures.

• Chapter 7: Thesis Conclusion and Future Work

This chapter concludes the thesis and discuss the possibilities for further enhancement of this work.

### Chapter 2

### Background

#### 2.1 Introduction

With the swift growth of secure transactions over the network and associated appliances, the demand for data security has increased rapidly in recent days. For these applications, public-key cryptography (PKC) such as elliptic curve cryptography (ECC) [8] and Rivest-Shamir-Adleman (RSA) [9] plays a vital role to pass the secured information among different devices.

The RSA cryptography was first invented in 1977 and is based on the factoring problem. In a valid RSA public key, the RSA modulus M is a product of two distinct odd prime numbers p and q. The major operation in the RSA encryption algorithm is the modular exponentiation that dominates the overall complexity of the RSA system. The modular exponentiation in the RSA is performed by repeated modular multiplications therefore a large number of architectures are proposed for the efficient modular multiplication architectures suitable for RSA [10–13]. The large key size of the RSA makes it less suitable for hardware implementations specially where the area is of major concern. The better choice for area-constrained applications is the ECC. The ECC was first proposed by N. Koblitz and V. Miller in the mid 80s. It is progressively becoming a more attractive alternative in the past few years to traditional RSA cryptosystems, because ECC can provide the same level of security as the traditional RSA cryptosystem with significantly smaller keys and area. Besides, less memory and hardware resources are required to implement ECC [14–16]. High-performance finite-field modular arithmetic (FFMA), for example modular addition, subtraction, and multiplication algorithms with hardware architectures over a prime field, are mandatory for an efficient ECC processor (ECP). In addition, smaller FFMA operations are required in data communication systems to encrypt data by using ECCs, enabling potentially higher data rates at a much lower implementation cost. These attractive features make ECC very popular for resource-constrained environments such as smart cards, credit cards, pagers, personal digital assistants (PDAs), and cellular phones.

ECC relies on complex mathematical problems to ensure that the data cannot be decrypted by intruders. Various architectures have been developed for hardware implementation of ECC. In recent years, a number of research papers implemented ECC using the residue number system (RNS), which is famous for high-speed arithmetic for addition, subtraction, and multiplication. Since the most frequent operation in ECC is modular multiplication, implementation of RNS-based modular multipliers is essential to implement ECC based on an RNS. This chapter provides the mathematical background of RNS and ECC as well as a brief literature review of modular multipliers and ECC architectures.

#### 2.2 Residue Number System

The use of residue number systems (RNS) in public-key cryptography has become increasingly popular over the past few years due to their ability to perform high-speed arithmetic operations on large numbers. In RNS, a large integer is represented by a set of smaller residue integers. The concept of representing a number by the multiple-residue representation was first introduced by the Chinese mathematician Sun Tsu more than 1500 years ago [17].

The RNS is a non-positional number system and is defined by a set of N co-prime positive integers, called a moduli set:

$$m = \{m_0, m_1, \dots, m_{N-1}\}.$$

(2.1)

The size (number of bits) of each modulus  $m_i$  is also called the channel width of the RNS. Within the RNS there is a unique representation of all integers in the range [0, D - 1]where D is the range of the RNS, known as the dynamic range, and can be computed by Equation (2.2) [18].

$$D = \prod_{i=0}^{n-1} m_i \tag{2.2}$$

A positive integer A in the RNS can be expressed as:  $A = \{a_0, a_1, \dots, a_{N-1}\}$  where

$$a_i = (A \mod m_i). \tag{2.3}$$

Two other values that are commonly used in RNS computations are  $D_i$  and  $\langle D_i^{-1} \rangle_{m_i}$ .  $D_i = D/m_i$ , and  $\langle D_i^{-1} \rangle_{m_i}$  is its multiplicative inverse such that  $\langle D_i \times D_i^{-1} \rangle_{m_i} = 1$ .

### 2.2.1 Arithmetic Operations in the RNS

Arithmetic operations in the RNS can be classified into two main categories:

- The simple operations, e.g. addition, subtraction, and multiplication.

- The complex operations, e.g. division, modulus, magnitude comparison, and sign detection.

Suppose that the RNS representations of A and B are given as  $A = \{a_0, a_1, \ldots, a_{N-1}\}$ and  $B = \{b_0, b_1, \ldots, b_{N-1}\}$ , respectively. The simple arithmetic operations on A and B can be performed by processing all channels concurrently:

$$C = \{ \langle a_0 \cdot b_0 \rangle_{m_0}, \langle a_1 \cdot b_1 \rangle_{m_1}, \dots, \langle a_{N-1} \cdot b_{N-1} \rangle_{m_{N-1}} \}$$

(2.4)

where  $(\cdot)$  represents addition, subtraction, or multiplication.

The primary advantage of an RNS is the ability to perform parallel operations on all channels to perform fast addition, subtraction, or multiplication for large numbers. Since there is no carry propagation between channels the use of an RNS significantly decreases the delay of simple arithmetic operations for large numbers [17, 19].

The second category of arithmetic operations, mentioned as complex operations, includes division, modulus, magnitude comparison, and sign detection. Equation (2.4) does not hold for the complex operations, therefore special algorithms are required to perform these operations in RNS. Little research has been done on RNS-based division [20, 21], magnitude comparison [22], and sign detection [23–25]. Since these operations are not required for elliptic curve cryptosystems, a detailed review of these operations is not carried out.

The most frequent operation in elliptic curve cryptosystems is the modulus operation, more commonly known as modular reduction in the existing literature. Modular reduction is discussed briefly in Section 2.2.5. RNS-based modular reduction is widely studied in the context of modular multiplication for ECC and RSA cryptosystems. A detailed discussion of modular multiplication is presented in Section 2.3.

### 2.2.2 The Chinese Remainder Theorem

The Chinese remainder theorem (CRT) is the most important part of the residue number system. It assures us of the unique representation of each number within the dynamic range of an RNS [17,26]. The CRT is also very useful in the reverse conversion (RNS to binary) as well as other useful operations. The CRT is defined by

$$X = \left\langle \sum_{i=0}^{N-1} D_i \langle D_i^{-1} x_i \rangle_{m_i} \right\rangle_D \tag{2.5}$$

where D is the dynamic range of the RNS defined by the moduli set  $m = \{m_0, m_1, \ldots, m_{N-1}\}$ and  $x_i$  is the  $i^{th}$  value of X in the RNS.  $D_i = D/m_i$ , and  $D_i^{-1}$  is the modular inverse of  $D_i$  such that  $\langle D_i \times D_i^{-1} \rangle_{m-i} = 1$ .

### 2.2.3 RNS Moduli Set Selection

The selection of an efficient RNS moduli set is very important for the performance of the complete system [26]. An RNS moduli set is usually represented as  $\{m_0, m_1, \ldots, m_{N-1}\}$ , where each modulus  $m_i$  is co-prime to all other moduli:

$$GCD(m_i, m_j) = 1 \quad \text{where } (i \neq j)$$

$$(2.6)$$

The selection of an appropriate moduli set is a case-specific problem and varies for different applications [27]. The most widely investigated RNS moduli set consists of three moduli  $\{2^n - 1, 2^n, 2^n + 1\}$ . Most of the existing literature focuses on RNS moduli sets in special formats [28–37]:

- $(2^n 1, 2^n, 2^n + 1)$

- $(2^n 3, 2^n 1, 2^n, 2^n + 1, 2^n + 3)$

- $(2^n 1, 2^n, 2^{n-1} 1, 2^{n-1} + 1)$

- $(2^n 1, 2^n, 2^n + 1, 2^{n+1} 1)$

- $(2^n, 2^n 1, 2^n + 1, 2^{n-1} 1)$

- $(2^n 1, 2^n, 2^n + 1, 2^{n+1} + 1)$

- $\{2^{n+1}, 2^n 1, 2^n + 1, 2^n + 2^{(n+1)/2} + 1, 2^n 2^{(n+1)/2} + 1\}$

- $\{r^a, r^b 1, r^c + 1\}$

The moduli in the form of  $2^n$ ,  $2^n - 1$ , etc. enable fast computation of modulus operations using simple algorithms. The disadvantage of these special moduli sets is their limited dynamic range for small values of n. For example, to achieve a dynamic range of 64 bits n needs to be at least 22 for the RNS moduli set  $\{2^n - 1, 2^n, 2^n + 1\}$ .

It is possible to achieve a higher dynamic range by using small channel widths (size of each modulus) and increasing the number of channels (number of moduli). This kind of RNS moduli set is used in [38–40]; it increases the speed of addition, subtraction, and multiplication within each channel due to the small channel width. Since the moduli are not a power of 2, the algorithm for modulus operations may become more complex.

### 2.2.4 Scaling in the RNS

The term "scaling" in an RNS is used for a division of a number by a constant value. Scaling is usually represented as

$$Y = \left\lfloor \frac{X}{k} \right\rfloor.$$

(2.7)

Scaling of a number is a frequent operation in applications related to Digital Signal Processing (DSP) [41,42]. A wide range of scaling algorithms are proposed in the existing literature to suit different applications [43–49]. Fortunately, cryptographic algorithms do not require scaling, therefore we did not investigate scaling algorithms in detail.

### 2.2.5 Modular Reduction in RNS

Modular reduction (or the mod operation) in RNS is a computationally complex operation because Equation (2.4) does not hold true for this operation. For example, if A and B are two integers and their RNS representations are  $\{a_0, a_i, \ldots, a_{N-1}\}$  and  $\{b_0, b_i, \ldots, b_{N-1}\}$ , respectively, for an RNS defined by moduli set  $\{m_0, m_i, \ldots, m_{N-1}\}$ , then the modular reduction performed in individual RNS channels does not give the same result as a modular reduction of integers A and B:

$$A \mod B \neq \{ \langle a_0 \mod b_0 \rangle_{m_0}, \langle a_1 \mod b_1 \rangle_{m_1}, \dots, \langle a_{N-1} \mod b_{N-1} \rangle_{m_{N-1}} \}.$$

(2.8)

Hence, several algorithms have been proposed in the literature to perform modular reduction in an RNS. Modular reduction is most commonly studied in the context of modular multiplication, which is a fundamental operation in public-key cryptosystems. A brief overview of modular multipliers follows, and Chapter 4 presents the proposed RNS-based modular multiplication architecture.

## 2.3 Modular Multipliers

Modular multiplication  $Z = (A \times B) \mod M$  is the most frequently used operation in ECC, therefore the development of high-speed modular multipliers is imperative to speed up ECC. This section briefly discusses the existing modular multiplier architectures in binary and RNS.

# 2.3.1 Overview of Existing Modular Multiplication Architectures in Binary Number System

A comprehensive literature review of binary modular multipliers is out of the scope of this work, therefore only a brief overview of the key algorithms of modular multiplication is provided. Existing research on modular multipliers in a binary number system provides a wide range of algorithms and implementation strategies [10,50–64]. Most of the techniques for modular multiplication are based on Montgomery modular multiplication, proposed

by P. L. Montgomery in 1985 [65]. Montgomery modular multiplication, commonly called Montgomery multiplication, performs a complete modular multiplication in n iterations, where n is the word length of the operands. Each iteration consists of two addition and shift operations. Improvements to Montgomery multiplication are proposed in [66–73]. An analysis of different Montgomery multipliers is presented in [52].

Another widely used method for modular multiplication is the Barrett algorithm [74], which was proposed by Paul Barrett in 1987. The Barrett algorithm uses pre-computations to avoid the division algorithm and requires only two multiplications and one subtraction along with shift operations. A detailed investigation of Barrett and Montgomery multipliers is done by J. F. Dhem [75, 76]. A fast interleaved modular multiplier based on Barrett and Montgomery techniques is proposed in [58].