# AN RF FRONT-END SYSTEM COMPARISON OF SiGe HBT AND GaAs pHEMT : LIMITATIONS IN NON-LINEARITY AND BALANCE

By

Sudipta Chakraborty

A thesis submitted to Macquarie University for the degree of Doctor of Philosophy Department of Engineering June 2017

© Sudipta Chakraborty, 2017.

Typeset in  $\mathbb{A}T_{\mathbb{E}} X 2_{\mathcal{E}}$ .

## Statement of Originality

Except where acknowledged in the customary manner, the material presented in this thesis is, to the best of my knowledge, original and has not been submitted in whole or part for a degree in any university.

Sudipta Chakraborty 25. 7. 2017

To my parents

## Acknowledgements

We all know that "time flies", and gradually the clock is ticking towards the end of the three years of my PhD tenure. The time has come to thank all the people who have helped me to reach this point.

First of all, I would like to thank my principal supervisor Professor Michael Heimlich for giving me the opportunity to pursue PhD studies at Macquarie University under his supervision. He has been very supportive of my research work throughout my PhD candidature, provided great advice and has highly motivated me. I am also grateful to him in that working with Mike has given me the opportunity to work with some fantastic people from industry.

I would also like to thank my associate supervisor Professor Anthony E. Parker for his motivation and guidance. Thanks to Macquarie University for awarding me the International Postgraduate Research Scholarship (IPRS) to pursue my PhD.

I am indebted to Mr Leigh E. Milner from DSTG, Adelaide, for his support throughout my PhD candidature. He is a man with great dedication and patience. None of the tape-outs would have been possible without his help and guidance. He taught me SiGe layout by telephonic conversation, which is incredible. When it comes to him, I have no words to express my gratitude, all I can say is he can turn desire into reality.

I was fortunate to get support from Mr Gerry McCulloch at MACOM Technology Solutions, North Sydney with his excellent guidance with measurements. I am grateful to him for giving me his valuable time for measurements whenever I requested. I would also like to thank Melissa Rodriguez for her tremendous support and guidance with the GaAs designs, which needed to be taped out in a very short span of time. I am also thankful to Dr Jim Harvey for reviewing some of my designs and Dr Simon Mahon for providing me access to the resources at MACOM Technology Solutions, North Sydney.

I am grateful to Dr Oya Sevimli for introducing me to the world of measurement, teaching me from scratch. She has been very supportive of me always, provided good advice and shared her knowledge during our frequent informal meetings. I would like to thank Dr Xi Zhu for his help during the initial days of my PhD. Many thanks to Dr Keith Imrie for detailed reading of this thesis and a few of my papers. Thanks to all the staff and my fellow members of the Department, particularly my group mates, Dr Evgeny Kuxa, Dr Perzila Ara, Dr Bryan Schwitter who have helped me directly or indirectly.

I am thankful to Mr Anirban Neogi, the then HOD of the E.C.E. department at the Bengal Institute of Technology, who inspired me to pursue the M.Tech in the first place instead of taking up one of the multiple jobs from different leading IT companies. I would also like to thank Dr Hafizur Rahman, HOD of the VLSI department, IIEST (BESU) for providing me with a reference for my PhD application and encouraging me to pursue the PhD.

I am greatly indebted to my dear friend Dr Budhaditya Majumdar for advising and motivating me to apply for PhD studies overseas. He has always helped me with any problems and provided advice on technical content. He has always encouraged me at difficult times of my PhD candidature.

Thanks to all of my friends and family who have supported me up to this point. I don't have enough words to express my gratitude to my family, especially my uncle (Mr Amitava Bhattacharya) and aunt (Mrs Madhabi Bhattacharya). Thanks to my brothers Mr Sujal Chakraborty and Mr Supriyo Chakraborty, sister-in-law Mrs Swarajita Chakraborty, for their love, continuous support and encouragement. Finally, to my mother (Mrs Mahua Chakraborty) and father (Mr Shyamal B. Chakraborty), I am forever indebted for your love and support, without which I would not have been here. Thanks for helping me to pursue my goals and putting up with my absence for three years. I dedicate this thesis to them.

## List of Publications

#### Articles

S. Chakraborty, L. E. Milner, X. Zhu, L. T. Hall, O. Sevimli and M. C. Heimlich *A K-band Frequency Doubler with 35-dB Fundamental Rejection Based on Novel Transformer Balun in 0.13 μm SiGe Technology*. IEEE Electron Device Letters **37**, 1375-1378 (2016)

### Conferences

- <u>S. Chakraborty</u>, L. E. Milner, L. T. Hall, X. Zhu, O. Sevimli and M. C. Heimlich *Characterisation of a Transformer Balun for a 7-15 GHz SiGe Frequency Doubler*. (Australian Microwave Symposium (AMS 2016), Adelaide, Australia)

- <u>S. Chakraborty</u>, L. E. Milner, L. T. Hall, Anthony E. Parker and M. C. Heimlich *A 30-60 GHz SiGe Transformer Balun with Offset Radii Coils for Low Ampli- tude and Phase Imbalance*. (International Microwave Symposium, (IMS 2017), (accepted))

- S. Chakraborty, Xi Zhu, Oya Sevimli and Michael Heimlich A wideband Transformercoupled Frequency Quadrupler Using an Asymmetrical Balun in 0.25 μm SiGe for Backhaul Communication. (IEEE International Symposium on Circuits and Systems (ISCAS 2015), Lisbon, Portugal)

#### Others

- <u>S. Chakraborty</u>, B. Majumdar, M. Heimlich and K. P. Esselle A Simple Reconfigurable BiCMOS Active Inductor and Its Implementation in A Phase-Shifter Unit Cell. (2015 International Symposium on Antennas and Propagation (ISAP), Hobart, Tasmania, Australia)

- <u>S. Chakraborty</u>, B. Majumdar, M. Heimlich and K. P. Esselle SiGe HBT Based Impedance Switch for On-Chip Antenna Reconfigurability. (2015 Australian Symposium on Antennas, Sydney, New South Wales, Australia)

- B. Majumdar, D. Baer, <u>S. Chakraborty</u>, K. P. Esselle and M. Heimlich A 3D Printed Dual-Ridged Horn Antenna. (2016 International Conference on Electromagnetics in Advanced Applications (ICEAA / IEEE AWPC), Cairns, Queensland, Australia)

- B. Majumdar, D. Baer, <u>S. Chakraborty</u>, K. P. Esselle and M. Heimlich Additive Manufacturing of a Dual-Ridged Horn Antenna. Progress in Electromagnetics Research Letters 59, 109-114 (2016)

- B. Majumdar, D. Baer, <u>S. Chakraborty</u>, K. P. Esselle and M. Heimlich Advantages and limitations of 3D printing a dual-ridged horn antenna. Microwave and Optical Technology Letters 58, 2110-2117 (2016)

## Abstract

For a successful system design of a wireless transmitter or receiver, it is important to investigate the overall linearity of a particular manufacturing process, where the limit of linearity can be viewed both as the onset of non-linearity above some threshold as well as loss of phase and amplitude balance. This dissertation presents a balanced frequency-doubler circuit as an archetype of a non-linear circuit that would allow the study of harmonics. The source of non-idealities in a frequency doubler is studied that would limit the overall linearity of a system design. In this context, a balun is used as an archetype of the passive structures that complements a frequency doubler when the linearity of a system is considered. For microwave and millimetre-wave circuit design, GaAs processing is well established but it involves high cost. SiGe processing is emerging in the microwave and millimetre-wave arena, promising reasonable performance at a lower cost and equipped with integrated digital logic capability. To compare the two process technologies, GaAs and SiGe, similar frequency-doubler circuits and passive baluns are implemented in both the processes using GaAs pHEMTs and SiGe HBTs. The design challenges, issues with layout and design flows developed for each of the processes are discussed. Analysis of harmonics in frequency doublers using GaAs pHEMTs and SiGe HBTs shows that pHEMTs are inherently more linear than HBTs. Large input power is needed to drive the frequency doubler using pHEMTs compared to SiGe HBTs. However, the area requirement of the GaAs frequency doubler is more than the SiGe counterpart. Measurement results demonstrate that high linearity (> 35dB odd-harmonic suppression) and balance (< 0.15 dB amplitude imbalance and  $< 2^{\circ}$

phase imbalance) is possible from both technologies over comparable bandwidths.

## List of Abbreviations

- Aluminium Gallium Arsenide AlGaAs AMS Analogue and Mixed Signal AWR Applied Wave Research BEOL Back-end Offline BiCMOS Bipolar Complementary Metal Oxide Semiconductor  $BV_{CEO}$ Collector emitter breakdown voltage CMOS Complementary Metal Oxide Semiconductor dBDecibels Decibels referred to 1 milliwatt dBm DRC Design Rule Check  $\mathbf{E}\mathbf{M}$ Electro Magnetic ESD Electro-Static Discharge  $f_{max}$ Maximum frequency of oscillation  $f_T$ Transit frequency

- GaAs Gallium Arsenide

| HBT            | Heterojunction Bipolar Transistor                   |

|----------------|-----------------------------------------------------|

| HV–HBT         | High Voltage Heterojunction Bipolar Transistor      |

| HS-HBT         | High Speed Heterojunction Bipolar Transistor        |

| ITRS           | International Technology Roadmap for Semiconductors |

| LO             | Local Oscillator                                    |

| LVS            | Layout Versus Schematic                             |

| MBE            | Molecular Beam Epitaxy                              |

| MIM            | Metal Insulator Metal                               |

| MMIC           | Monolithic Microwave Integrated Circuit             |

| MWO            | Microwave Office                                    |

| P-cells        | Parameterised cells                                 |

| PDK            | Process Design Kit                                  |

| pHEMT          | Pseudomorphic High Electron Mobility Transistor     |

| PLL            | Phase Locked Loop                                   |

| $\mathbf{RF}$  | Radio Frequency                                     |

| SiGe           | Silicon Germanium                                   |

| SiN            | Silicon Nitride                                     |

| SOLT           | Short Open Load Through                             |

| SPP            | Shape Pre-Processing rules                          |

| $\mathbf{TFR}$ | Thin-film Resistor                                  |

| TM1            | Thick Metal 1                                       |

#### TM2 Thick Metal 2

- **UGW** Unit Gate Width

- VCO Voltage Controlled Oscillator

- **VLSI** Very-Large-Scale Integration

# Contents

| A            | ckno  | wledge | oments vii                                                    | Ĺ |

|--------------|-------|--------|---------------------------------------------------------------|---|

| Li           | st of | Publi  | cations ix                                                    | - |

| $\mathbf{A}$ | bstra | ict    | xi                                                            | i |

| Li           | st of | Abbre  | eviations xiii                                                | i |

| Li           | st of | Figur  | es xxiii                                                      | i |

| Li           | st of | Table  | s xxxiii                                                      | i |

| 1            | Intr  | oduct  | ion 1                                                         |   |

|              | 1.1   | Status | s of semiconductor market                                     | ) |

|              | 1.2   | GaAs   | and silicon technologies                                      | 2 |

|              |       | 1.2.1  | Overview                                                      | ) |

|              |       | 1.2.2  | Development of heterostructures                               | , |

|              |       | 1.2.3  | Transit frequency and maximum frequency of oscillation 8      | ; |

|              |       | 1.2.4  | Performance trend                                             | ) |

|              | 1.3   | Aims   |                                                               | 6 |

|              |       | 1.3.1  | Motivation for the performance comparison                     | , |

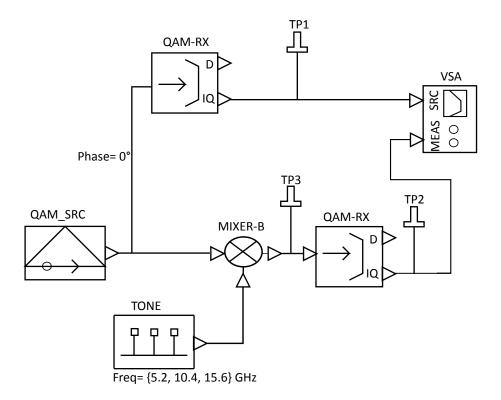

|              |       | 1.3.2  | QAM System                                                    | • |

|              |       | 1.3.3  | Frequency multiplier as an archetype of non-linear circuit 20 | ) |

|          |     | 1.3.4    | Frequency bands of interest                | 20 |

|----------|-----|----------|--------------------------------------------|----|

|          |     | 1.3.5    | Objectives                                 | 21 |

|          | 1.4 | Scope    |                                            | 23 |

|          | 1.5 | Synops   | sis                                        | 24 |

| <b>2</b> | Bac | kgrour   | nd                                         | 29 |

|          | 2.1 | Introd   | uction                                     | 29 |

|          | 2.2 | SG13S    | SiGe HBT process                           | 30 |

|          | 2.3 | PP10-    | 10 GaAs pHEMT process                      | 33 |

|          | 2.4 | Freque   | ency doublers                              | 37 |

|          |     | 2.4.1    | Single diode                               | 38 |

|          |     | 2.4.2    | Balanced diodes                            | 38 |

|          |     | 2.4.3    | Transistor-based                           | 39 |

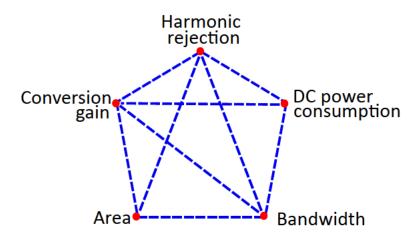

|          | 2.5 | Design   | a parameters of a frequency doubler        | 41 |

|          |     | 2.5.1    | Conversion gain                            | 42 |

|          |     | 2.5.2    | Bandwidth                                  | 42 |

|          |     | 2.5.3    | Power consumption                          | 43 |

|          |     | 2.5.4    | Area                                       | 43 |

|          |     | 2.5.5    | Harmonic rejection                         | 44 |

|          | 2.6 | Balun    |                                            | 45 |

|          | 2.7 | Summ     | ary                                        | 48 |

| 3        | Ana | alysis o | f harmonic generation in frequency doubler | 51 |

|          | 3.1 | Introd   | uction                                     | 51 |

|          | 3.2 | Harmo    | onic generation in a SG13S SiGe HBT        | 52 |

|          |     | 3.2.1    | Simple bipolar transistor model            | 52 |

|          |     | 3.2.2    | Foundry HBT model                          | 54 |

|          |     | 3.2.3    | Balanced doubler                           | 57 |

|          | 3.3 | Harmo    | onic generation in PP10-10 GaAs pHEMTs     | 68 |

|          |     | 3.3.1    | Simple FET model                           | 68 |

|          |     | 3.3.2    | Foundry GaAs pHEMT model                   | 69 |

|          |     | 3.3.3    | Balanced doubler                               | 72  |

|----------|-----|----------|------------------------------------------------|-----|

|          | 3.4 | Summ     | ary                                            | 81  |

| 4        | Bal | un des   | ign and implementation                         | 83  |

|          | 4.1 | Introd   | uction                                         | 83  |

|          | 4.2 | Design   | n considerations                               | 84  |

|          | 4.3 | Passiv   | e baluns                                       | 85  |

|          |     | 4.3.1    | Analysis of Marchand balun                     | 86  |

|          |     | 4.3.2    | Analysis of transformer balun                  | 89  |

|          |     | 4.3.3    | Balun selection                                | 91  |

|          | 4.4 | Opera    | ting principle of transformer balun            | 96  |

|          | 4.5 | Transf   | Former balun implementation in SG13S process   | 97  |

|          |     | 4.5.1    | Design details                                 | 97  |

|          |     | 4.5.2    | Layout and fabrication                         | 101 |

|          |     | 4.5.3    | Test and measurement results                   | 103 |

|          | 4.6 | Transf   | Former balun implementation in PP10-10 process | 105 |

|          |     | 4.6.1    | Design details                                 | 105 |

|          |     | 4.6.2    | Layout and fabrication                         | 109 |

|          |     | 4.6.3    | Test and measurement results                   | 112 |

|          | 4.7 | Evalua   | ation and comparison                           | 114 |

| <b>5</b> | K-b | and fr   | equency doubler implemented in SG13S process   | 117 |

|          | 5.1 | Introd   | uction                                         | 117 |

|          | 5.2 | Specifi  | ication                                        | 118 |

|          | 5.3 | Design   | 1                                              | 119 |

|          |     | 5.3.1    | Implementation                                 | 119 |

|          |     | 5.3.2    | Design flow                                    | 124 |

|          |     | 5.3.3    | Verification of layout cells                   | 126 |

|          | 5.4 | Final of | circuit layout                                 | 127 |

|          | 5.5 | Harmo    | onic rejection simulation and measurement      | 130 |

|          |     | 5.5.1    | Frequency sweep                                | 130 |

|   |     | 5.5.2                                                                             | Bias offset                                                                                                                                                                                                          |

|---|-----|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 5.5.3                                                                             | Input power sweep                                                                                                                                                                                                    |

|   | 5.6 | Discus                                                                            | ssion and conclusion $\ldots \ldots 139$                                                                                                |

| 6 | K-ŀ | Ka ban                                                                            | d frequency doubler implemented in PP10-10 process 141                                                                                                                                                               |

|   | 6.1 | Introd                                                                            | luction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $141$                                                                                                                                                                    |

|   | 6.2 | Specif                                                                            | $ication \dots \dots$                                                                                          |

|   | 6.3 | Design                                                                            | n                                                                                                                                                                                                                    |

|   |     | 6.3.1                                                                             | Implementation                                                                                                                                                                                                       |

|   |     | 6.3.2                                                                             | Design flow                                                                                                                                                                                                          |

|   | 6.4 | Final                                                                             | circuit layout                                                                                                                                                                                                       |

|   | 6.5 | Harmo                                                                             | onic rejection simulation and measurement $\ldots$ $\ldots$ $\ldots$ $\ldots$ $154$                                                                                                                                  |

|   |     | 6.5.1                                                                             | Frequency sweep                                                                                                                                                                                                      |

|   |     | 6.5.2                                                                             | Input power sweep                                                                                                                                                                                                    |

|   | 6.6 | Discus                                                                            | ssion and Conclusion                                                                                                                                                                                                 |

| 7 | Cor | nparis                                                                            | on of SG13S and PP10-10 processes 163                                                                                                                                                                                |

|   | 7.1 | Introd                                                                            | luction $\ldots \ldots 163$                                                                                 |

|   | 7.2 | Circui                                                                            | t design differences $\ldots \ldots 165$                                                             |

|   |     | 7.2.1                                                                             | Baluns                                                                                                                                                                                                               |

|   |     | 7.2.2                                                                             | Frequency doublers                                                                                                                                                                                                   |

|   | 7.3 |                                                                                   |                                                                                                                                                                                                                      |

|   |     | Imple                                                                             | mentation differences $\ldots \ldots 169$                                                                                 |

|   |     | Imple:<br>7.3.1                                                                   | mentation differences $\dots \dots \dots$                                                                            |

|   |     | -                                                                                 |                                                                                                                                                                                                                      |

|   |     | 7.3.1                                                                             | Layout complexity    170      Exploration of different topologies    170                                                                                                                                             |

|   | 7.4 | <ul><li>7.3.1</li><li>7.3.2</li><li>7.3.3</li></ul>                               | Layout complexity    170      Exploration of different topologies    170                                                                                                                                             |

|   |     | <ul><li>7.3.1</li><li>7.3.2</li><li>7.3.3</li><li>Linear</li></ul>                | Layout complexity       170         Exploration of different topologies       170         Compactness of layout       171         rity performance comparison       172                                              |

|   | 7.4 | <ul><li>7.3.1</li><li>7.3.2</li><li>7.3.3</li><li>Linear</li></ul>                | Layout complexity    170      Exploration of different topologies    170      Compactness of layout    171      rity performance comparison    172                                                                   |

|   | 7.4 | <ul><li>7.3.1</li><li>7.3.2</li><li>7.3.3</li><li>Linear</li><li>Applie</li></ul> | Layout complexity       170         Exploration of different topologies       170         Compactness of layout       171         rity performance comparison       172         cation to higher frequency       176 |

| 8            | Con   | clusio | n                                                                                            | 185        |

|--------------|-------|--------|----------------------------------------------------------------------------------------------|------------|

|              | 8.1   | Scope  | of Project                                                                                   | 186        |

|              | 8.2   | Projec | t Outcomes                                                                                   | 187        |

|              |       | 8.2.1  | Demonstrate frequency doubler as an indicator of process linearity                           | 187        |

|              |       | 8.2.2  | Analyse effect of topology on linearity                                                      | 189        |

|              |       | 8.2.3  | Frequency-doubler analysis                                                                   | 189        |

|              |       | 8.2.4  | Balun analysis                                                                               | 190        |

|              |       | 8.2.5  | Critical components of circuit implementation                                                | 191        |

|              |       | 8.2.6  | Selection of a suitable process                                                              | 195        |

|              | 8.3   | Future | e Opportunities                                                                              | 196        |

|              |       | 8.3.1  | Models for the HBTs                                                                          | 196        |

|              |       | 8.3.2  | Improvement of balun models $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 196        |

|              |       | 8.3.3  | Improvement of power level of second harmonic $\ldots \ldots \ldots$                         | 197        |

|              |       | 8.3.4  | Implementation of a E-band doubler                                                           | 197        |

| $\mathbf{A}$ | App   | oendix | Α                                                                                            | 199        |

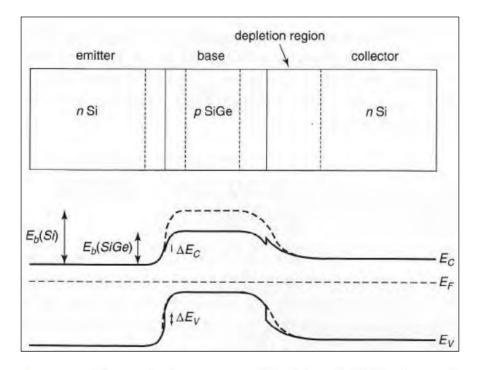

|              | A.1   | Energy | y Band Diagram                                                                               | 199        |

|              |       | A.1.1  | SiGe HBT                                                                                     | 200        |

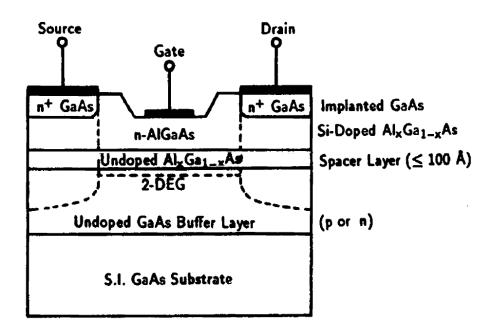

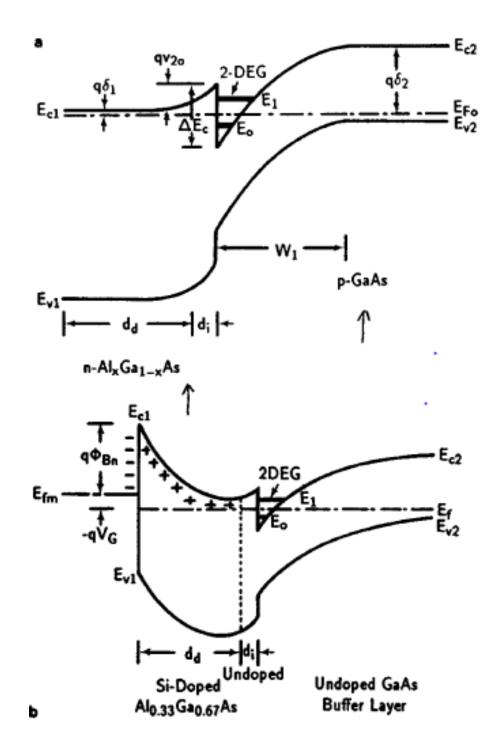

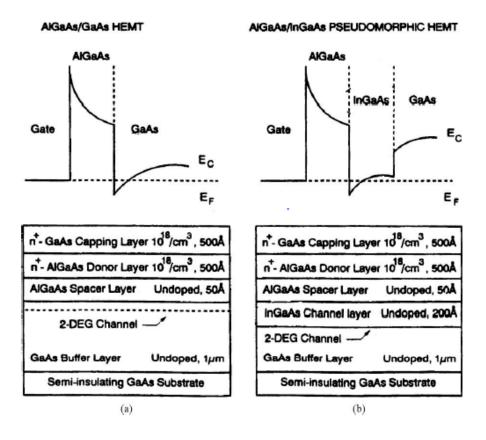

|              |       | A.1.2  | pHEMT                                                                                        | 201        |

| В            | App   | oendix | В                                                                                            | 207        |

|              | B.1   | SG13S  | process specification                                                                        | 207        |

|              | B.2   | PP10-  | 10 process specification                                                                     | 209        |

| С            | App   | oendix | С                                                                                            | <b>211</b> |

|              | C.1   | Fabric | ated circuits                                                                                | 211        |

| Re           | efere | nces   |                                                                                              | 213        |

# List of Figures

| 1.1  | Inventors of transistors at Bell Laboratories 1947 [AT&T archive]                | 2  |

|------|----------------------------------------------------------------------------------|----|

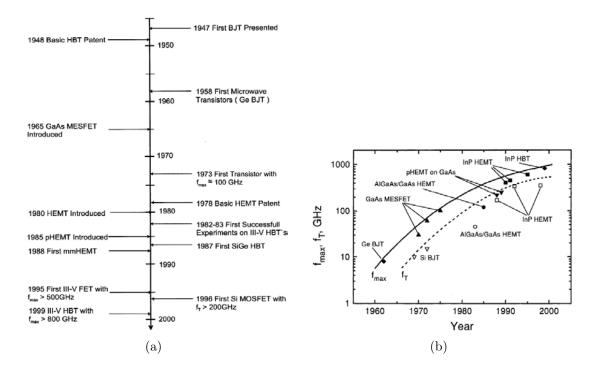

| 1.2  | (a) History of development of RF transistors, (b) Plot of $f_T$ and $f_{max}$ of |    |

|      | RF transistors over the years 1960 to 2000                                       | 3  |

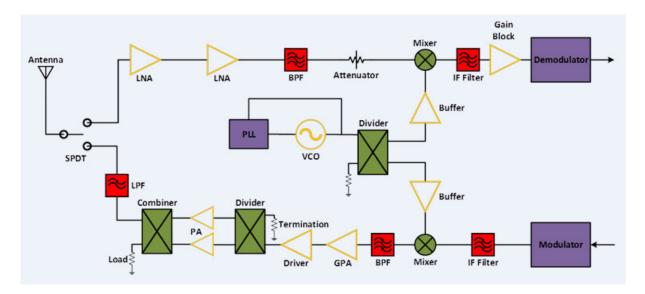

| 1.3  | Simplified block diagram of a wireless communication transceiver                 | 4  |

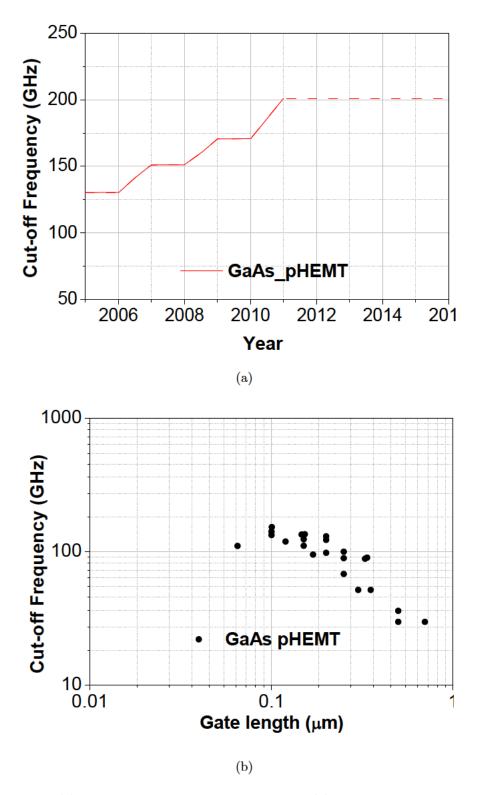

| 1.4  | (a) ITRS $f_T$ target for GaAs pHEMT. (b) Reported cut-off frequency             |    |

|      | $(f_T)$ versus gate length for GaAs pHEMT                                        | 10 |

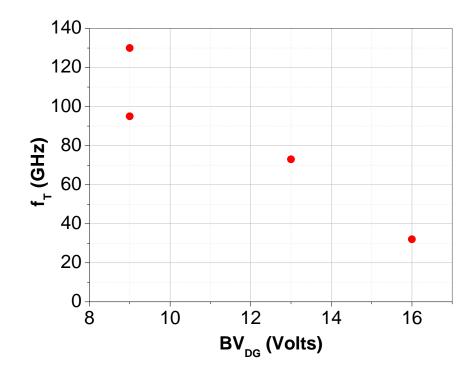

| 1.5  | The plot of breakdown voltage vs $f_T$ of GaAs pHEMTs available from             |    |

|      | WIN Semiconductors                                                               | 11 |

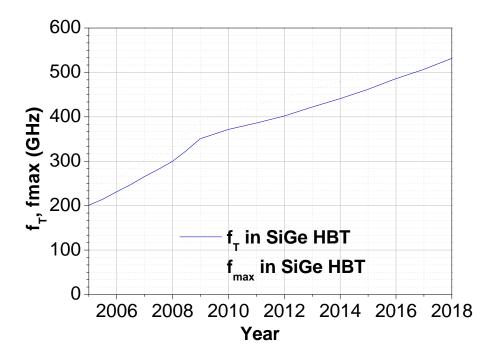

| 1.6  | ITRS $f_T$ and $f_{max}$ targets for SiGe HBT                                    | 12 |

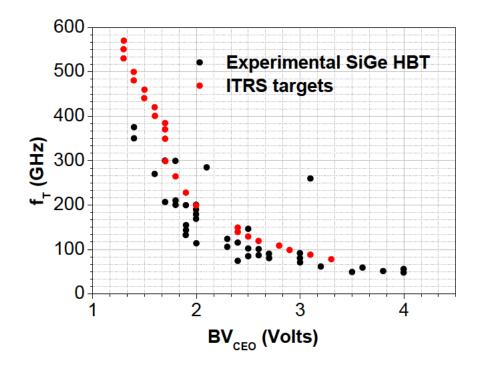

| 1.7  | Reported cut-off frequency $f_T$ as a function of the collector-emitter          |    |

|      | breakdown voltage $BV_{CEO}$ and the ITRS targets for a SiGe HBT                 | 13 |

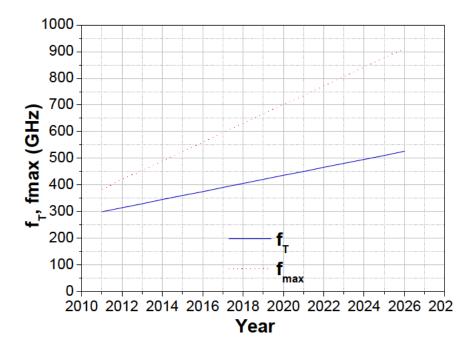

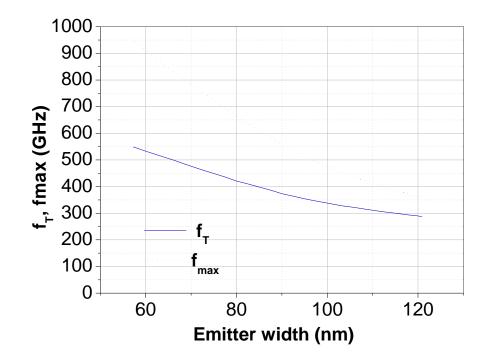

| 1.8  | The $f_T$ and $f_{max}$ targets in the Dot Seven project for SiGe HBT            | 13 |

| 1.9  | Estimated emitter width for projected $f_T$ and $f_{max}$ targets in the Dot     |    |

|      | Seven project for SiGe HBT                                                       | 14 |

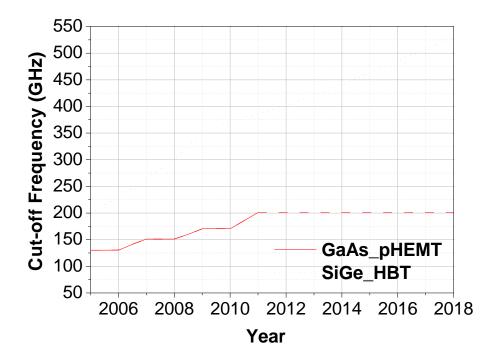

| 1.10 | Comparison of cut-off frequencies of GaAs pHEMT and SiGe HBT up                  |    |

|      | to 2018                                                                          | 15 |

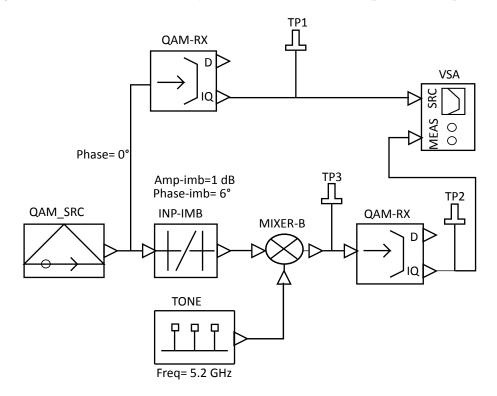

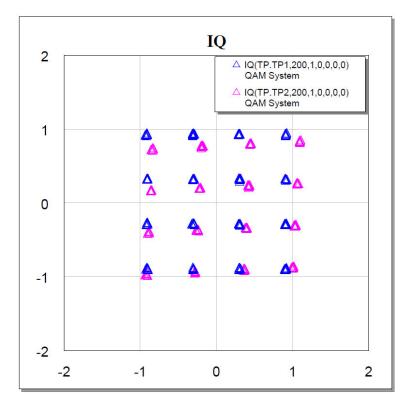

| 1.11 | 16-QAM system set-up in AWR using the built-in System blocks. $\ . \ .$          | 17 |

| 1.12 | Constellation diagram for a 16-QAM system with (pink) and without                |    |

|      | (blue) amplitude and phase imbalance in the input signal. $\ldots$ .             | 18 |

| 1.13 | 16-QAM system set-up in AWR with harmonics in the local oscillator               |    |

|      | signal, using the built-in System blocks                                         | 19 |

|      |                                                                                  |    |

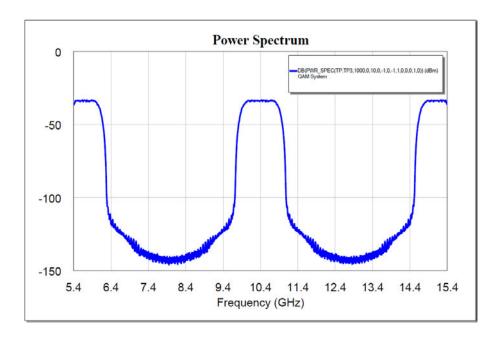

| 1.14 | The power spectrum of the QAM system with harmonics (upto third                                       |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | order) in the local oscillator signal. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 19 |

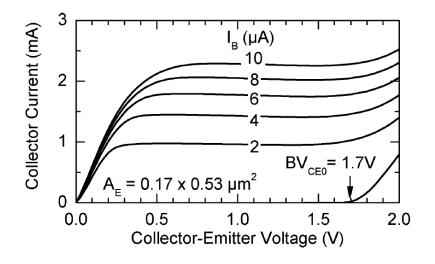

| 2.1  | Output characteristics of HS-HBT.                                                                     | 31 |

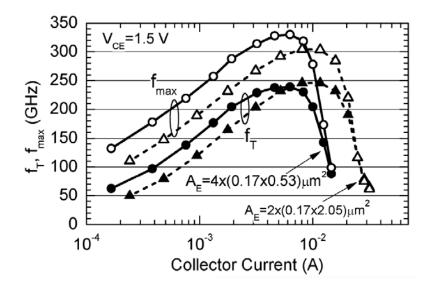

| 2.2  | $f_T$ and $f_{max}$ of the HS-HBT                                                                     | 31 |

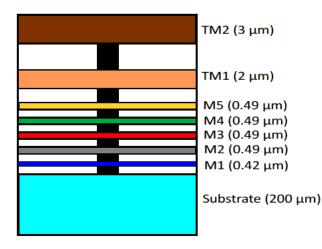

| 2.3  | Detailed cross-sectional view of the metal layers available in the SG13S                              |    |

|      | SiGe HBT process.                                                                                     | 32 |

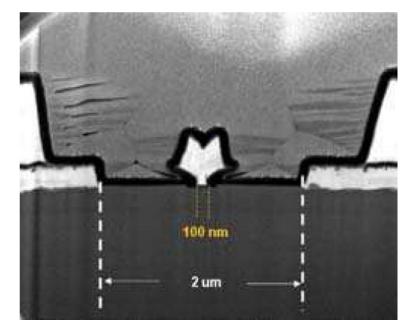

| 2.4  | The cross-section of a 0.1 $\mu {\rm m}$ GaAs PP10-10 pHEMT device                                    | 33 |

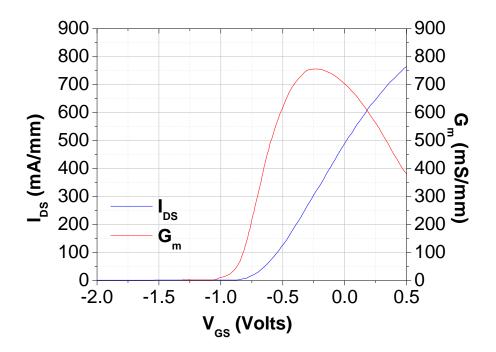

| 2.5  | Plot for transconductance and drain current of a 2 $\times$ 50 $\mu \rm m$ transistor                 |    |

|      | in the PP10-10 GaAs pHEMT process                                                                     | 34 |

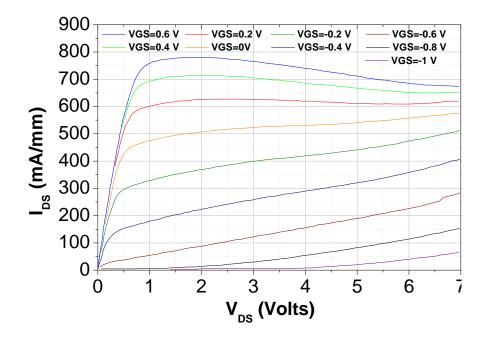

| 2.6  | IV characteristics of a 2 $\times$ 50 $\mu {\rm m}$ transistor in PP10-10 GaAs pHEMT                  |    |

|      | process                                                                                               | 35 |

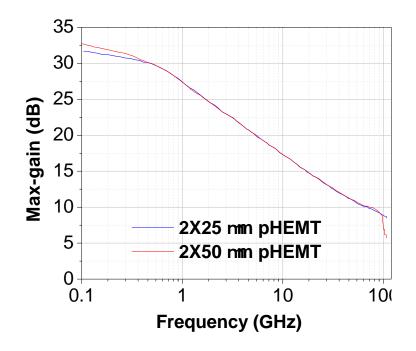

| 2.7  | Maximum gain performance of 2 $\times$ 25 $\mu \rm{m}$ and 2 $\times$ 50 $\mu \rm{m}$ transistors in  |    |

|      | PP10-10 GaAs pHEMT process                                                                            | 35 |

| 2.8  | Metal stack-up available in the PP10-10 GaAs pHEMT process                                            | 36 |

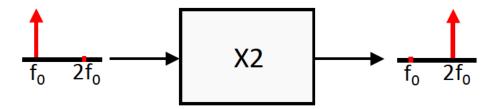

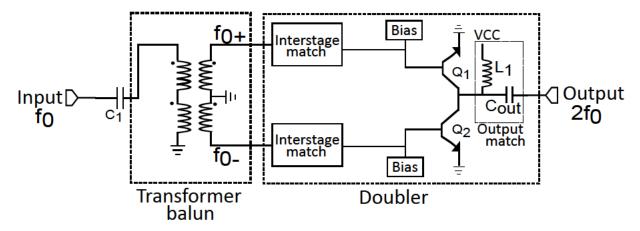

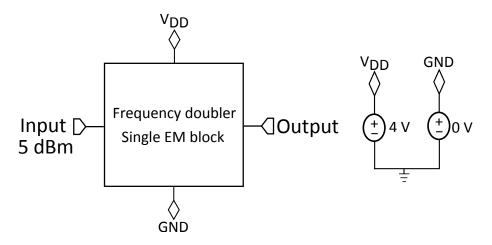

| 2.9  | Block diagram of a frequency doubler.                                                                 | 37 |

| 2.10 | Tradeoff between the design parameters of a frequency doubler. $\ldots$                               | 41 |

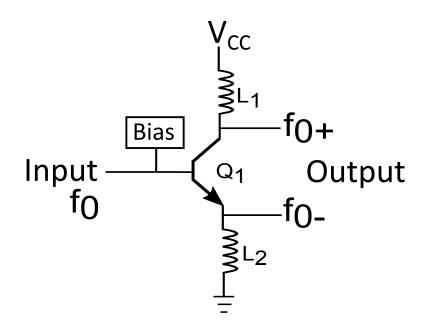

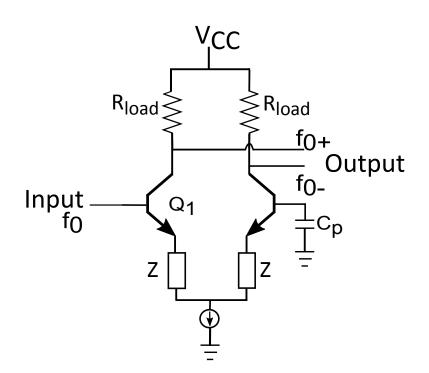

| 2.11 | Active balun using a single transistor                                                                | 46 |

| 2.12 | Active balun using a modified differential-pair configuration                                         | 47 |

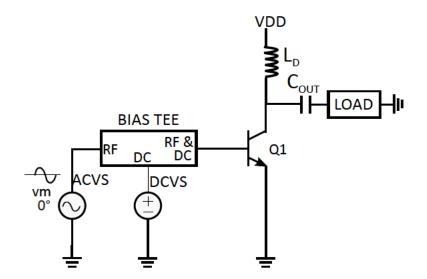

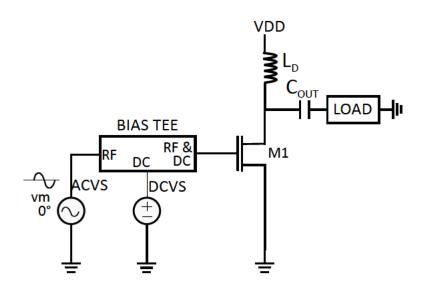

| 3.1  | Test bench for simulating the harmonics in collector current of a SG13S                               |    |

|      | SiGe HBT                                                                                              | 54 |

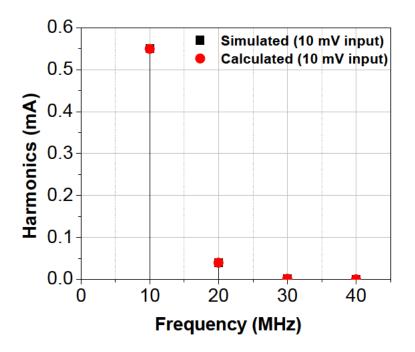

| 3.2  | Comparison of the simulated (black line) and calculated (red dot) mag-                                |    |

|      | nitudes of harmonics in the collector current of a SG13S SiGe HBT, for                                |    |

|      | a 10 MHz input                                                                                        | 56 |

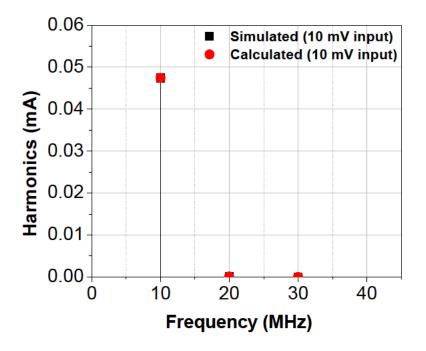

| 3.3  | Test bench for simulating the harmonics in collector current of an ideal                              |    |

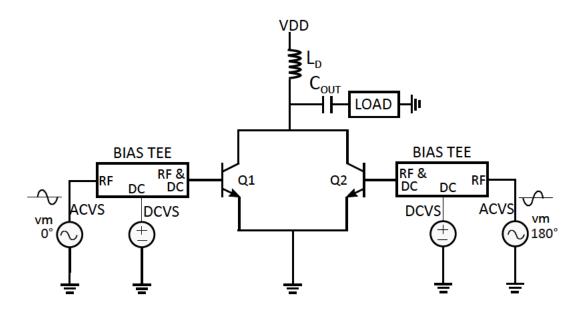

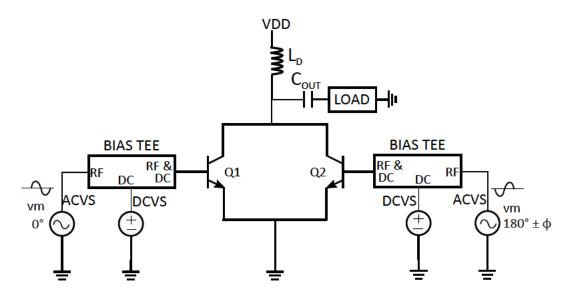

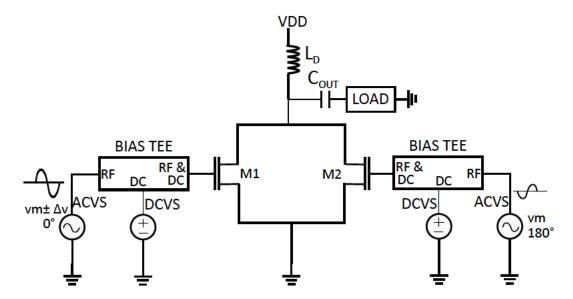

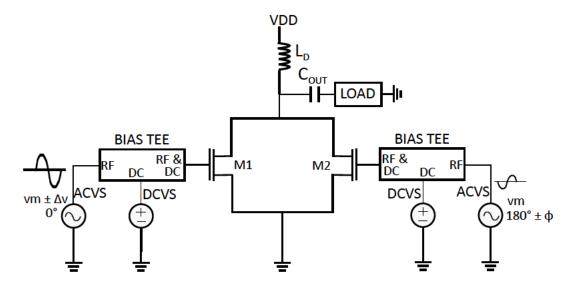

|      | push-push doubler.                                                                                    | 57 |

| 3.4  | Comparison of the simulated (black line) and calculated (red dot) magni-                              |    |

|      | tudes of harmonics in collector current for the push-push configuration,                              |    |

|      | at 10 MHz input.                                                                                      | 59 |

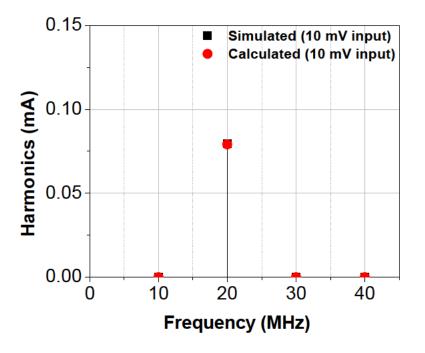

| 3.5  | Test bench for simulating the harmonics in the collector current of a           |    |

|------|---------------------------------------------------------------------------------|----|

|      | push-push doubler with magnitude imbalance in the input differential            |    |

|      | signals                                                                         | 61 |

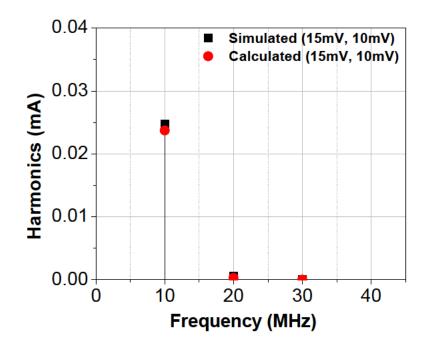

| 3.6  | Comparison of the simulated (black line) and calculated (red dot) mag-          |    |

|      | nitudes of harmonics in collector current for magnitude mismatch of 5           |    |

|      | mV, with 10 MHz input signal.                                                   | 62 |

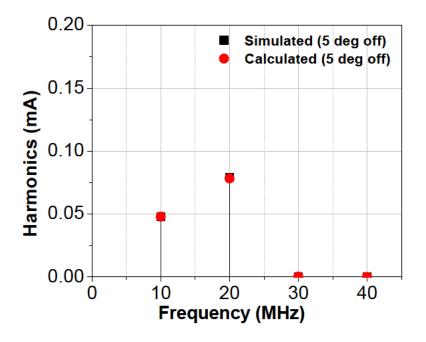

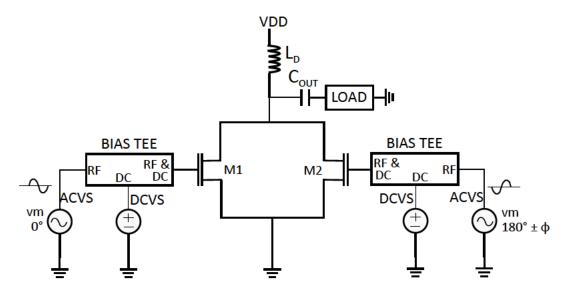

| 3.7  | Test bench for simulating the harmonics in the collector current of a           |    |

|      | push-push doubler with a phase imbalance in the input differential signals.     | 64 |

| 3.8  | Comparison between the simulated (black line) and the calculated (red           |    |

|      | dot) magnitudes of the harmonics in the collector current of a push-push        |    |

|      | doubler with a phase imbalance of $5^{o}$ in the input differential signals, at |    |

|      | 10 MHz input                                                                    | 64 |

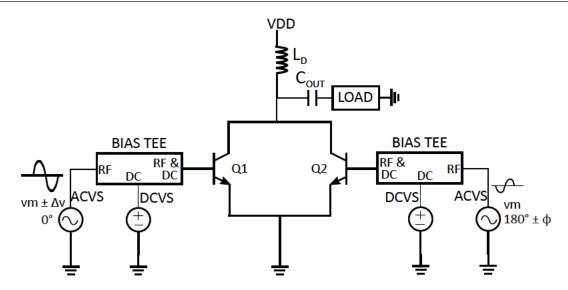

| 3.9  | Test bench for simulating the harmonics in the collector current of a           |    |

|      | push-push doubler with both magnitude and phase imbalance in the                |    |

|      | input differential signals.                                                     | 66 |

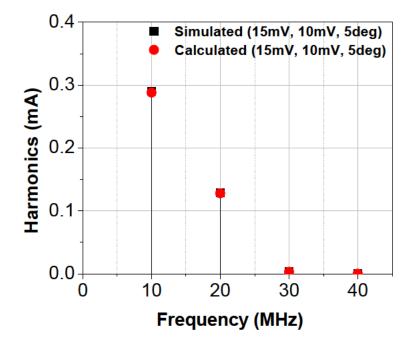

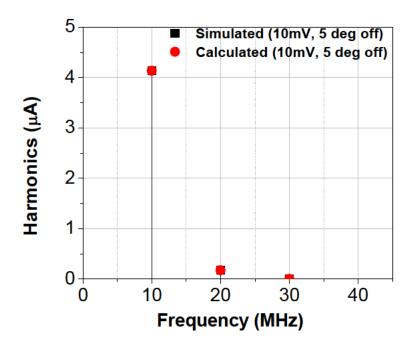

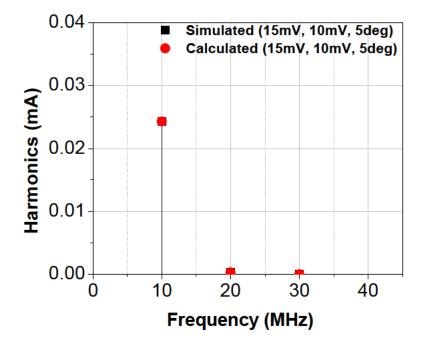

| 3.10 | Comparison of the simulated (black line) and calculated (red dot) mag-          |    |

|      | nitudes of the harmonics in the collector current of a push-push doubler        |    |

|      | with a magnitude imbalance of 5 mV (15 mV, 10 mV) and a phase                   |    |

|      | imbalance of $5^{\circ}$ , in the input differential signals at 10 MHz input    | 67 |

| 3.11 | Test bench for simulating the harmonics in the drain current of a PP10-         |    |

|      | 10 GaAs pHEMT                                                                   | 70 |

| 3.12 | Comparison of the simulated (black line) and calculated (red dot) magni-        |    |

|      | tudes of harmonics in the drain current of a pHEMT in PP10-10 process,          |    |

|      | for a 10 MHz input signal                                                       | 71 |

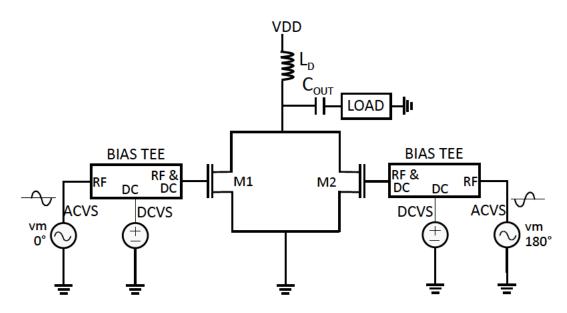

| 3.13 | Test bench for simulating the harmonics in the drain current of a push-         |    |

|      | push doubler using pHEMTs in PP10-10 process.                                   | 73 |

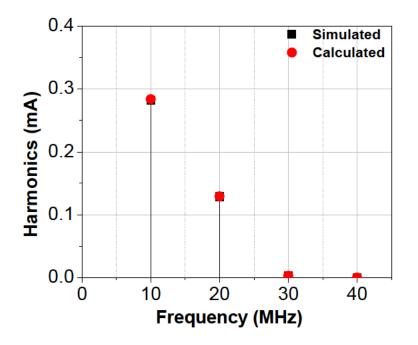

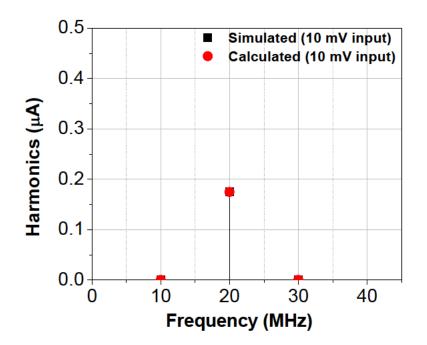

| 3.14 | Comparison of the simulated (black line) and calculated (red dot) mag-          |    |

|      | nitudes of the harmonics in the drain current of the push-push doubler          |    |

|      | implemented using PP10-10 GaAs pHEMTs, for 10 MHz input differen-               |    |

|      | tial signals.                                                                   | 74 |

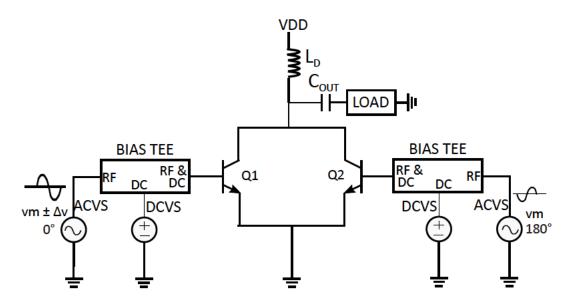

| 3.15 | Test bench for simulating the harmonics in drain current of the push-          |    |

|------|--------------------------------------------------------------------------------|----|

|      | push doubler with magnitude imbalance in the input differential signal.        | 74 |

| 3.16 | Comparison of the simulated (black line) and calculated (red dot) mag-         |    |

|      | nitudes of harmonics in drain current of the doubler with a magnitude          |    |

|      | mismatch of 5 mV in the input differential signals, at 10 MHz                  | 76 |

| 3.17 | Test bench for simulating the harmonics in the drain current of the            |    |

|      | push-push doubler with phase imbalance in the input differential signals.      | 77 |

| 3.18 | Comparison between the simulated (black line) and the calculated (red          |    |

|      | dot) magnitudes of the harmonics in the drain current of the push-push         |    |

|      | doubler with a phase imbalance of $5^o$ in the input differential signals, at  |    |

|      | 10 MHz                                                                         | 78 |

| 3.19 | Test bench for simulating the harmonics in the drain current of the            |    |

|      | push-push doubler with both magnitude and phase imbalance in the               |    |

|      | input differential signals                                                     | 79 |

| 3.20 | Comparison of the simulated and calculated harmonics in the drain cur-         |    |

|      | rent of a push-push doubler with a magnitude imbalance of 5 mV (15 $$          |    |

|      | mV, 10 mV) and phase imbalance of $5^{o}$ , in the input differential signals, |    |

|      | at 10 MHz                                                                      | 80 |

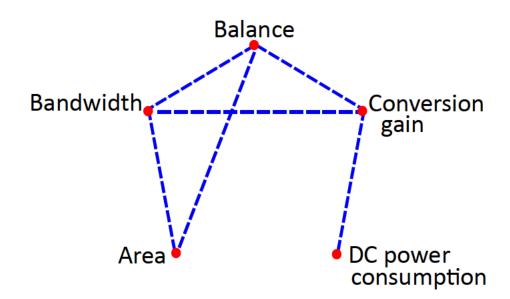

| 4.1  | Tradeoff between the different key parameters of a balun                       | 85 |

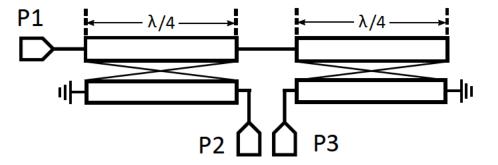

| 4.2  | Marchand balun configuration with two identical coupled lines                  | 86 |

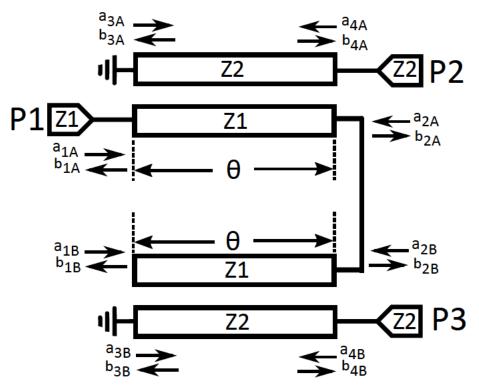

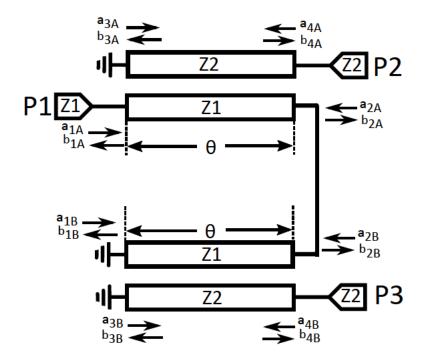

| 4.3  | Block diagram of Marchand balun with two identical coupled lines. $\ .$ .      | 87 |

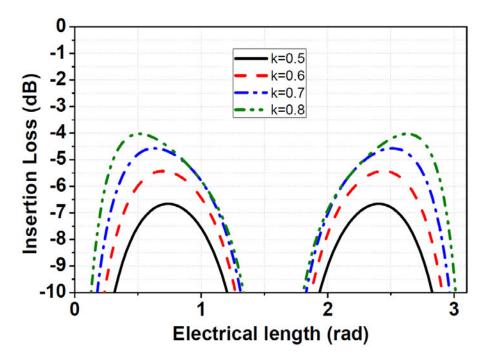

| 4.4  | Insertion loss of Marchand balun with respect to electrical length for         |    |

|      | varying coupling coefficient.                                                  | 88 |

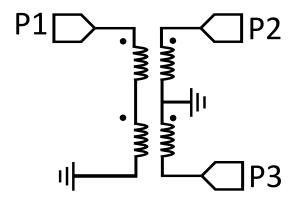

| 4.5  | Transformer balun configuration with two identical coupled line                | 89 |

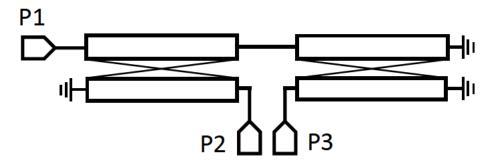

| 4.6  | Block diagram of transformer balun with two identical coupled lines.           | 89 |

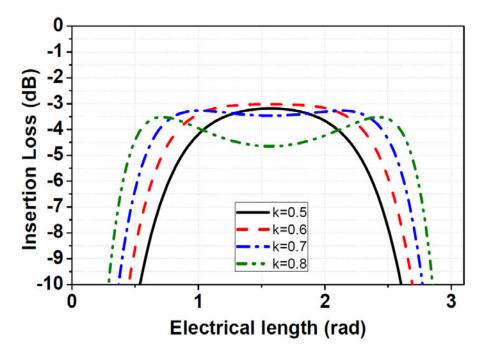

| 4.7  | Insertion loss of transformer balun with respect to electrical length for      |    |

|      | varying coupling coefficient.                                                  | 90 |

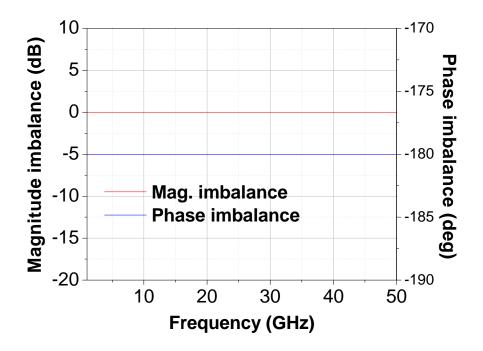

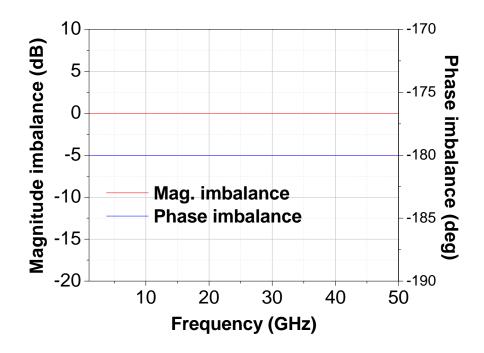

| 4.8  | Amplitude and phase imbalance of a typical coupled-line Marchand               |    |

|      | balun simulated in AWR                                                         | 92 |

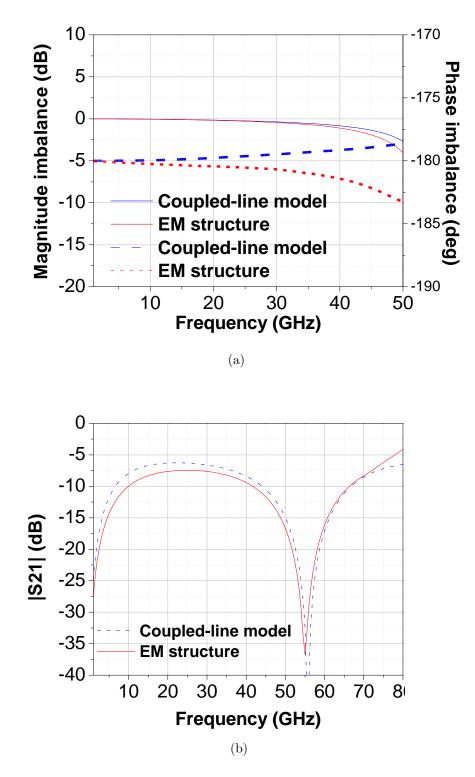

| 4.9  | Amplitude and phase imbalance of a typical coupled-line transformer                   |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | balun simulated in AWR                                                                | 92  |

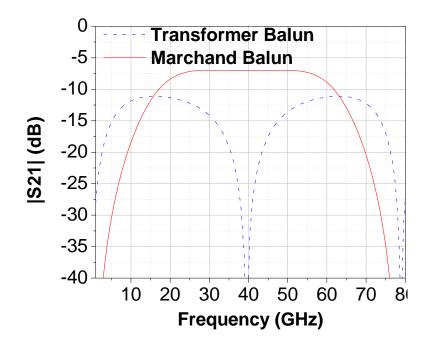

| 4.10 | Bandwidth of a typical coupled-line Marchand balun and a transformer                  |     |

|      | balun simulated in AWR                                                                | 93  |

| 4.11 | Comparison of coupled-line model and EM simulation of a transformer                   |     |

|      | balun. (a) Magnitude imbalance and Phase imbalance (b) Insertion loss                 |     |

|      | and bandwidth                                                                         | 94  |

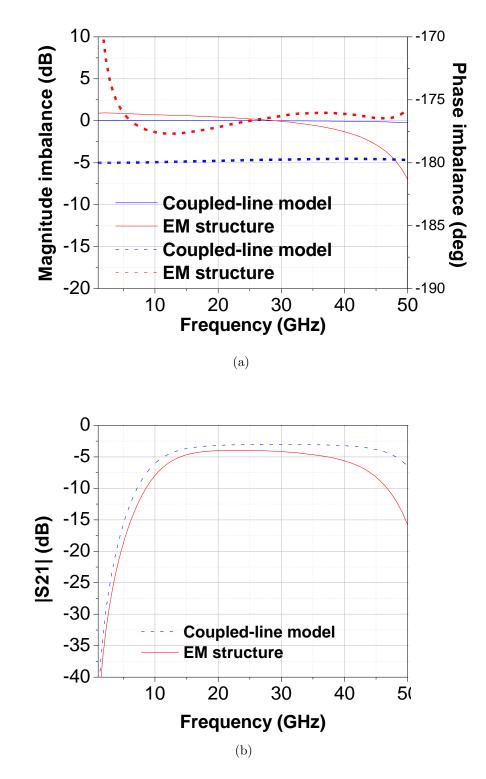

| 4.12 | Comparison of coupled-line model and EM simulation of a Marchand                      |     |

|      | balun. (a) Magnitude imbalance and Phase imbalance (b) Bandwidth                      | 95  |

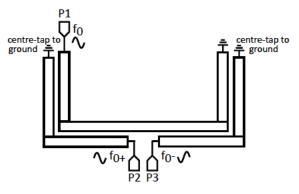

| 4.13 | Block diagram of Transformer balun.                                                   | 96  |

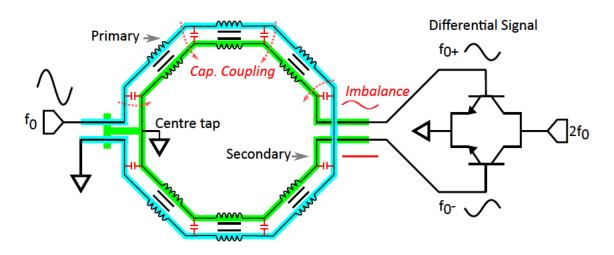

| 4.14 | Schematic representation of Transformer balun with doubler                            | 98  |

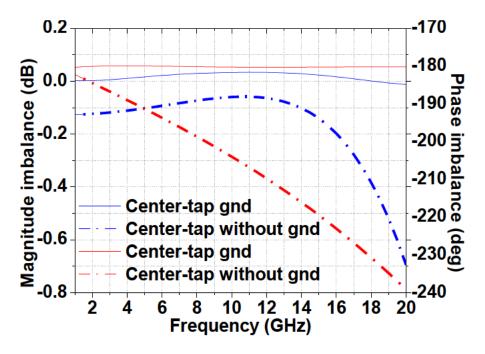

| 4.15 | Magnitude imbalance (blue) and phase imbalance (red) with (solid) and                 |     |

|      | without (dotted) centre-tap ground on secondary for 6 $\mu \mathrm{m}$ offset between |     |

|      | the coil radii.                                                                       | 98  |

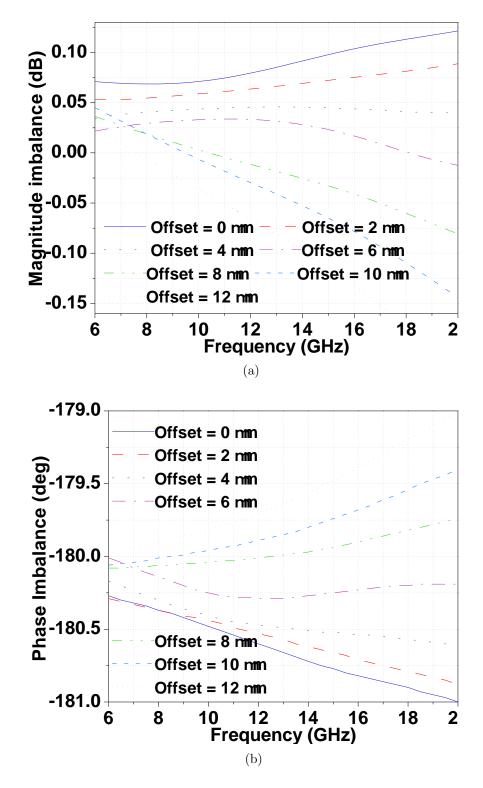

| 4.16 | Effect of varying offset between primary and secondary coil radii. (a)                |     |

|      | Simulated magnitude imbalance and (b) simulated phase imbalance.                      | 99  |

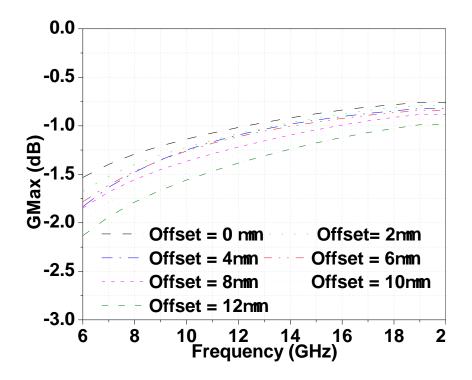

| 4.17 | Plot of Gmax for the transformer balun for varying radius offset                      | 100 |

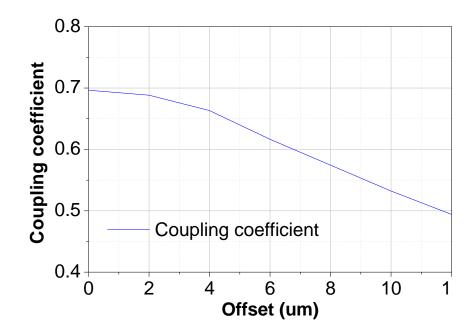

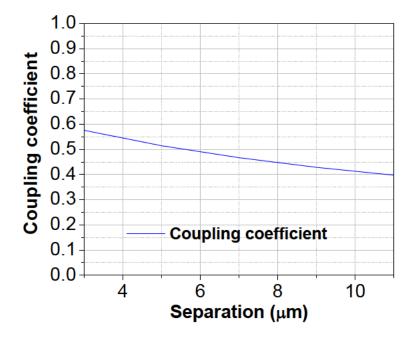

| 4.18 | plot of coupling coefficient with respect to varying radius offset                    | 101 |

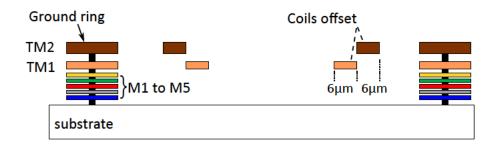

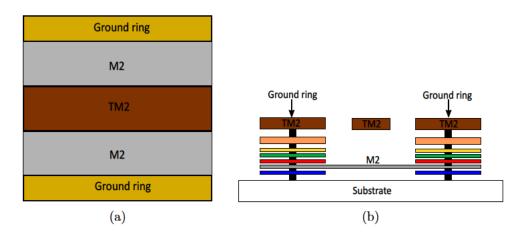

| 4.19 | Cross-sectional view of the metal stack-up of SG13S SiGe HBT process                  |     |

|      | showing offset radius coils in the balun                                              | 102 |

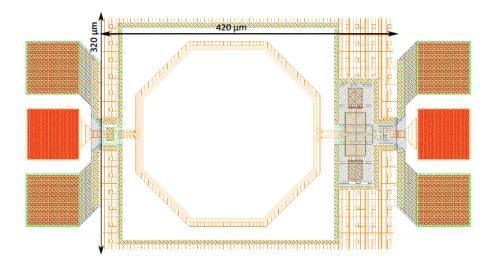

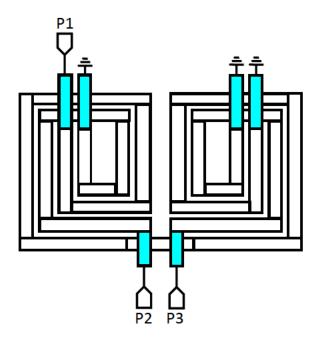

| 4.20 | Layout of the designed transformer balun.                                             | 102 |

| 4.21 | (a) Diagram showing the position of on-chip resistors to facilitate two               |     |

|      | port measurements. (b) Die photo of transformer balun characterisation                |     |

|      | structures                                                                            | 103 |

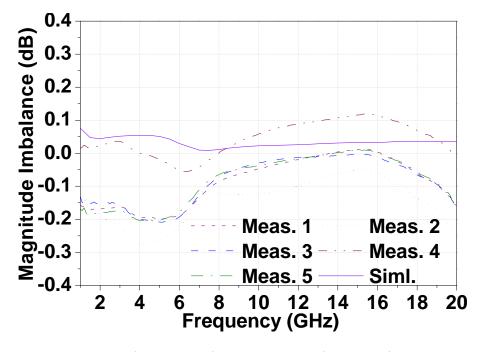

| 4.22 | Measured (dotted lines) and simulated (solid lines) magnitude imbalance               |     |

|      | across five dice                                                                      | 104 |

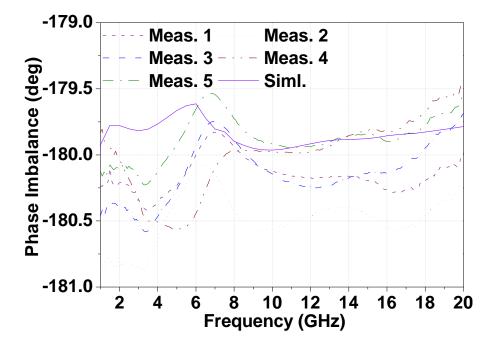

| 4.23 | Measured (dotted lines) and simulated (solid lines) phase imbalance                   |     |

|      | across five dice.                                                                     | 104 |

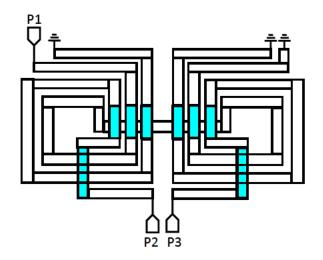

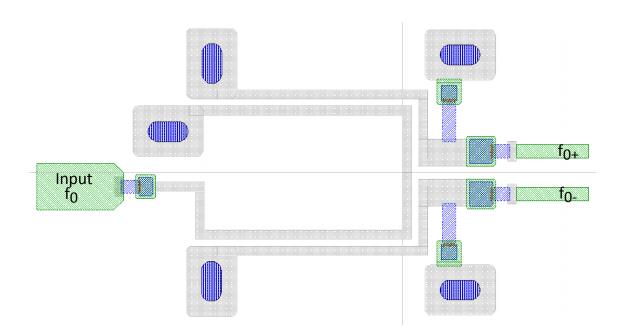

| 4.24 | Layout of the proposed balun                                                          | 106 |

| 4.25 | Layout of the conventional spiral balun                                               | 107 |

| 4.26 | Layout of the conventional spiral balun                                  | 107 |

|------|--------------------------------------------------------------------------|-----|

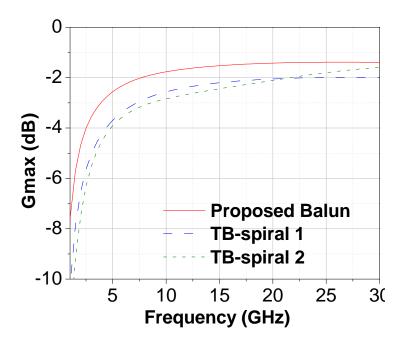

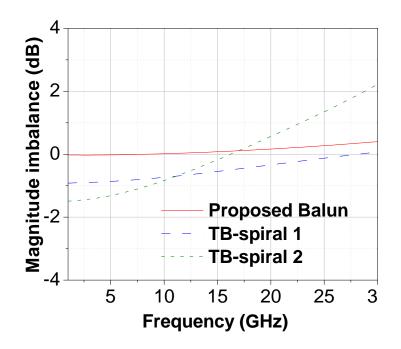

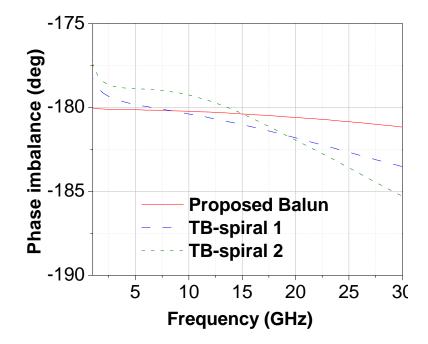

| 4.27 | Plot of Gmax for the "U-shaped" and the other two spiral transformer     |     |

|      | baluns                                                                   | 108 |

| 4.28 | Plot of Amplitude imbalance for the "U-shaped" and the other two spiral  |     |

|      | transformer baluns                                                       | 108 |

| 4.29 | Plot of Phase imbalance for the "U-shaped" and the other two spiral      |     |

|      | transformer baluns                                                       | 109 |

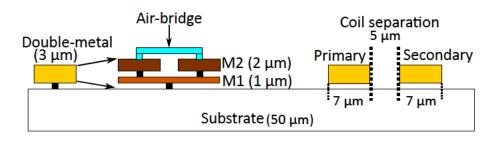

| 4.30 | PP10-10 GaAs pHEMT process cross-section.                                | 110 |

| 4.31 | Coupling coefficient for different spacing between the primary and the   |     |

|      | secondary coils.                                                         | 110 |

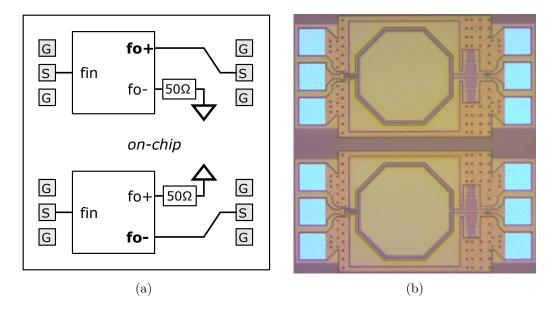

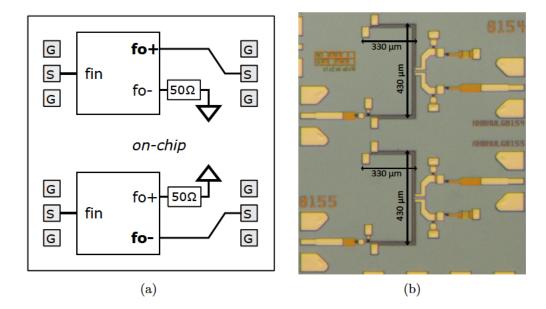

| 4.32 | (a) Diagram showing the position of on-chip resistors to facilitate two- |     |

|      | port measurements. (b) Die photo of transformer balun characterisation   |     |

|      | structures                                                               | 111 |

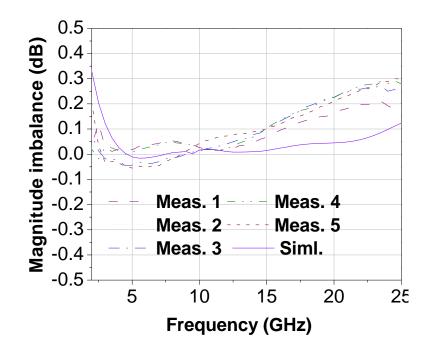

| 4.33 | Measured (dotted lines) and simulated (solid line) amplitude imbalance   |     |

|      | of the transformer balun across five dice                                | 113 |

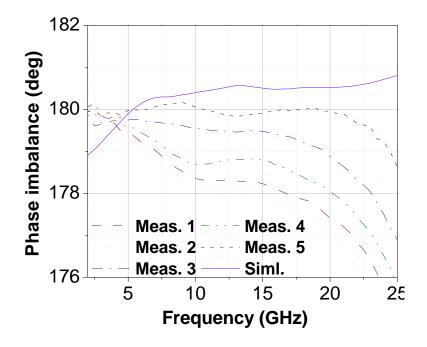

| 4.34 | Measured (dotted lines) and simulated (solid line) phase imbalance of    |     |

|      | the transformer balun across five dice.                                  | 113 |

| 5.1  | Schematic of the designed frequency doubler                              | 120 |

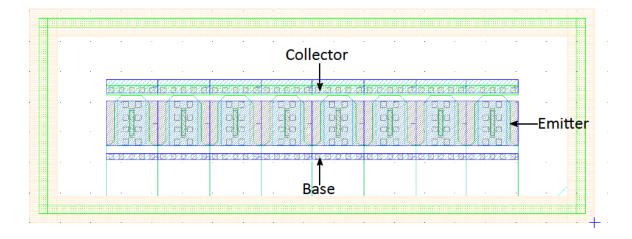

| 5.2  | Layout of a single transistor as used in the frequency-doubler core      | 120 |

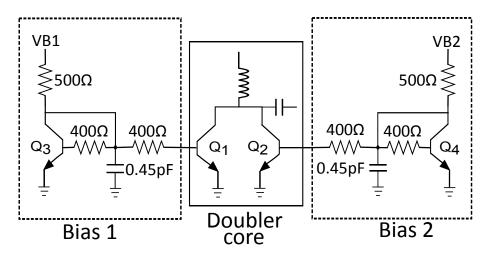

| 5.3  | Biasing circuit of the frequency doubler.                                | 121 |

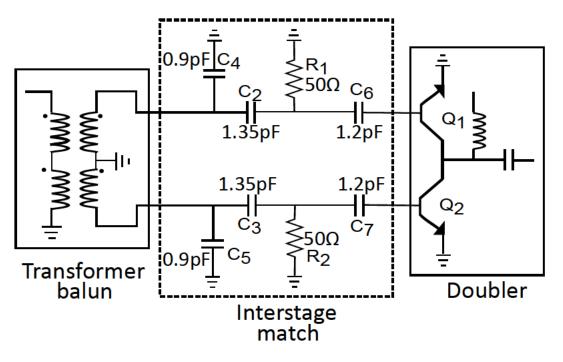

| 5.4  | Interstage matching circuit of the frequency-doubler.                    | 122 |

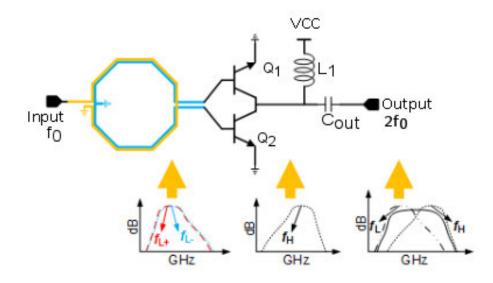

| 5.5  | Simplified schematic of the proposed staggered tuning frequency doubler. | 123 |

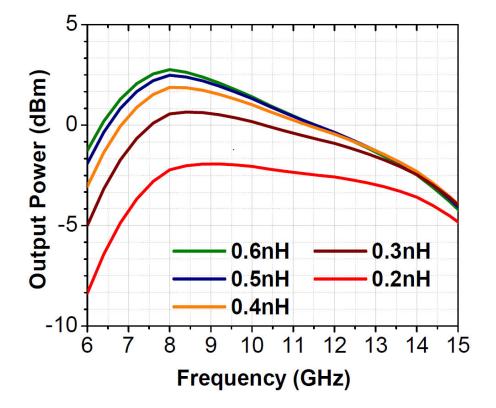

| 5.6  | Simulated output power of the frequency doubler in terms of second       |     |

|      | harmonic as a function of input frequency with swept inductance value    |     |

|      | of $L_1$                                                                 | 124 |

| 5.7  | Diagram of a transmission line (a) P-cell (b) cross-sectional view       | 127 |

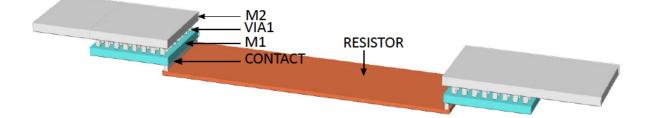

| 5.8  | Connection of a resistor in M2 layer.                                    | 128 |

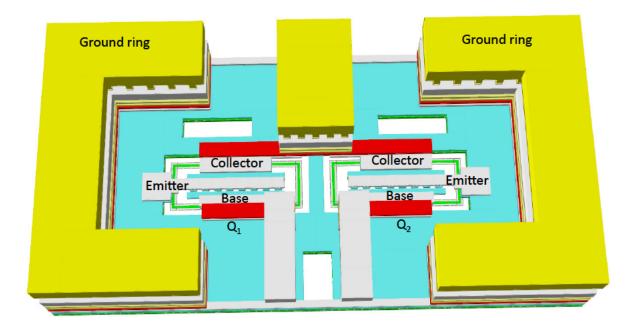

| 5.9  | Layout of the doubler core                                               | 128 |

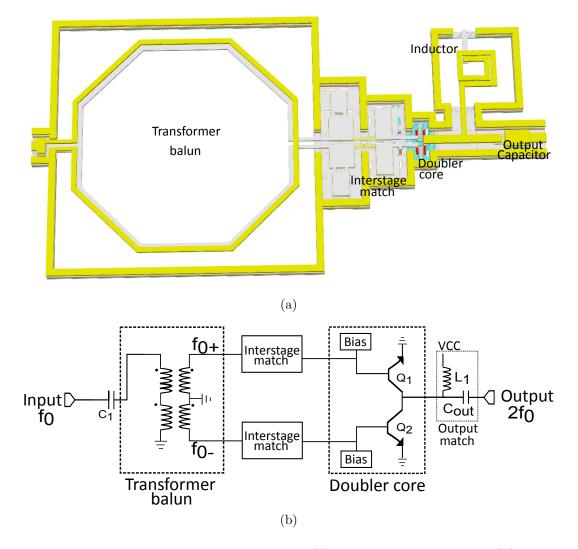

| 5.10 | The frequency doubler design (a) layout of the RF chain, (b) schematic                                                                                                                                                                                                                                                                               |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | diagram                                                                                                                                                                                                                                                                                                                                              | 129 |

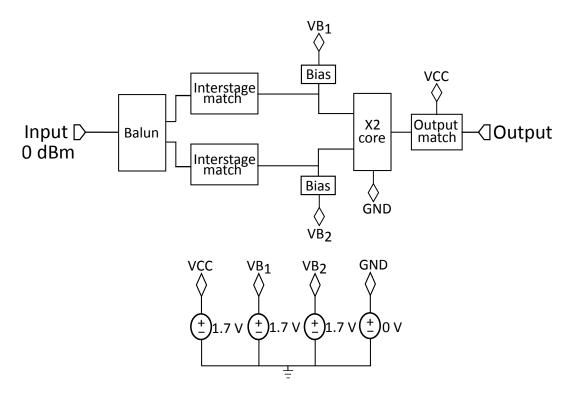

| 5.11 | Test-bench for simulating the harmonics with 0 dBm input                                                                                                                                                                                                                                                                                             | 131 |

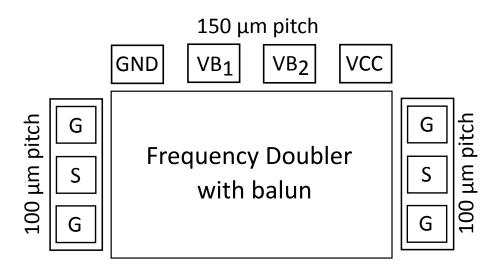

| 5.12 | Pin configuration for measurement of the frequency doubler                                                                                                                                                                                                                                                                                           | 131 |

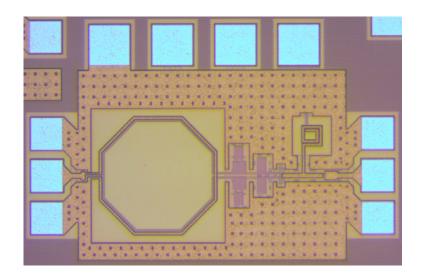

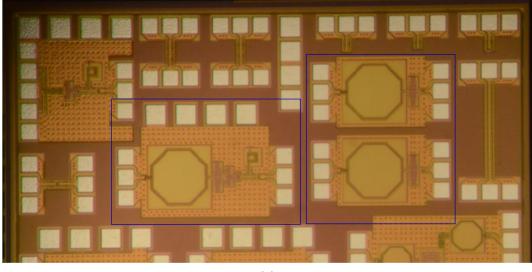

| 5.13 | The die-photo of the frequency doubler                                                                                                                                                                                                                                                                                                               | 132 |

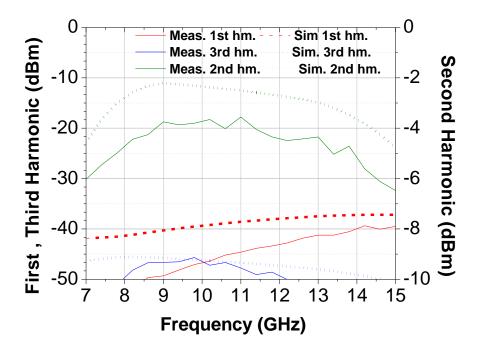

| 5.14 | Output power of harmonics as a function of input frequency, measured (solid) and simulated (dotted), fundamental (red lines), second harmonic (green lines) and third harmonic (blue lines)                                                                                                                                                          | 132 |

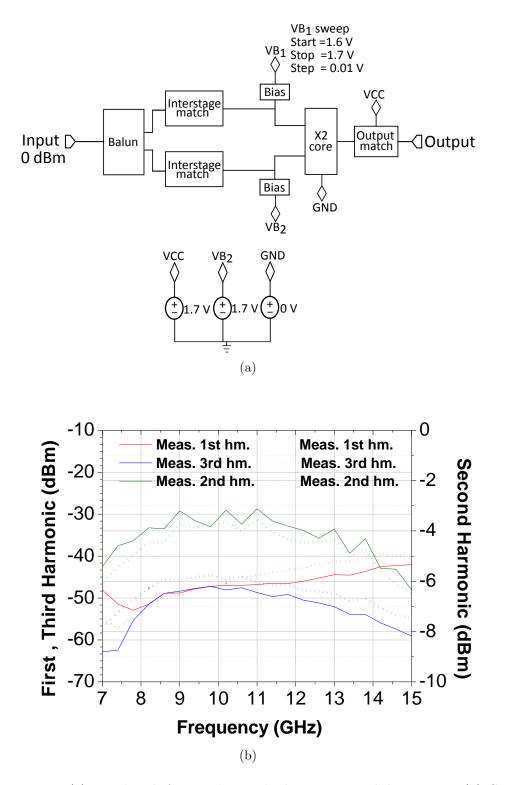

| 5.15 | <ul> <li>(a) Test-bench for simulating the harmonics with bias sweep, (b) Comparison of the measured results for the harmonics with equal and different bias, equal bias 1.7 V on each line (dotted), unequal bias 1.68V-1.70</li> <li>V (solid). Fundamental (red lines), second harmonic (green lines) and third harmonic (blue lines).</li> </ul> | 134 |

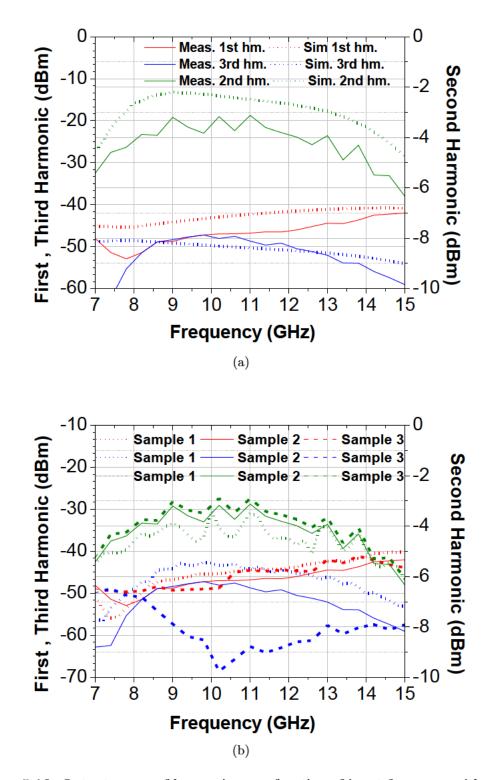

| 5.16 | Output power of harmonics as a function of input frequency with un-<br>equal bias, 1.68 V and 1.70 V: (a) comparison of measured (solid) and<br>simulated (dotted) results, (b) measured results for three samples                                                                                                                                   | 135 |

| 5.17 | Test-bench for simulating the harmonics with input power sweep                                                                                                                                                                                                                                                                                       | 136 |

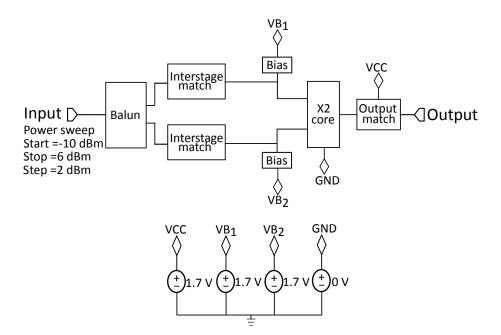

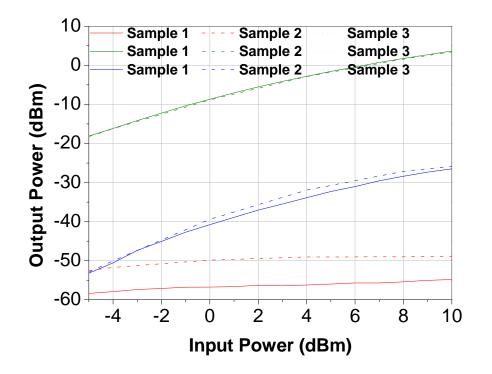

| 5.18 | Output power of harmonics as a function of input power: (a) measured results of three samples for 7 GHz input, (b) measured results of three samples for 11 GHz input. Fundamental (red lines), second harmonic (green lines) and third harmonic (blue lines)                                                                                        | 137 |

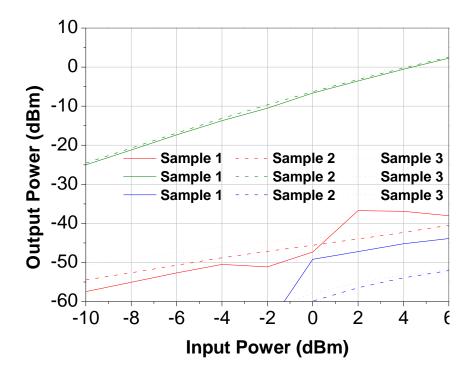

| 5.19 | Measured results of output power of harmonics as a function of input<br>power across three samples for 15 GHz input. Fundamental (red lines),<br>second harmonic (green lines) and third harmonic (blue lines)                                                                                                                                       | 138 |

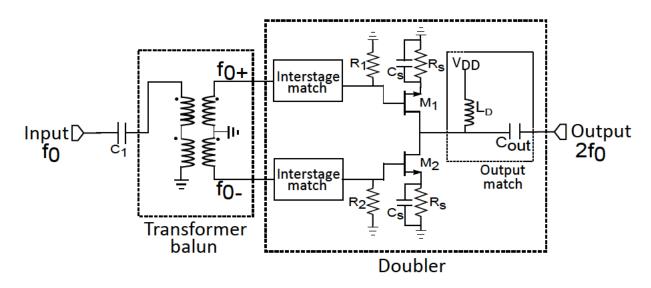

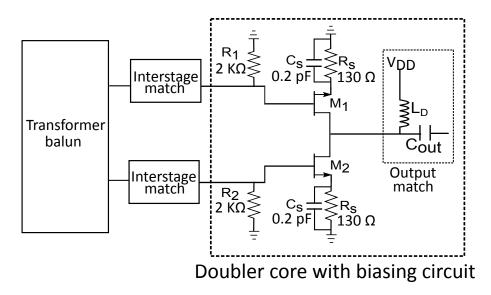

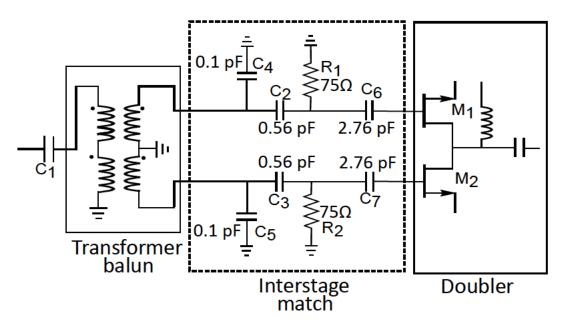

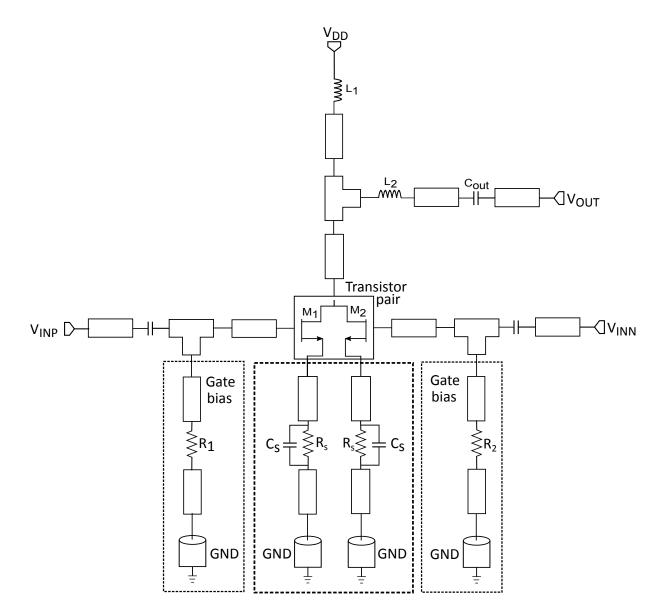

| 6.1  | Schematic of the designed frequency doubler                                                                                                                                                                                                                                                                                                          | 144 |

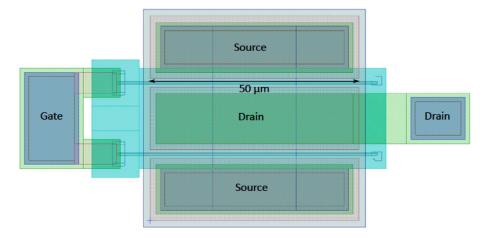

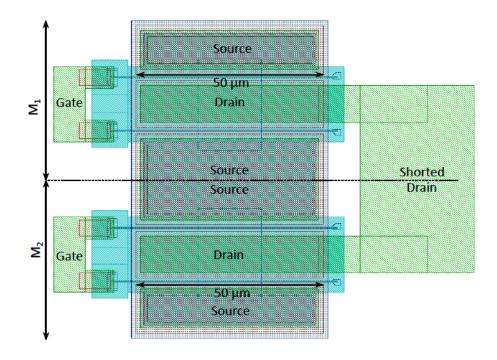

| 6.2  | Layout of a single transistor used in the frequency doubler                                                                                                                                                                                                                                                                                          | 144 |

| 6.3  | Layout of the two transistors of the frequency doubler                                                                                                                                                                                                                                                                                               | 145 |

| 6.4  | Schematic of the matching circuit between the transformer balun and                                              |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

|      | the frequency doubler (biasing resistor at the gate is omitted in the figure                                     |     |

|      | for simplicity)                                                                                                  | 146 |

| 6.5  | Schematic of the frequency doubler using the closed-form elements                                                | 148 |

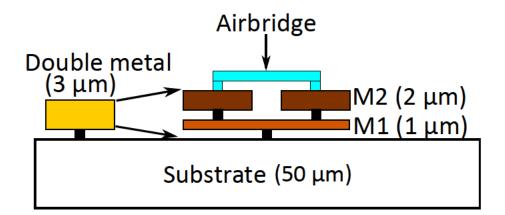

| 6.6  | Layout of the two transistors of the frequency-doubler core                                                      | 151 |

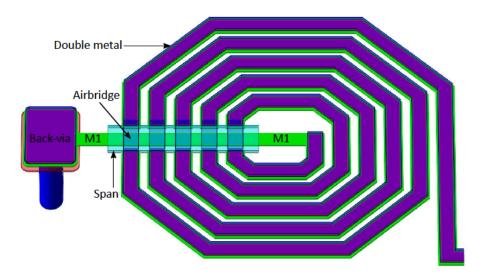

| 6.7  | Diagram showing the cross-over implementation in the PP10-10 GaAs                                                |     |

|      | pHEMT process using an airbridge                                                                                 | 151 |

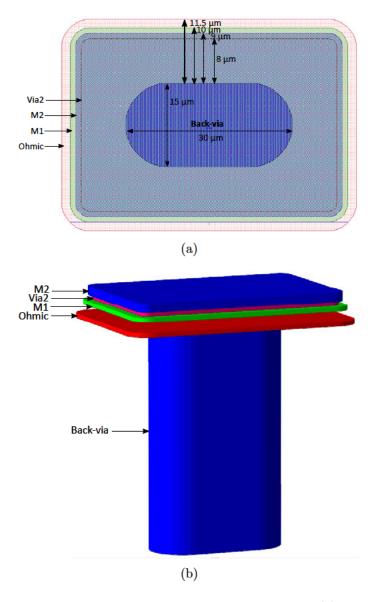

| 6.8  | The layout of a back-via for ground connection: (a) 2D view (b) 3D view.                                         | 152 |

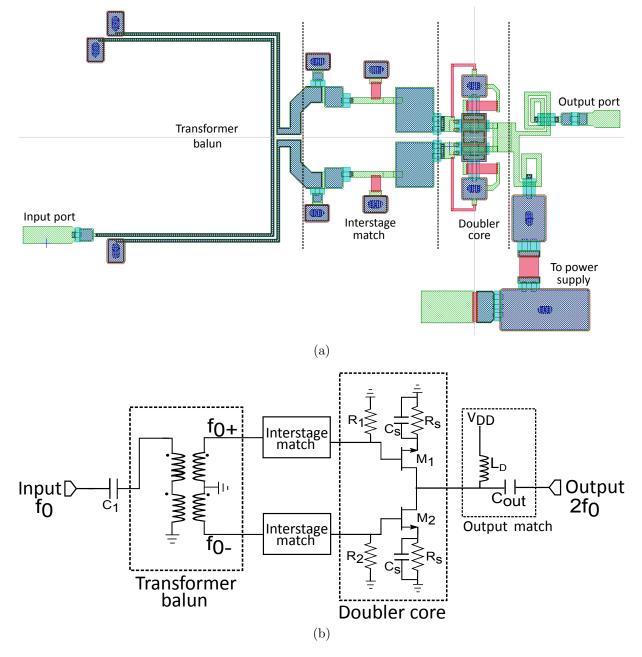

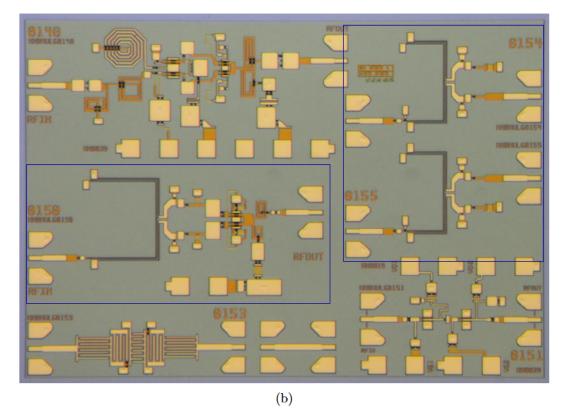

| 6.9  | The frequency doubler design (a) layout with the transformer balun, (b)                                          |     |

|      | schematic diagram.                                                                                               | 153 |

| 6.10 | Test-bench for simulation of the harmonics.                                                                      | 154 |

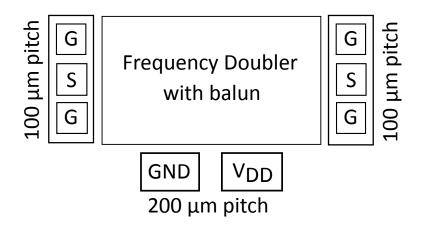

| 6.11 | Diagram showing the pin configuration of the frequency doubler with                                              |     |

|      | the transformer balun. $\ldots$ | 155 |

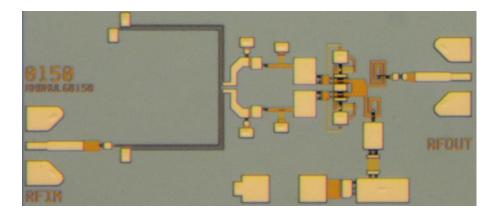

| 6.12 | Die-photo of the frequency doubler with the transformer balun. $\ . \ . \ .$                                     | 155 |

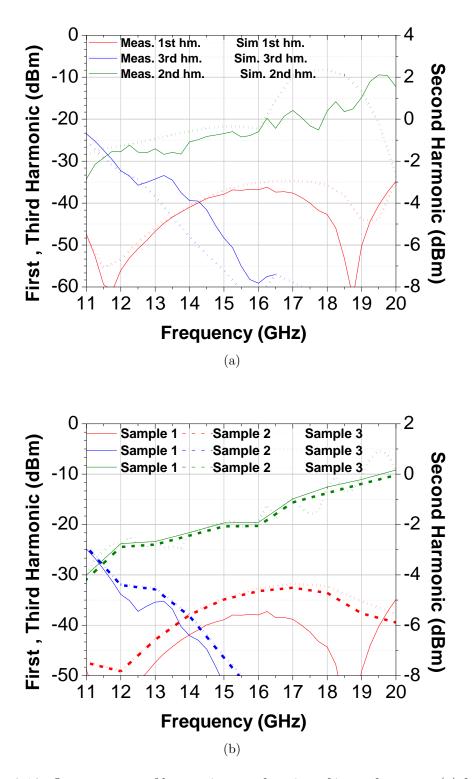

| 6.13 | Output power of harmonics as a function of input frequency (a) for 5                                             |     |

|      | dBm input, measured (solid), simulated (dotted), (b) for 4 dBm input,                                            |     |

|      | measured results for three dice.                                                                                 | 156 |

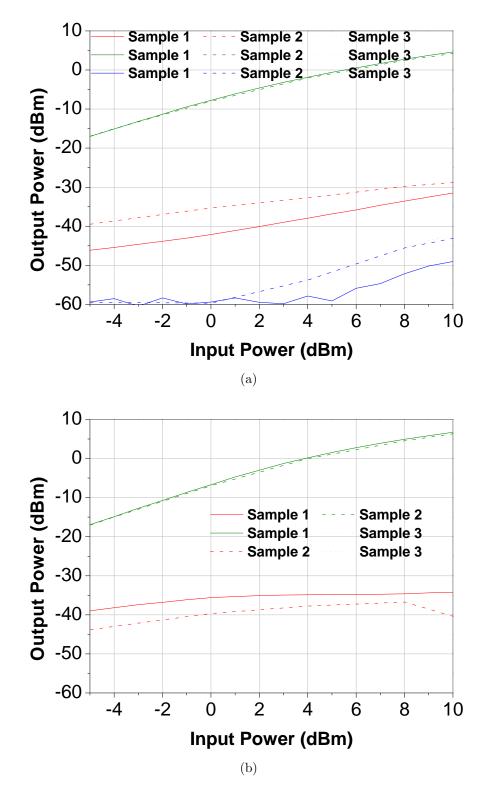

| 6.14 | Output power of harmonics as a function of input power sweep from -5                                             |     |

|      | dBm to 10 dBm for 12 GHz input across three samples; fundamental                                                 |     |

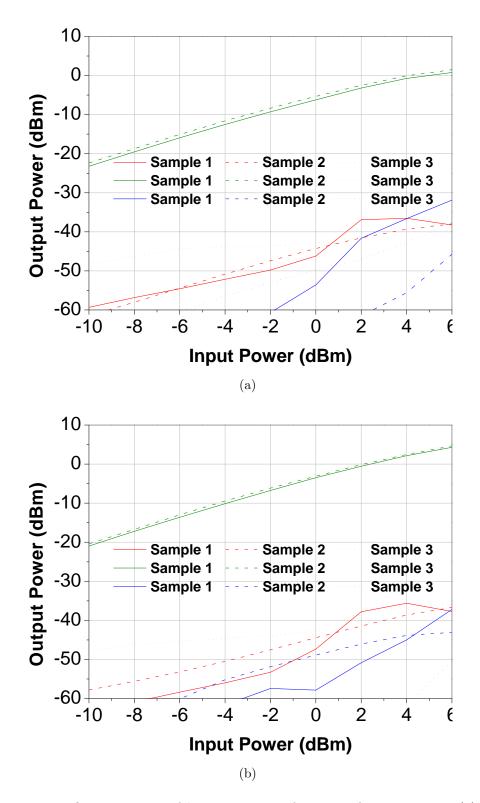

|      | (red line), second harmonic (green line)and third harmonic (blue line).                                          | 158 |

| 6.15 | Output power of harmonics as a function of input power sweep from -5                                             |     |

|      | dBm to 10 dBm across three samples: (a) for 16 GHz input, (b) for 20 $$                                          |     |

|      | GHz input; fundamental (red line), second harmonic (green line) and                                              |     |

|      | third harmonic (blue line)                                                                                       | 159 |

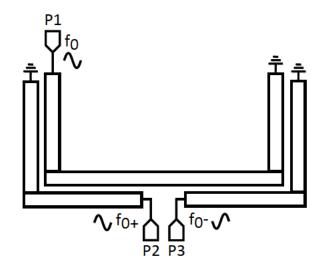

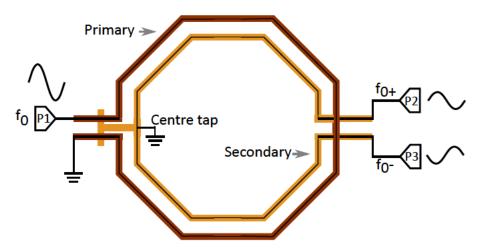

| 7.1  | Schematic representation of transformer balun implemented in the PP10-                                           |     |

|      | 10 GaAs pHEMT process                                                                                            | 165 |

| 7.2  | Schematic representation of transformer balun implemented in the SG13S                                           |     |

|      | SiGe HBT process.                                                                                                | 166 |

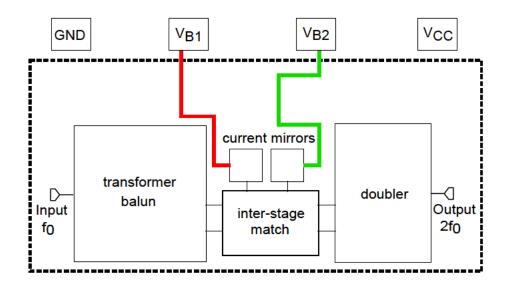

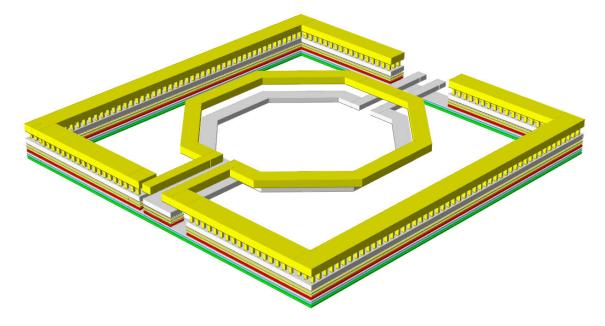

| Representation of the two bias lines (red and green) in the layout of the   |

|-----------------------------------------------------------------------------|

| frequency doubler in the SG13S SiGe HBT process                             |

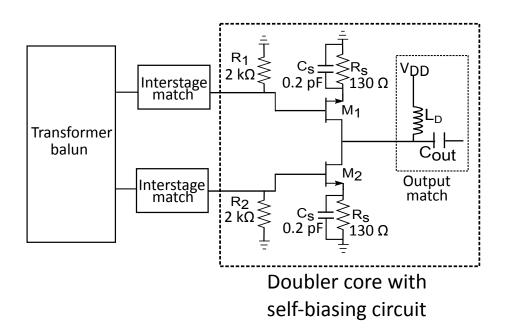

| Schematic of the self-biasing circuit of the frequency doubler in the       |

| PP10-10 GaAs pHEMT process                                                  |

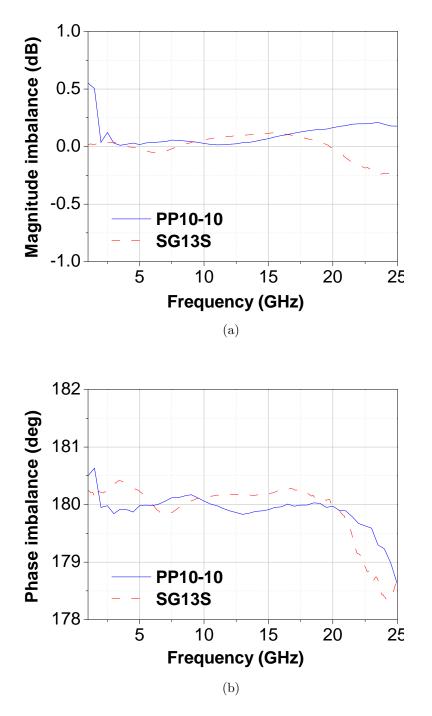

| Comparison of imbalances of the transformer baluns in the SG13S SiGe $$     |

| HBT and the PP10-10 GaAs pHEMT processes: (a) Magnitude imbal-              |

| ance, (b) Phase imbalance                                                   |

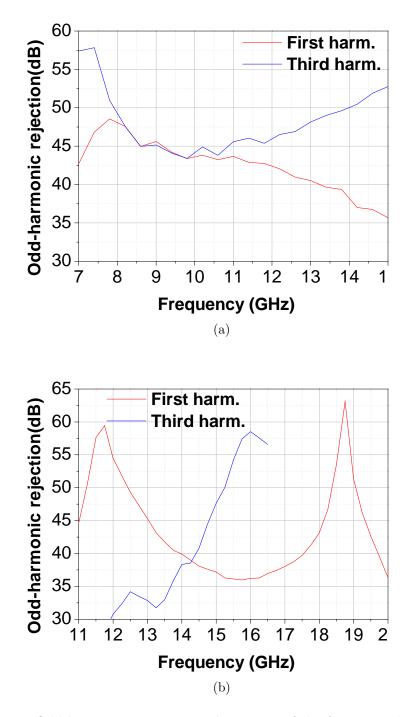

| Odd-harmonic rejection at the output of the frequency doubler for, (a)      |

| the SG13S SiGe HBT and (b) the PP10-10 GaAs pHEMT processes $175$           |

| Schematic representation of the transformer balun for an E-band doubler.177 |

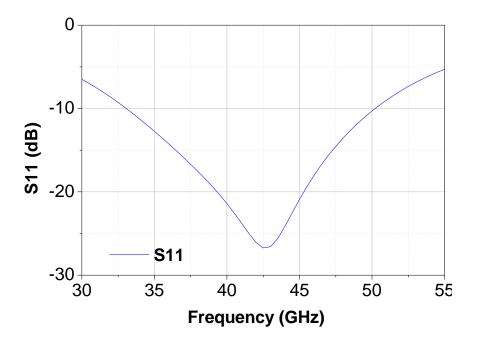

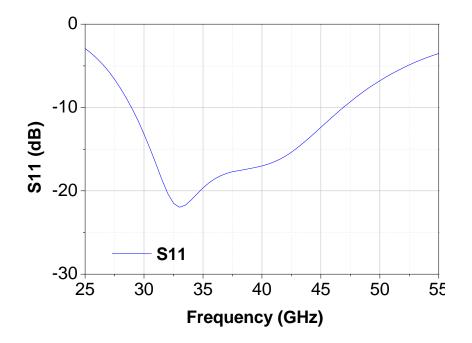

| Simulated $S_{11}$ of the transformer balun                                 |

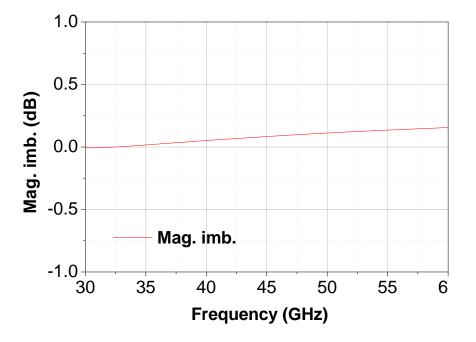

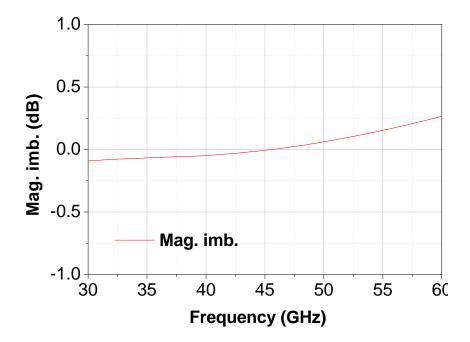

| Simulated magnitude imbalance of the transformer balun                      |

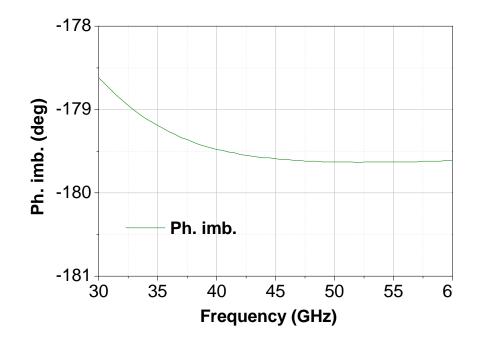

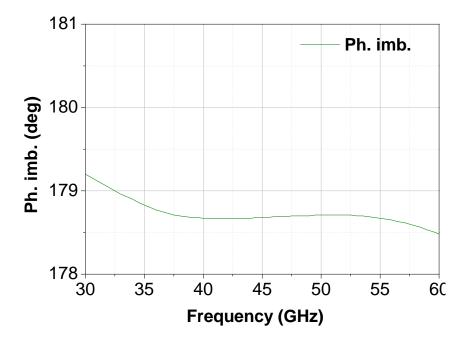

| Simulated phase imbalance of the transformer balun                          |

| Schematic representation of the transformer balun for an E-band doubler.180 |

| Simulated $S_{11}$ of the transformer balun                                 |

| Simulated magnitude imbalance of the transformer balun                      |

| Simulated phase imbalance of the transformer balun                          |

| Energy-band diagram of a SiGe HBT (solid line) with respect to a silicon    |

| BJT (dotted line)                                                           |

| Structure of a HEMT                                                         |

| Energy band diagram of a HEMT                                               |

| Energy-band diagram of a PHEMT                                              |

| Photographs of fabricated wafers (a)SG13S SiGe HBT process, (b) PP10-       |

| 10 GaAs pHEMT process                                                       |

|                                                                             |

## List of Tables

| 1.1 | Summary of key physical properties of silicon and GaAs 6                    |

|-----|-----------------------------------------------------------------------------|

| 1.2 | Summary of pHEMT parameters from three different foundries 11               |

| 1.3 | Summary of key physical properties of SiGe HBTs available from differ-      |

|     | ent companies in the European Dot Five project                              |

| 2.1 | Summary of HBT parameters of IHP SG13S process                              |

| 2.2 | Summary of pHEMT parameters of WIN Semiconductor's PP10-10 process 34       |

| 4.1 | Summary of key physical properties of an active and a passive balun. $.$ 84 |

| 4.2 | Performance summary of the designed transformer balun and compar-           |

|     | isons with other state-of-the-art designs                                   |

| 4.3 | Performance summary of the balun in PP10-10 compared to the other           |

|     | state-of-the art designs                                                    |

| 4.4 | Comparison of the performance of the baluns implemented in the PP10-        |

|     | 10 GaAS pHEMT and the SG13S SiGe HBT process                                |

| 5.1 | Design specification for the frequency doubler                              |

| 5.2 | Performance summary of the designed frequency doubler and compar-           |

|     | isons with other state-of-the-art designs                                   |

| 6.1 | Design specification for the K-Ka band PP10-10 frequency doubler $142$      |

| 6.2 | Performance summary of the designed frequency doubler and compar-           |

|     | isons with other state-of-the-art designs                                   |

| 7.1 | Comparison of the performance of the frequency doublers implemented |     |

|-----|---------------------------------------------------------------------|-----|

|     | in the PP10-10 GaAS pHEMT and the SG13S SiGe HBT process            | 172 |

| B.1 | Summary of the maximum current densities in the metal layers in the |     |

|     | SG13S process                                                       | 208 |

| B.2 | Summary of the maximum current densities in the metal layers in the |     |

|     | SG13S process                                                       | 208 |

| B.3 | Summary of the maximum current densities in the metal layers in the |     |

|     | PP10-10 process                                                     | 209 |

| B.4 | Summary of the maximum current densities in the metal layers in the |     |

|     | PP10-10 process                                                     | 209 |

# **1** Introduction

Since the invention of bipolar junction transistors in 1947 by John Bardeen, Walter Brattain and William Shockley (Fig. 1.1), semiconductor electronics has evolved at a rapid pace. The device dimensions have been reduced, enabling integration of a large number of transistors on a single silicon chip, paving the way for silicon VLSI (very-large-scale integration). Besides silicon VLSI, RF electronics emerged as the other prominent field of electronics in the 1980s [1]. The introduction of mobile phones and the development of wireless communication systems created a large impact on human society. RF transistors, which have become steadily faster, form the backbone of modern communication systems. Fig. 1.2 shows the evolution of RF transistors over the years [1].

The first real mass market for RF semiconductors was created with the advent of

FIGURE 1.1: Inventors of transistors at Bell Laboratories 1947 [AT&T archive].

mobile phones. Since then the RF semiconductor industry has ridden a wave of evolution which has made it possible to realise today's transistors that can operate in the microwave and millimetre-wave and even the terahertz range [2]. The development of high-frequency transistors can be attributed, not only to transistors of smaller dimensions, but also to the exploration of a wide variety of semiconductor materials (Silicon (Si), Silicon Germanium (SiGe), Gallium Arsenide (GaAs), Indium Phosphide (InP) etc.) and different types of transistors (Bipolar junction transistors (BJTs), Heterojunction bipolar transistors (HBTs), Metal-oxide-semiconductor field-effect transistors (MOSFETs), Metal-semiconductor field-effect transistors (MESFETs), High-electronmobility transistors (HEMTs) etc.).

#### 1.1 Status of semiconductor market

GaAs technology has been paramount in providing high-frequency performance, with high reliability at a reasonable cost for high-volume applications. With the advent

FIGURE 1.2: (a) History of development of RF transistors, (b) Plot of  $f_T$  and  $f_{max}$  of RF transistors over the years 1960 to 2000.

of the IoT (Internet of Things) and 5G systems, the semiconductor industry will be revolutionised. According to the latest Strategy Analytics forecast, more than 33 billion devices are expected to be connected to the Internet by 2020 [3].

The system complexity of communication systems is likely to continue to increase by orders of magnitude to provide increased user data rates and capacity. Due to these requirements, other technologies are in the process of capturing market share from GaAs. One such example is the mobile handset switch in which Silicon-on-Insulator (SoI) technology has replaced GaAs devices [3]. Silicon can provide highvolume digital, analogue and mixed-signal (AMS) integration, with low power and low cost. SiGe BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technologies equipped with high-speed HBTs and CMOS (Complementary Metal Oxide Semiconductor) with high integration capability will continue to grow in the field of microwave and millimetre-wave applications and pose a threat to at least some, if not all, GaAs-based applications.

# **1.2** GaAs and silicon technologies

The high-frequency performance of different devices is continually improving as advances in device technologies are made. It is also implied by the increase in cut-off frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  (details in Section 1.2.3) for different devices over the years. As the semiconductor industry offers various transistors in different materials with a variety of capabilities, the selection of a particular technology is made more difficult for the circuit designer. A complex system, like a typical transceiver for wireless communication system, consists of different building blocks such as amplifiers, mixers, oscillators, filters, switches, modulators and demodulators. A simplified block diagram of a wireless transceiver is shown in Fig. 1.3. Each of these building blocks has different requirements.

FIGURE 1.3: Simplified block diagram of a wireless communication transceiver.

In general for microwave and millimetre-wave designs, devices with higher  $f_T$  and  $f_{max}$  are necessary, but the choice of a particular device is not only limited to its higher  $f_T$  and  $f_{max}$ . For a specific application, many key parameters such as frequency of operation, linearity, current density, output power, supply voltage, gain, noise figure, power consumption play an important role. The level of integration supported by a particular process and the cost of manufacturing are also deciding factors for a

particular application.

A particular process is often selected based on the  $f_T$  and  $f_{max}$  of the devices, which decide the high-frequency performance of the circuit. In a complex system-level design such as a wireless transmitter or receiver, the overall linearity of the system is affected by the non-idealities from the active circuits. In other words, it is important to assess the overall linearity that could be achieved from a particular process. In this dissertation, it is proposed that the behaviour of a non-linear circuit can be studied and the non-idealities in a non-linear circuit can be investigated that limit the overall performance of a system.

Therefore, the status of the devices in different processes for microwave and millimetrewave applications are reviewed.

## 1.2.1 Overview

The increasing demand for wireless communication systems has pushed research to higher frequencies, towards millimetre-wave applications. Traditional Monolithic Microwave Integrated Circuits (MMICs) using GaAs technology have been the stalwart of the microwave industry over the last three decades. Group III/V technologies, such as GaAs, have outstanding properties, both a low-loss (passive) substrate and a highfrequency (active) transistor technology. They offer high electron mobility and a high band gap, and fabrication of complex layer structures by epitaxial growth to support millimetre-wave circuits [4]. Due to the high band gap, the breakdown voltage is higher. But GaAs material is expensive and fragile, and the fabrication process is less repeatable. GaAs wafer breakage rates of as high as 18% were common previously, due to the brittleness of wafers 5. Microcracks on the backside of the wafer and chips around the edges of the wafer caused a significant drop in the wafer strength. Micro-scratches caused unintentionally, and edge chips (caused due to collisions of wafers with metal cassettes and quartz boats, alignment pins on equipment or accidental handling errors) lead to wafer breakage, thereby reducing the yield [5]. Some improvements have been made recently by some companies [5] but they are still limited to a small wafer size.

On the other hand, silicon is known to be a robust material [4] that is widely

| induction and the properties of smeon and the |                       |                    |

|-----------------------------------------------|-----------------------|--------------------|

| Property                                      | Si                    | GaAs               |

| Energy gap (eV)                               | 1.12                  | 1.424              |

| Dielectric constant                           | 11.9                  | 13.1               |

| Electric breakdown field (kV/cm)              | 300                   | 400                |

| Electron drift mobility $(cm^2/V-s)$          | 1500                  | 8500               |

| Intrinsic carrier concentration $(cm^{-3})$   | $1.45 \times 10^{10}$ | $1.79 \times 10^6$ |

| Thermal conductivity (W/cm-K)                 | 1.5                   | 0.46               |

TABLE 1.1: Summary of key physical properties of silicon and GaAs

available and inexpensive. The thermal conductivity of silicon is three times as high as for GaAs, which is advantageous for power-dissipating devices [6]. The abundance of silicon and its inherent mechanical strength allow the growth of large defect-free wafers. This facilitates a tightly-controlled fabrication process compared to GaAs [7– 9]. The silicon-based devices are also suitable for digital applications. Therefore, digital and analogue circuits can be integrated on the same silicon wafer, which facilitates a complete system solution.

But silicon-based RF and microwave integrated circuits are typically associated with a higher loss for passive designs and lower-frequency operation for active circuits. As the electron mobility in silicon is approximately one-fifth the electron mobility in GaAs [6], silicon-based devices are more limited in high-frequency operation. However, the speed of silicon-based devices can be improved by shrinking the size of the transistors, as this reduces the transit time of the electrons. This comes with a price, namely short-channel effects, as the devices are decreased in length. If the channel length of the device is decreased, it causes collisions among the carriers and reduces the velocity of the carriers, which gives rise to a saturation velocity. The lower electron mobility of silicon restricts the use of silicon-based devices for high-frequency applications. The less reliable and expensive group III-V processes, such as GaAs, became the natural choice of option for high-frequency high-performance applications. Therefore, there is a desire to improve the performance of silicon-based devices to achieve comparable performance to their GaAs counterparts, while maintaining the benefits of high yield and low cost of manufacturing. Some of the key physical properties of silicon and GaAs are listed in Table 1.1.

SiGe takes advantage of the silicon wafers while enabling the benefits of a heterojunction (details in Section 1.2.2). Recent advancements in SiGe processes have made it possible to design circuits at RF and microwave frequencies with relatively good performance, at a lower cost than with GaAs. Moreover, for millimetre-wave and sub-millimetre-wave applications, it is beneficial to integrate the passive and active circuits on the same substrate, to provide a System-on-chip solution which could be implemented in SiGe technology [10]. Also, digital and analogue circuits can be integrated on the same die, as they follow the same manufacturing process as silicon-based devices. The SiGe process has the potential to incorporate the benefits of silicon device technology, such as high yield and low fabrication cost, into the high-frequency world [10].

## **1.2.2** Development of heterostructures

Although the speed of transistors can be and has been improved by shrinking the device dimensions (gate length in FETs and base width in BJTs) for RF applications, implementation of heterostructures or "bandgap engineering" after 1980 pushed the limit of high-frequency operation [1]. The realisation of HBTs and HEMTs played a significant role in improving the high-frequency performance of high-speed devices.

A heterostructure consists of at least two different semiconductor materials with different bandgaps, grown epitaxially one on top of the other. The concept of the heterostructure is used in an HBT. The important part in the HBT is the emitterbase heterojunction. Typically, the bandgap of the emitter is larger than that of the base [1]. Due to the difference in the bandgap, the electrons travelling from the emitter to the base encounter a small energy barrier. In a SiGe HBT, germanium is selectively doped into the base of the silicon bipolar transistor. A graded germanium doping profile can be used in the base for bandgap engineering. This results in an accelerating field, thereby reducing the base transit time, which also helps to increase the transit frequency. The concept of an HBT is not new; it was conceived by Shockley in 1948 [11]. Later, in 1957, Kroemer formulated an HBT theory [12]. At that time the state of development of fabricating high-quality heterostructures posed a hindrance to realising successful HBTs. Hence HBTs could not be fabricated until the 1980s, with the advent of molecular-beam epitaxy (MBE) [13].

The FET version of a heterostructure device is the HEMT. An HEMT can be constructed, for example, by exploiting an AlGaAs-GaAs heterostructure. As the bandgap energy for  $Al_xGa_{1-x}As$  is larger than for GaAs, the energy level of the conduction band  $E_C$  of  $Al_xGa_{1-x}As$  is higher than that of GaAs. Therefore the electrons flow from the  $E_C$  of  $Al_xGa_{1-x}As$  to the  $E_C$  of GaAs by diffusion. These electrons are trapped at the heterointerface of AlGaAs-GaAs. A triangular potential well (quantum well) is formed on the undoped GaAs buffer layer. A two-dimensional electron-gas (2-DEG) sheet charge is developed on the undoped GaAs layer at the AlGaAs-GaAs interface, which creates a conducting channel for the HEMT devices. In the late 1970s at Bell Laboratories, intensive research was carried out to characterise a sequence of thin layers of GaAs and AlGaAs layers, called superlattices [1]. As this heterostructure showed higher mobility than bulk GaAs or AlGaAs, different research groups worked to utilise GaAs-AlGaAs heterostructures with enhanced mobilities, to develop faster FETs. The first device of this kind, known as an HEMT, was reported by Takashi Mimura from Fujitsu [14]. Later a pseudomorphic HEMT (pHEMT) on a GaAs substrate was developed using an AlGaAs/InGaAs/GaAs heterostructure [15].

## **1.2.3** Transit frequency and maximum frequency of oscillation

The high-frequency performance of transistors can be assessed by two important parameters which act as rough figures of merit for high-frequency circuit and system applications: cut-off frequency  $(f_T)$  and maximum oscillation frequency  $(f_{max})$  [7].

The frequency,  $f_T$ , at which the current gain drops to unity is called the cut-off frequency, making the device ineffective at higher frequencies than  $f_T$  [16].  $f_T$  can be defined for BJTs and HBTs by the following equation [7, 17, 18]

$$f_T = \frac{1}{2\pi} \left[ \frac{1}{g_m} \left( C_{EB} + C_{CB} \right) + \tau_B + \tau_C + \tau_E \right]^{-1}$$

(1.1)

where,  $g_m$  is the transconductance,  $C_{EB}$  and  $C_{CB}$  are the emitter-to-base and collectorto-base capacitances respectively,  $\tau_B$ ,  $\tau_C$  and  $\tau_E$  are the transit times in the base, collector and emitter respectively.

The maximum oscillation frequency  $f_{max}$  is the frequency at which the power gain of the transistor drops to unity. It can be defined for BJTs and HBTs by [7, 17, 18]

$$f_{max} = \sqrt{\frac{f_T}{8\pi \left(C_{CB}R_B\right)}} \tag{1.2}$$

Similar formulations for  $f_T$  and  $f_{max}$  can be derived for FET structures by appropriate substitution of drain, gate, source for collector, base and emitter respectively, as follows [19]:

$$f_T = \frac{1}{2\pi} \left[ \frac{1}{g_m} \left( C_{gs} + C_{gd} \right) + C_{gd} \left( R_S + R_D \right) \right]^{-1}$$

(1.3)

$$f_{max} = \frac{1}{2} \frac{f_T}{\sqrt{2\pi f_T C_{gd} \left(R_g + R_S\right) + \frac{R_g + R_S}{r_o}}}$$

(1.4)

where,  $g_m$  is the transconductance,  $C_{gs}$  and  $C_{gd}$  are the gate-to-source and gate-todrain capacitances respectively.  $R_S$ ,  $R_D$  and  $R_g$  are the resistances in the source, drain and gate respectively.

## 1.2.4 Performance trend

The performance trend of GaAs pHEMTs and SiGe HBTs over the years is discussed in this section.

#### GaAs pHEMT

The cut-off-frequency target for a GaAs pHEMT over time is plotted in Fig. 1.4(a) [20]. Significant increments in the cut-off frequency for a process occur in steps. For GaAs pHEMTs no significant improvement has been introduced in the last few years. For example in [21], a 0.1  $\mu$ m GaAs pHEMT with more than 130 GHz  $f_T$  and 180 GHz

FIGURE 1.4: (a) ITRS  $f_T$  target for GaAs pHEMT. (b) Reported cut-off frequency  $(f_T)$  versus gate length for GaAs pHEMT.

FIGURE 1.5: The plot of breakdown voltage vs  $f_T$  of GaAs pHEMTs available from WIN Semiconductors.

| TABLE 1.2: Summary of premi parameters from three different foundries |                |               |              |