# DIGITAL IMAGE PROCESSING BASED ON THE RESIDUE NUMBER SYSTEM

By

Azadeh Safari

A thesis submitted to Macquarie University for the degree of Doctor of Philosophy Department of Engineering, Faculty of science October 2014

© Azadeh Safari, 2014.

Typeset in  $\mathbb{A}T_{\mathbb{E}} X 2_{\mathcal{E}}$ .

Except where acknowledged in the customary manner, the material presented in this thesis is, to the best of my knowledge, original and has not been submitted in whole or part for a degree in any university.

Azadeh Safari

#### Dedicated to

My beloved husband, Peyman, whose endless love and support made PhD a significant journey,

and

My parents, whose unconditional love and encouragement allowed me to start and complete this journey.

## Acknowledgements

I would like to express my sincere gratitude and heartfelt appreciation to my supervisor, Dr Yinan Kong for his excellent guidance and continuous encouragement throughout my research. I particularly appreciate his patience and motivation that helped me to learn a lot, and challenge myself to do the best job that I could do.

I also would like to extend my thanks to A/Prof. Sam Reisenfeld, my co-supervisor, for his excellent support. I am thankful to Niras C.V., James Nugent, Fujimi Bentley, Fateme Ghasemi, and Davar Kheirandish for being great collaborators, and for helpful ideas.

I would like to thank Mr Adrian Ng and Synopsys Customer Support for providing outstanding support and frequent meetings to help us solve technical problems with Synopsys tools.

I also thank Professor Danijela Cabric of the Electrical Engineering Department of the University of California, Los Angeles, and Professor Philip Leong of the University of Sydney for inviting me to visit their research laboratories to collaborate and meet with their graduate students and faculty members.

I am grateful to Dr Keith Imrie for valuable advice and useful comments that improved the quality of this thesis. I am also thankful to the admirable staff in the Department of Engineering for their wonderful support.

I wish to acknowledge Macquarie University for awarding me the International Macquarie University Research Excellence Scholarship (iMQRES), and providing financial support to attend national and international conferences during this project.

## List of Publications

Publications related to the field of this thesis for which the author is the primary author are as follows.

- Azadeh Safari and Yinan Kong. Simple, Fast and Synchronous Hybrid Scaling Scheme for the 8-bit Moduli Set, Journal of Emerging Trends in Computing and Information Sciences, Vol. 3, No. 6, June 2012.

- Azadeh Safari and Yinan Kong. Four Tap Daubechies filter banks based on RNS, International Symposium on Communications and Information Technologies (ISCIT) 2012, pp. 957-960, 2-5 Oct., Gold Coast, Australia.

- Azadeh Safari and Yinan Kong. *The application of lifting in Digital Image processing*, Advances in Mechanical and Electronic Engineering, Lecture Notes in Electrical Engineering, Volume 178, 2013, pp. 449-453, Springer, 2013.

- Azadeh Safari, Niras C V, and Yinan Kong. VLSI architecture of multiplierless DWT image processor, IEEE TENCON Spring 2013 Conference in Sydney Australia, pp. 280-284, 17-19 April 2013.

- Azadeh Safari, James Nugent, and Yinan Kong. Novel Implementation of Full Adder Based Scaling in Residue Number Systems, IEEE 56<sup>th</sup> International Midwest Symposium on Circuits and Systems (MWSCAS2013), The Ohio Union at the Ohio State University, Columbus Ohio, August 4-7, 2013.

- Azadeh Safari and Yinan Kong. Performance comparison of orthogonal and biorthogonal wavelets using technology libraries, The 13<sup>th</sup> International Symposium on Communications and Information Technologies, IEEE, Samui Island, Thailand, September 4-6, 2013.

- Azadeh Safari, Fujimi Bentley, and Yinan Kong. Operational Capability and Suitability of Image Compression Methods for Different Applications, CCECE

2014, Ontario, Canada 4-7 May, pp.875-880, 2014.

• Azadeh Safari, and Yinan Kong. Power-Performance Enhancement of RNS-Based DWT Image Processor Using Multiple Voltage Domains, In preparation.

Publications related to the field of this thesis for which the author is the second author are as follows.

- Davar Kheirandish, Azadeh Safari, and Yinan Kong. Using one hot residue number system (OHRNS) for digital image processing, The 16<sup>th</sup> international symposium on artificial intelligence and signal processing (AISP 2012), 2-3 May 2012, Shiraz University, Shiraz, Iran.

- Niras C V, Azadeh Safari, and Yinan Kong. Overlapped block processing VLSI architecture for separable 2D filters, National Conference on Emerging Trends in VLSI and ES, January 2013.

- Davar Kheirandish, Azadeh Safari, and Yinan Kong. A Novel Approach for Improving Error Detection and Correction in WSN, CCECE 2014, Ontario, Canada, 4-7 May, pp. 370-373, 2014.

- Yinan Kong, Azadeh Safari, Niras C.V. A low-cost architecture for DWT filter banks in RNS applications, Abstract accepted in International Symposium on Integrated Circuits (ISIC 2014), Singapore, 10-12 December, 2014.

- Fatemeh Ghasemi, Azadeh Safari, Saied Sorouri, Amir Sabbagh Molahosseini, Yinan Kong, An Efficient RNS Scaler for the Four-Moduli Set {2<sup>n</sup> - 1, 2<sup>2n</sup>, 2<sup>n</sup> + 1, 2<sup>2n</sup> + 1}, Submitted to Very Large Scale Integration (VLSI) Systems, IEEE Transactions on.

## Abstract

This thesis presents the design, optimisation and physical implementation of a twodimensional (2D) discrete wavelet transform (DWT) image processor using the residue number system (RNS), and examines it against an initial processor designed based on existing binary modules. The original contributions of the proposed design include a low-complexity hardware architecture of the RNS-based filter banks, optimised transposition units, and exploitation of the multi-voltage scheme to reduce the power consumption. Modular adders and multipliers of the RNS-based filter banks are simplified to save on hardware complexity, while modular arithmetic and 6-bit dyadic-fraction filter coefficients are applied to improve the system performance. The proposed design is synthesised with the Synopsys 90 nm Generic Library (SAED90nmEDK) using the Synopsys synthesis and implementation tools. The synthesis results show that the proposed RNS-based processor is 23% faster than the initial processor. Another noteworthy result is that the total area of the RNS-based processor is less than the total area in the initial binary processor. It confirms that using the proposed architecture for RNS-based filter banks has saved on the hardware complexity and the system area requirement. The proposed RNS-based processor is implemented using the multivoltage (MV) low power design (LPD) scheme to improve the power performance of the proposed processor. The power synthesis results show that using the multi-voltage scheme reduces the total power of the proposed RNS-based design by up to 50%. The proposed residue arithmetic units are explained in details to illustrate the novelty of the proposed design.

\_\_\_\_\_

## Contents

| A        | cknov                 | wledge        | ments                                                       | v     |

|----------|-----------------------|---------------|-------------------------------------------------------------|-------|

| Li       | st of                 | Publi         | cations                                                     | vii   |

| A        | bstra                 | $\mathbf{ct}$ |                                                             | ix    |

| Li       | st of                 | Figur         | es                                                          | xix   |

| Li       | st of                 | Table         | 5                                                           | xxiii |

| 1        | $\operatorname{Intr}$ | oducti        | on                                                          | 1     |

|          | 1.1                   | Existi        | ng Literature                                               | 2     |

|          | 1.2                   | Motiv         | ation for This Research                                     | 5     |

|          | 1.3                   | Resear        | rch Objectives                                              | 6     |

|          | 1.4                   | Thesis        | Outline                                                     | 6     |

|          | 1.5                   | Tools         |                                                             | 8     |

| <b>2</b> | Rev                   | iew of        | Image-Compression Algorithms and Schemes                    | 11    |

|          | 2.1                   | Image         | -Compression Schemes                                        | 12    |

|          | 2.2                   | Comm          | on Image-Compression Algorithms                             | 14    |

|          |                       | 2.2.1         | Run-Length Encoding                                         | 14    |

|          |                       | 2.2.2         | Entropy Coding                                              | 16    |

|          |                       | 2.2.3         | Discrete Cosine Transform                                   | 16    |

|          |                       | 2.2.4         | Discrete Wavelet Transform                                  | 17    |

|          | 2.3                   | Perfor        | mance Comparison and Applications of Common Compression Al- |       |

|          |                       | gorith        | ms                                                          | 17    |

|          |                       | 2.3.1         | Performance of RLE Algorithm on Test Images                 | 18    |

|          |                       | 2.3.2         | Performance of Entropy Coding on Test Images                | 18    |

|          |                       | 2.3.3         | Performance of DCT Algorithm on Test Images                 | 19    |

|          |                       |               |                                                             |       |

|   |      | 2.3.4   | Performance of DWT Algorithm on Test Images          | 20 |

|---|------|---------|------------------------------------------------------|----|

|   | 2.4  | Overa   | ll Performance of Selected Algorithms                | 21 |

|   |      | 2.4.1   | Performance of RLE Over DCT Coefficients             | 21 |

|   |      | 2.4.2   | Performance of Huffman Coding Over DWT Coefficients  | 22 |

|   | 2.5  | Discus  | ssion of Simulation Results                          | 22 |

|   | 2.6  | Convo   | olution vs. Lifting                                  | 25 |

|   |      | 2.6.1   | Lifting-Based DWT Image Compression                  | 26 |

|   | 2.7  | Chapt   | er Summary                                           | 29 |

| 3 | Disc | crete V | Wavelet Transform for Image-Processing Applications  | 31 |

|   | 3.1  | Discre  | ete Wavelet Transform                                | 32 |

|   | 3.2  | Ortho   | gonal and Bi-Orthogonal Wavelets                     | 35 |

|   | 3.3  | Ortho   | gonal DWT                                            | 36 |

|   |      | 3.3.1   | Haar Wavelet Transform                               | 36 |

|   |      | 3.3.2   | Daubechies Wavelet Transform                         | 37 |

|   | 3.4  | Bi-Ort  | thogonal DWT                                         | 39 |

|   |      | 3.4.1   | Cohen-Daubechies-Feauveau (CDF97) Wavelet            | 40 |

|   |      | 3.4.2   | LeGall $(b, c)$ Wavelet $\ldots$                     | 40 |

|   | 3.5  | Perfor  | mance Comparison of Wavelets                         | 41 |

|   | 3.6  | Synthe  | esising Wavelets Using Design Compiler               | 41 |

|   | 3.7  | Chapt   | er Summary                                           | 45 |

| 4 | The  | Resid   | lue Number System                                    | 47 |

|   | 4.1  | Algeb   | raic Operations in the RNS                           | 48 |

|   | 4.2  | Forwa   | rd and Reverse Conversions                           | 49 |

|   |      | 4.2.1   | The Chinese Remainder Theorem                        | 50 |

|   |      | 4.2.2   | Multiplicative Inverse for $(2^n - 1, 2^n, 2^n + 1)$ | 50 |

|   |      | 4.2.3   | Modified CRT                                         | 51 |

|   |      | 4.2.4   | Mixed-Radix Conversion                               | 52 |

|   | 4.3  | Modu    | li Set Selection and Bit-Efficiency Improvement      | 52 |

|   |      | 4.3.1   | Moduli Set Selection                                 | 52 |

|   |      | 4.3.2   | Moduli Set for Video and Image Processing            | 54 |

|   | 4.4  | Scalin  | g in the RNS                                         | 55 |

|   | 4.5  | Residu  | ue Number System Merged With Other Number Systems    | 55 |

|   |      | 4.5.1   | Polynomial Residue Number System                     | 55 |

|   |      | 4.5.2   | One-Hot Residue Number System                        | 56 |

|   | 4.6  | Chapt   | er Summary                                           | 57 |

| <b>5</b> | Sca | ling in    | the Residue Number System                                          | <b>59</b> |

|----------|-----|------------|--------------------------------------------------------------------|-----------|

|          | 5.1 | Previo     | ous Work                                                           | 60        |

|          | 5.2 | Mathe      | ematical Basis for Designing Scalers                               | 62        |

|          | 5.3 | Scalin     | g Scheme Based on Modular Reducers                                 | 64        |

|          |     | 5.3.1      | Modulo- $(2^n - 1)$ Reduction                                      | 66        |

|          |     | 5.3.2      | Modulo- $(2^n + 1)$ Reduction                                      | 66        |

|          |     | 5.3.3      | Optimised Modulo- $(2^n + 1)$ Reducer                              | 67        |

|          |     | 5.3.4      | Numerical Example                                                  | 67        |

|          |     | 5.3.5      | Synthesising the Proposed Modular-Reducer-Based Scaler $\ . \ .$ . | 68        |

|          |     | 5.3.6      | Comparison of the Synthesis Results of the Proposed Modular-       |           |

|          |     |            | Reducer-Based Scaler and a Full-Adder-Based Scaler $\ . \ . \ .$ . | 72        |

|          | 5.4 | Simpl      | e, Fast, Hybrid Scaling Scheme Using Full-Adders and LUTs          | 73        |

|          |     | 5.4.1      | Proposed Hybrid Scaler                                             | 74        |

|          |     | 5.4.2      | Error Analysis of Approximation                                    | 75        |

|          |     | 5.4.3      | Synthesis Results                                                  | 76        |

|          |     | 5.4.4      | Evaluation and Comparison                                          | 80        |

|          | 5.5 | -          | sing a Scaler for Four-Moduli Set                                  |           |

|          |     | $(2^{n} -$ | $1, 2^{2n}, 2^n + 1, 2^{2n} + 1)$                                  | 82        |

|          |     | 5.5.1      | Proposed Algorithm                                                 | 83        |

|          |     | 5.5.2      | Generating $y_1$                                                   | 88        |

|          |     | 5.5.3      | Generating $y_2$                                                   | 89        |

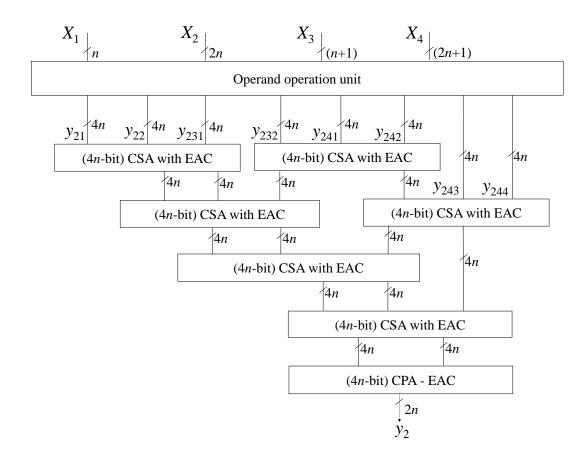

|          |     |            | 5.5.3.1 Generating $y_{21}$                                        | 90        |

|          |     |            | 5.5.3.2 Generating $y_{22}$                                        | 91        |

|          |     |            | 5.5.3.3 Generating $y_{23}$                                        | 92        |

|          |     |            | 5.5.3.4 Generating $y_{24}$                                        | 93        |

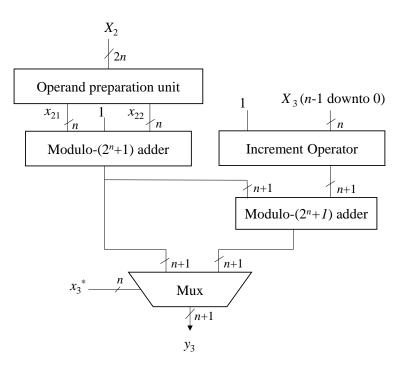

|          |     | 5.5.4      | Generating $y_3$                                                   | 95        |

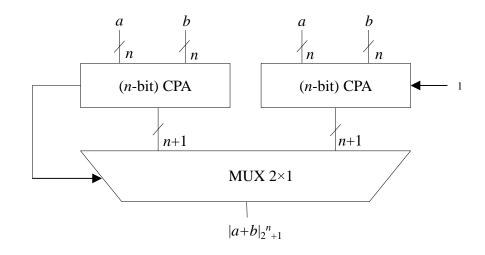

|          |     |            | 5.5.4.1 A New Modulo- $(2^n + 1)$ Adder $\ldots$                   | 97        |

|          |     | 5.5.5      | Generating $y_4$                                                   | 98        |

|          |     | 5.5.6      | Performance Evaluation                                             | 101       |

|          |     | 5.5.7      | Comparison of Design Compiler Synthesis Results for the Pro-       |           |

|          |     |            | posed Four-Moduli Scaler and the Chang Scaler                      | 102       |

|          |     | 5.5.8      | Design Summary                                                     | 105       |

|          | 5.6 | Chapt      | ter Summary                                                        | 106       |

| 6                                                               | Logic Design and FPGA Implementation of RNS-Based DWT Digital |         |                                                                                                           |      |  |

|-----------------------------------------------------------------|---------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------|------|--|

|                                                                 | Ima                                                           | ige Pro | ocessor                                                                                                   | 107  |  |

|                                                                 | 6.1                                                           | Hierar  | chy of the Proposed Image Processor                                                                       | 108  |  |

|                                                                 | 6.2                                                           | Logic   | Design of the Proposed Image Processor Using Xilinx Tools                                                 | 109  |  |

|                                                                 |                                                               | 6.2.1   | The RNS-Based Filter Banks                                                                                | 109  |  |

|                                                                 |                                                               |         | 6.2.1.1 Existing Design of RNS-Based Filter Banks                                                         | 109  |  |

|                                                                 |                                                               |         | 6.2.1.2 Proposed RNS-Based Filter Banks                                                                   | 112  |  |

|                                                                 |                                                               | 6.2.2   | Transposition Unit                                                                                        | 118  |  |

|                                                                 |                                                               |         | $6.2.2.1  {\rm VLSI \ Architecture \ of \ a \ Scalable \ Matrix \ Transposer} \ . \ .$                    | 118  |  |

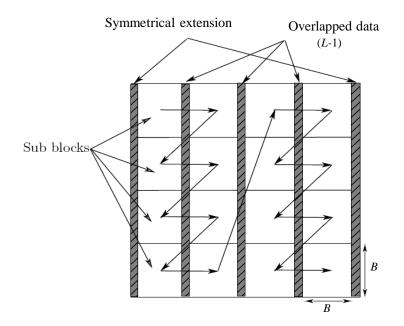

|                                                                 |                                                               |         | 6.2.2.2 Proposed Transposition Unit with Overlapped Sub-Block                                             | s123 |  |

|                                                                 |                                                               |         | 6.2.2.3 Modified Transposition Unit with Symmetric Extension                                              |      |  |

|                                                                 |                                                               |         | $(Extender)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                             | 124  |  |

|                                                                 |                                                               | 6.2.3   | Control Logic                                                                                             | 126  |  |

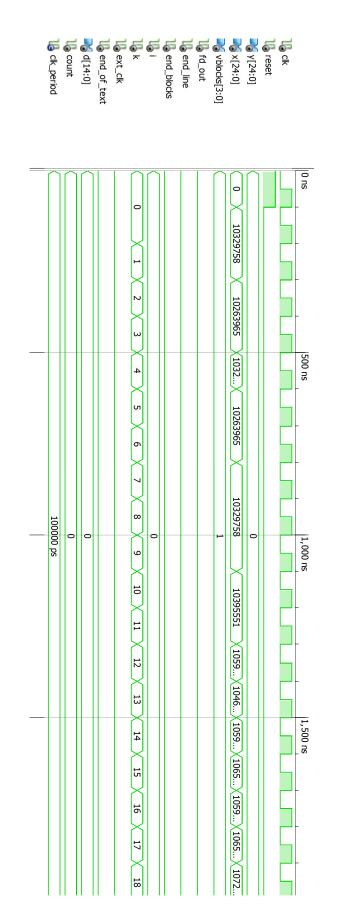

|                                                                 | 6.3                                                           | Simula  | tion and Functionality of the Proposed Processor                                                          | 127  |  |

|                                                                 | 6.4                                                           | Top-L   | evel and Hierarchy Synthesis Results                                                                      | 127  |  |

|                                                                 |                                                               | 6.4.1   | Synthesising the Modular Adders                                                                           | 130  |  |

|                                                                 |                                                               | 6.4.2   | Synthesising the Modular Multipliers                                                                      | 130  |  |

|                                                                 |                                                               | 6.4.3   | Synthesising the Modular Filter Banks                                                                     | 131  |  |

|                                                                 | 6.5                                                           | Initial | Binary Processor                                                                                          | 132  |  |

| 6.6 Performance Comparison of the Proposed RNS-Based Image Proc |                                                               |         |                                                                                                           |      |  |

|                                                                 |                                                               | with I  | Existing Designs                                                                                          | 132  |  |

|                                                                 |                                                               | 6.6.1   | Comparing Synthesis Results of Modular Scalable Transposer                                                |      |  |

|                                                                 |                                                               |         | and the Proposed Transposer (Extender) $\ . \ . \ . \ . \ .$ .                                            | 132  |  |

|                                                                 |                                                               | 6.6.2   | Comparison of the Initial and Proposed RNS-based CDF97 Filter                                             |      |  |

|                                                                 |                                                               |         | Banks Designed Using Existing and Proposed Modules $\ . \ . \ .$                                          | 133  |  |

|                                                                 |                                                               | 6.6.3   | Comparison of Initial and RNS-based Processors                                                            | 134  |  |

|                                                                 | 6.7                                                           | Comp    | arison of Initial and RNS-based Processors with Existing Designs                                          | 135  |  |

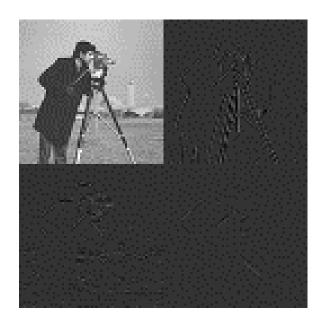

|                                                                 | 6.8                                                           | FPGA    | Implementation of Proposed RNS-Based Image Processor                                                      | 137  |  |

|                                                                 |                                                               | 6.8.1   | Translate                                                                                                 | 137  |  |

|                                                                 |                                                               | 6.8.2   | Map                                                                                                       | 137  |  |

|                                                                 |                                                               | 6.8.3   | Place and Route $\ldots$ | 138  |  |

|                                                                 | 6.9                                                           | Chapt   | er Summary                                                                                                | 138  |  |

| 7                                                               | $\mathbf{RT}$                                                 | L-to-G  | ate Synthesis                                                                                             | 141  |  |

|                                                                 | 7.1                                                           | Logic   | Synthesis                                                                                                 | 141  |  |

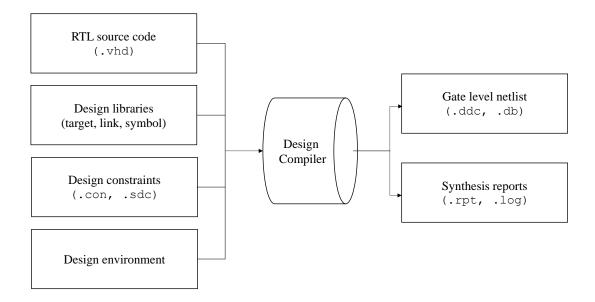

|                                                                 |                                                               | 7.1.1   | The RTL Source                                                                                            | 142  |  |

|   |     | 7.1.2          | Libraries $\ldots \ldots 142$                                                     |

|---|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

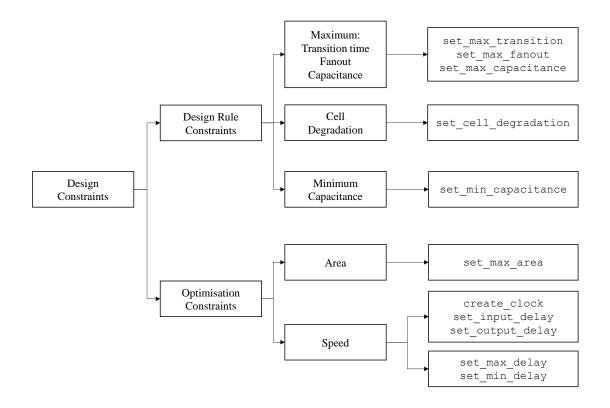

|   |     | 7.1.3          | Design Constraints                                                                                                                                                                  |

|   |     | 7.1.4          | Design Environment                                                                                                                                                                  |

|   |     |                | 7.1.4.1 Operating Conditions                                                                                                                                                        |

|   |     |                | 7.1.4.2 Wire-Load Model and Wire-Load Mode                                                                                                                                          |

|   |     |                | 7.1.4.3 Interface Characteristics                                                                                                                                                   |

|   |     |                | 7.1.4.4 Drive Characteristics of Input Ports and Driving Cell . $146$                                                                                                               |

|   |     |                | 7.1.4.5 Load on Input and Output Ports                                                                                                                                              |

|   |     |                | 7.1.4.6 Fanout_load on Output Ports $\ldots \ldots \ldots \ldots \ldots 147$                                                                                                        |

|   |     | 7.1.5          | Synthesis Reports                                                                                                                                                                   |

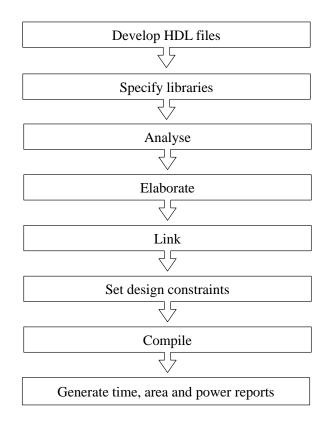

|   | 7.2 | Synth          | esis Flow $\ldots \ldots 148$                                                     |

|   |     | 7.2.1          | Read Design                                                                                                                                                                         |

|   |     | 7.2.2          | Compile Strategies                                                                                                                                                                  |

|   | 7.3 | Comp           | arison of Proposed RNS-based Image Processor with Initial Binary                                                                                                                    |

|   |     | Proces         | m ssor                                                                                                                                                                              |

|   | 7.4 | Optim          | nising Power Consumption of Proposed Image Processor $\ldots \ldots 156$                                                                                                            |

|   |     | 7.4.1          | Components of Power Dissipation                                                                                                                                                     |

|   |     | 7.4.2          | Leakage Power Sources                                                                                                                                                               |

|   |     | 7.4.3          | Low-Power Design Techniques                                                                                                                                                         |

|   |     | 7.4.4          | Impact of LPD Techniques on Standard Cell Libraries 161                                                                                                                             |

|   |     | 7.4.5          | Impact of LPD Techniques on Synthesis Flow 162                                                                                                                                      |

|   | 7.5 | Impac          | t of the Multi-Voltage LPD Technique on Quality of Results $162$                                                                                                                    |

|   | 7.6 | Prepa          | ring the Design for Power Analysis Using VCS $\ldots \ldots \ldots$ |

|   | 7.7 | Multi-         | Voltage Power Analysis Using PrimeTime PX and UPF Flow $\ . \ . \ 173$                                                                                                              |

|   | 7.8 | Chapt          | er Summary                                                                                                                                                                          |

| 8 | Dh- |                | mplementation Using Design Compiler Topographical Tech-                                                                                                                             |

| 0 | v   |                | ASIC Methodology 181                                                                                                                                                                |

|   | 8.1 | 00             | cal Synthesis Using IC Compiler                                                                                                                                                     |

|   | 8.2 | v              | cal Synthesis Flow $\dots \dots \dots$                                              |

|   | 0.2 | 8.2.1          | Library Data Preparation                                                                                                                                                            |

|   |     | 8.2.1          |                                                                                                                                                                                     |

|   |     | 8.2.2          | Floorplanning         184           Placement         185                                                                                                                           |

|   |     | 8.2.3          | Clock Tree Synthesis    186                                                                                                                                                         |

|   |     | 8.2.4<br>8.2.5 | Routing         189                                                                                                                                                                 |

|   |     | 8.2.5          | Design Verification                                                                                                                                                                 |

|   |     | 0.2.0          | Design vermeanon                                                                                                                                                                    |

|              |                | 8.2.7 Finishing and Saving the Results                                                                              | 190                  |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------------|----------------------|

|              | 8.3            | Comparison of the Proposed RNS-Based Image Processor with Dedi-                                                     |                      |

|              |                | cated Hardware Designs $\ldots \ldots \ldots$ | 193                  |

|              | 8.4            | Chapter Summary                                                                                                     | 196                  |

| 9            | The            | sis Conclusion and Recommendations for Future Work                                                                  | 197                  |

|              | 9.1            | Thesis Conclusion                                                                                                   | 197                  |

|              | 9.2            | Future Research Directions                                                                                          | 198                  |

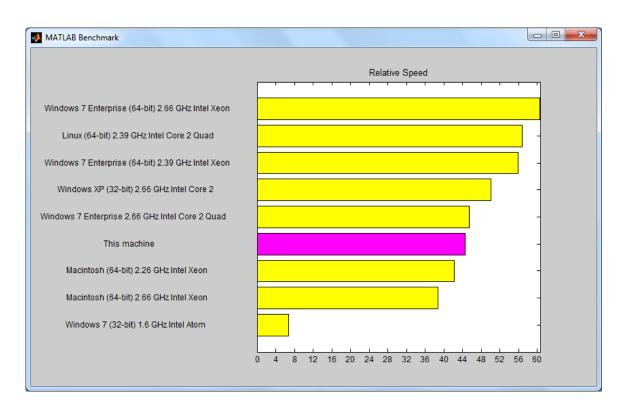

| $\mathbf{A}$ | Con            | nputer Specifications Used for Running MATLAB                                                                       | 201                  |

|              | A.1            | Computer Benchmark for Running MATLAB                                                                               | 201                  |

|              | A.2            | MATLAB Benchmark                                                                                                    | 202                  |

| в            | $\mathbf{Syn}$ | opsys Design Compiler Synthesis Results of Full-Adder-Based Sca                                                     | ler <mark>203</mark> |

| С            | Tcl            | Scripts for Synthesising Initial Binary and the Proposed RNS                                                        | -                    |

|              | base           | ed Image Processors Using Synopsys DC                                                                               | 209                  |

|              | C.1            | Synopsys DC Setup File-Setup.tcl                                                                                    | 209                  |

|              | C.2            | Synopsys DC Constraints File-Defaults.con                                                                           | 210                  |

| D            | Tcl            | Scripts for Multi-Voltage Synthesis of Initial Binary and the Pro                                                   | -                    |

|              | pos            | ed RNS-Based Image Processors Using Synopsys DC Topograph                                                           | -                    |

|              | ical           | Mode                                                                                                                | 211                  |

|              | D.1            | Synopsys DC Topographical Mode Setup File-Setup_topo.tcl $\ . \ . \ .$ .                                            | 211                  |

|              | D.2            | Multi-voltage Setting Tcl File for Topographical Mode Synthesis - Voltage.                                          | tcl212               |

|              | D.3            | UPF File for Compiling the Proposed RNS-based Image Processor Using                                                 |                      |

|              |                | Synopsys DC Topographical Mode-binary.upf                                                                           | 212                  |

| $\mathbf{E}$ | $\mathbf{Syn}$ | opsys VCS-MX Tcl Scripts for Simulation of the Proposed RNS                                                         | -                    |

|              | base           | ed Image Processor                                                                                                  | 215                  |

|              | E.1            | Synopsys DVE Setup File-Setup_DVE.tcl                                                                               | 215                  |

|              | E.2            | Tcl File Used to Generate VCD File                                                                                  | 216                  |

| $\mathbf{F}$ | Syn            | opsys PrimeTime PX Tcl Scripts for Multi-voltage Power Analy                                                        | -                    |

|              | sis o          | of the Proposed RNS-based Image Processor                                                                           | 217                  |

|              | F.1            | Tcl Script for PrimeTime PX Post Lay Power Analysis                                                                 | 217                  |

| $\mathbf{G}$ | Synopsys DC Report of Post Compile UPF of the Proposed RN            | S-         |

|--------------|----------------------------------------------------------------------|------------|

|              | based Image Processor                                                | <b>219</b> |

|              | G.1 Visual UPF - Post Compile UPF                                    | . 219      |

| н            | Synopsys IC Compiler Tcl Scripts for Physical Implementation of the  | ne         |

|              | Proposed RNS-based Image Processor                                   | 223        |

|              | H.1 Synopsys IC Compiler Setup File-Setup_icc.tcl                    | . 223      |

|              | H.2 Creat MilkyWay Library "RNS2D"                                   | . 224      |

|              | H.3 Set TLU+ Files                                                   | . 224      |

|              | H.4 Import the Design and Constraints File                           | . 224      |

|              | H.5 Initialise Floorplan                                             | . 224      |

|              | H.6 Set Power and Ground Nets and Pins                               | . 224      |

|              | H.7 Add Rectangular Power and Ground Rings                           | . 225      |

|              | H.8 Create Power Straps                                              | . 225      |

|              | H.9 Core Placement and Optimisation                                  |            |

|              | H.10 Clock Tree Synthesis                                            | . 225      |

|              | H.11 Preroute Standard Cells                                         |            |

|              | H.12 Core Route and Optimisation                                     | . 226      |

|              | H.13 Insert Fillers                                                  |            |

|              | H.14 Verification                                                    |            |

|              | H.15 Save the File                                                   | . 226      |

| I            | Synopsys IC Compiler Reports for Physical Implementation of the      | 10         |

| T            | Proposed RNS-based Image Processor                                   | 227        |

|              | I.1 Linking the Design                                               |            |

|              | I.2 Sanity Check on TLU+ Files                                       |            |

|              | I.3 Floorplanning                                                    |            |

|              | I.4 Placement                                                        |            |

|              | I.5 Chip Summary                                                     |            |

|              | I.6 Legalize Displacement                                            |            |

|              | I.0       Leganze Displacement         I.7       Clock Tree Summary  |            |

|              | I.7       Clock free Summary         I.8       Filler Cell Insertion |            |

|              |                                                                      |            |

|              | I.9 Design Verification                                              | . 233      |

| Li           | st of Acronyms/Abbreviations                                         | 235        |

| Re           | eferences                                                            | 239        |

# List of Figures

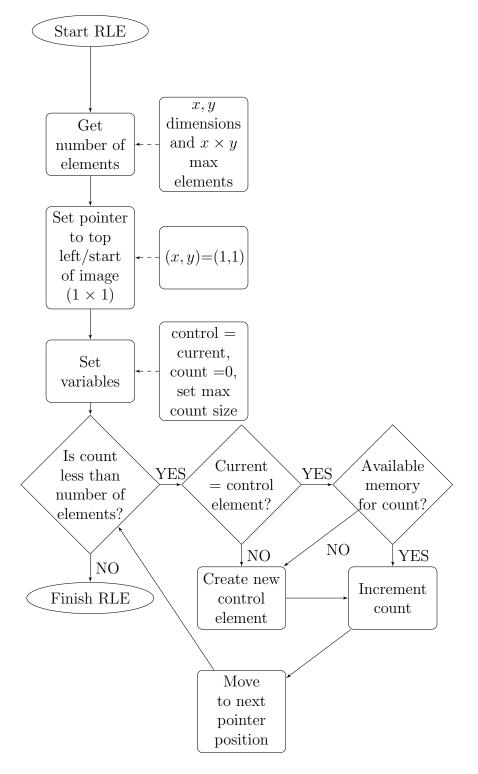

| 2.1  | RLE flowchart                                                                    | 15 |

|------|----------------------------------------------------------------------------------|----|

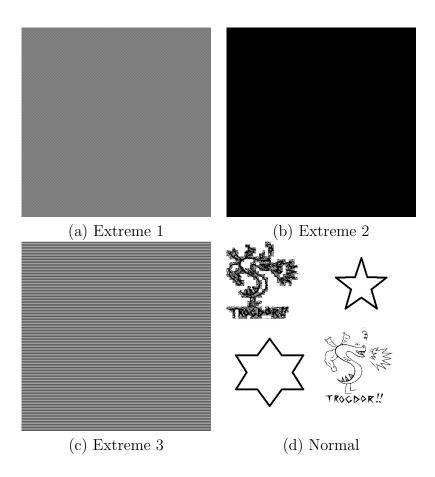

| 2.2  | Test images: (a) a solid 0101 extreme, (b) a solid 1111 extreme, (c) one         |    |

|      | row 1111 and one row 0000 alternately, (d) a normal image                        | 18 |

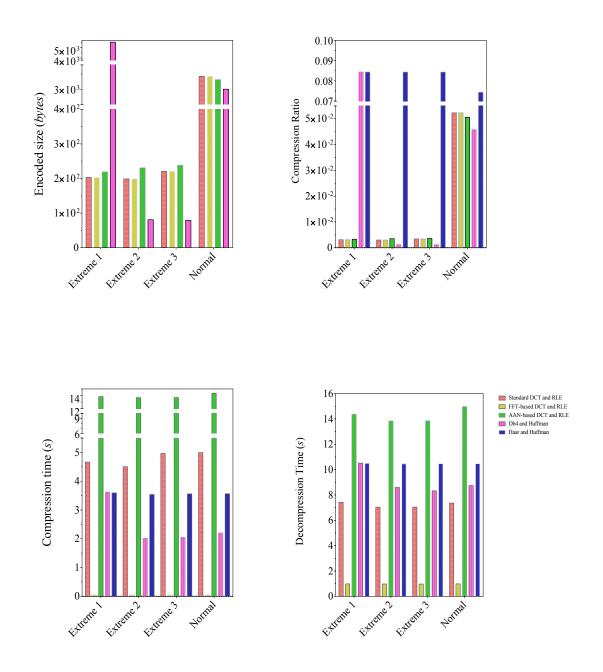

| 2.3  | Overall performance of selected algorithms                                       | 23 |

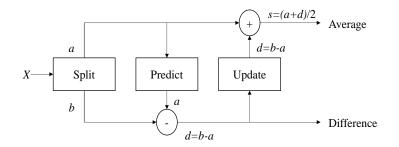

| 2.4  | Lifting scheme with three steps: split, predict and update                       | 26 |

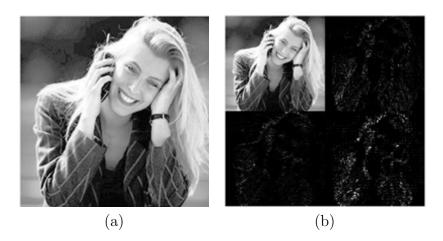

| 2.5  | Lifting-based image compression: (a) Original image "phone.jpg" $256 \times$     |    |

|      | 256, (b) One level of lifting decomposition                                      | 29 |

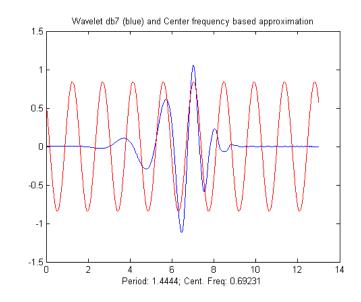

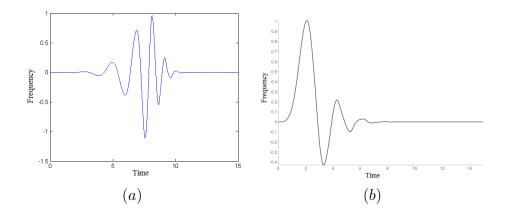

| 3.1  | Wavelet db7 (blue) and a centre-frequency-based approximations                   | 33 |

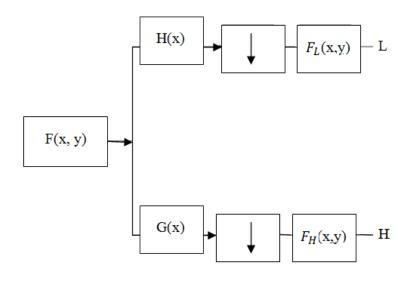

| 3.2  | One-dimensional DWT                                                              | 34 |

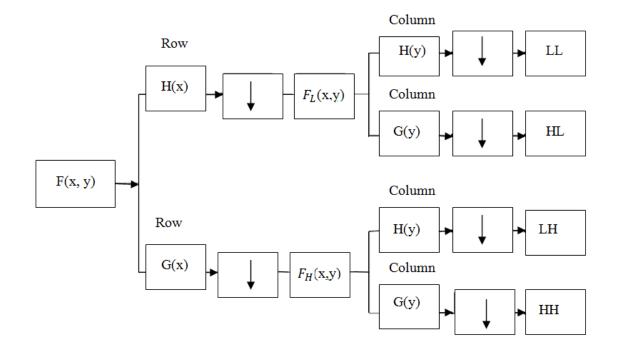

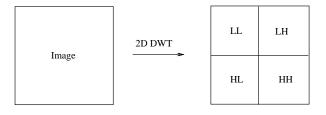

| 3.3  | Two-dimensional DWT                                                              | 34 |

| 3.4  | Decomposition of an image using 2D DWT to $LL, LH, HL$ and $HH$                  |    |

|      | data sets                                                                        | 35 |

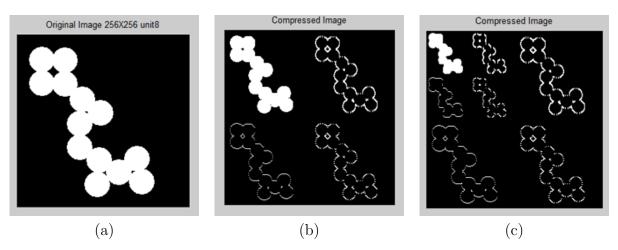

| 3.5  | Decomposition of a binary image using 2D DWT: (a) Original image                 |    |

|      | "circles.png" (256 $\times$ 256), (b) Image at level one, (c) Image at level two | 35 |

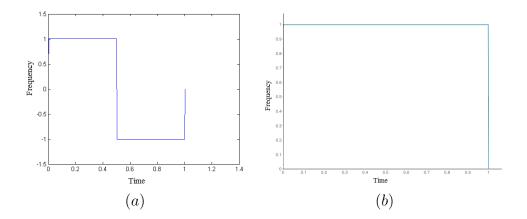

| 3.6  | Haar transform: (a) Mother wavelet function, (b) Scaling function (Fig-          |    |

|      | ure is generated using Matlab)                                                   | 38 |

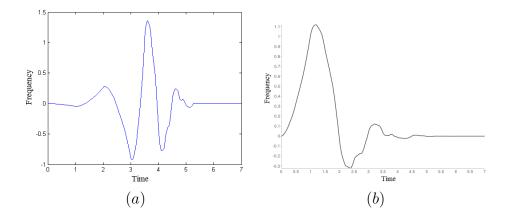

| 3.7  | db4: (a) Wavelet function, (b) Scaling function (Figure is generated             |    |

|      | using Matlab)                                                                    | 38 |

| 3.8  | db8: (a) Wavelet function, (b) Scaling function (Figure is generated             |    |

|      | using Matlab)                                                                    | 39 |

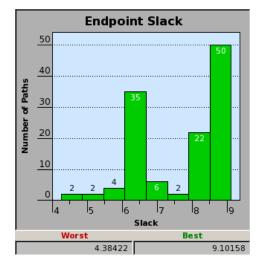

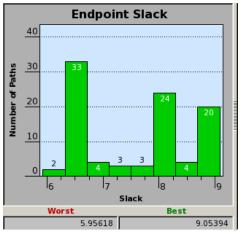

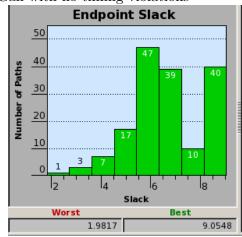

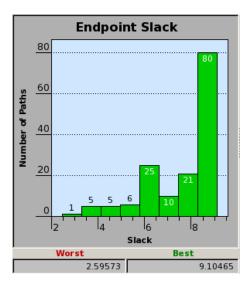

| 3.9  | Endpoint slack histogram of CDF97 with no timing violations $\ldots$ .           | 44 |

| 3.10 | Endpoint slack histogram of LeGall with no timing violations                     | 44 |

| 3.11 | Endpoint slack histogram of Haar with no timing violations                       | 44 |

| 3.12 | Endpoint slack histogram of db4 with no timing violations $\ldots \ldots \ldots$ | 44 |

| 3.13 | Endpoint slack histogram of db8 with no timing violations $\ldots \ldots \ldots$ | 45 |

|      |                                                                                  |    |

| 5.1  | Full-adder-based scaler $\begin{bmatrix} 1 \end{bmatrix}$                                         | 65                 |

|------|---------------------------------------------------------------------------------------------------|--------------------|

| 5.2  | Proposed scaling scheme using full-adder-based modular reducers $\ . \ .$                         | 65                 |

| 5.3  | VLSI architecture of modulo- $(2^n - 1)$ reducer                                                  | 69                 |

| 5.4  | VLSI architecture of modulo- $(2^n + 1)$ reducer                                                  | 69                 |

| 5.5  | VLSI architecture of the 3:2 compressor (full adder) used in modular                              |                    |

|      | reducers                                                                                          | 70                 |

| 5.6  | VLSI architecture of the half adder used in designing the modulo- $(2^n - 1)$                     |                    |

|      | reducer                                                                                           | 70                 |

| 5.7  | Proposed hybrid scaling scheme                                                                    | 77                 |

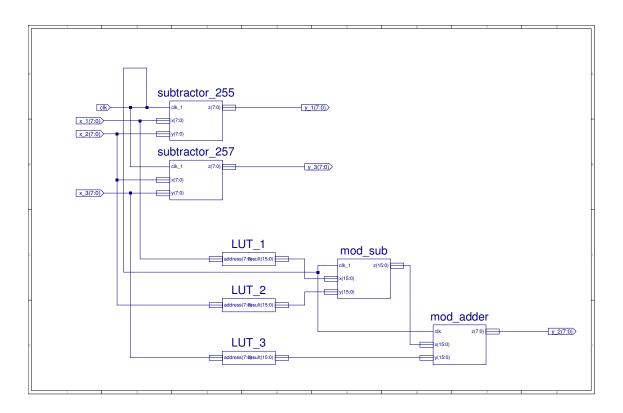

| 5.8  | Schematic of the proposed hybrid scaling scheme                                                   | 78                 |

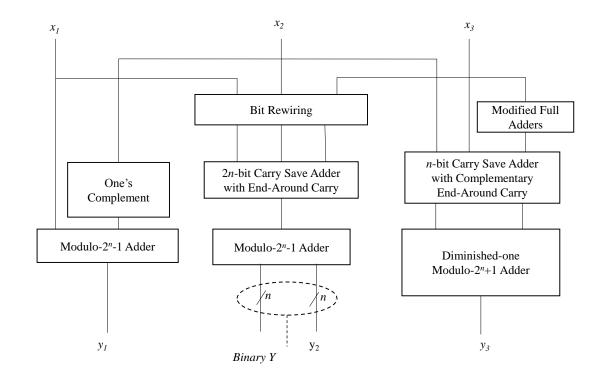

| 5.9  | Proposed method to generate $y_1$ in the moduli set $(2^n - 1, 2^{2n}, 2^n + 1, 2^{2n} + 1)$      | 1) <mark>89</mark> |

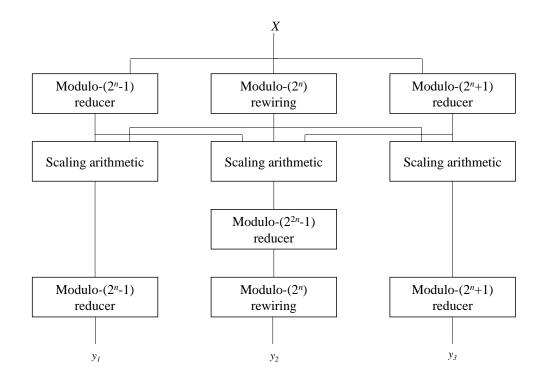

| 5.10 | Proposed method to generate $y_2$ in moduli set $(2^n - 1, 2^{2n}, 2^n + 1, 2^{2n} + 1)$          | 95                 |

| 5.11 | Proposed method to generate $y_3$ in moduli set $(2^n - 1, 2^{2n}, 2^n + 1, 2^{2n} + 1)$          | 97                 |

| 5.12 | Proposed modulo- $(2^n + 1)$ adder                                                                | 99                 |

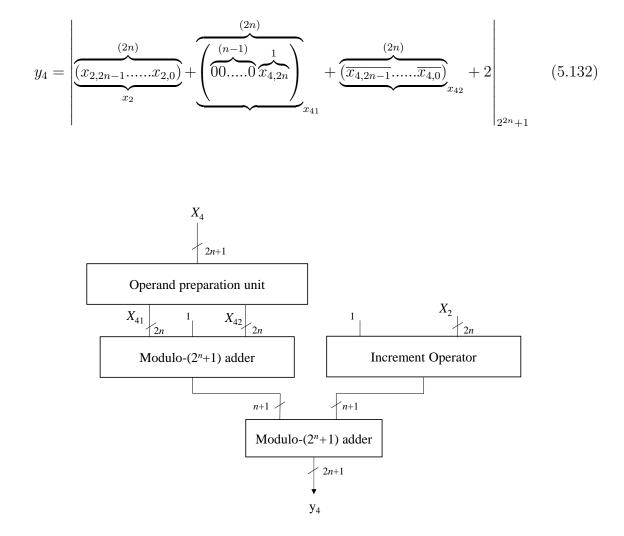

| 5.13 | Proposed method to generate $y_4$ in moduli set $(2^n - 1, 2^{2n}, 2^n + 1, 2^{2n} + 1)$          | 100                |

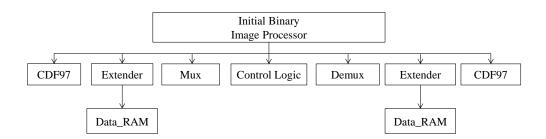

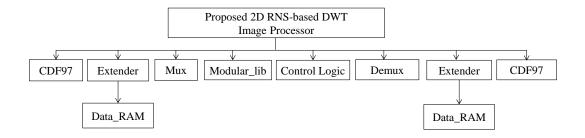

| 6.1  | Hierarchy of initial binary image processor                                                       | 08                 |

| 6.2  | Hierarchy of proposed RNS-based image processor                                                   | 08                 |

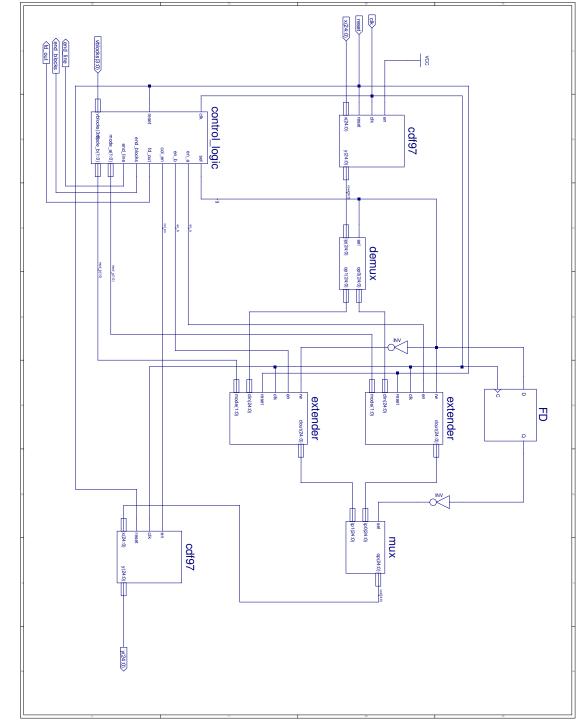

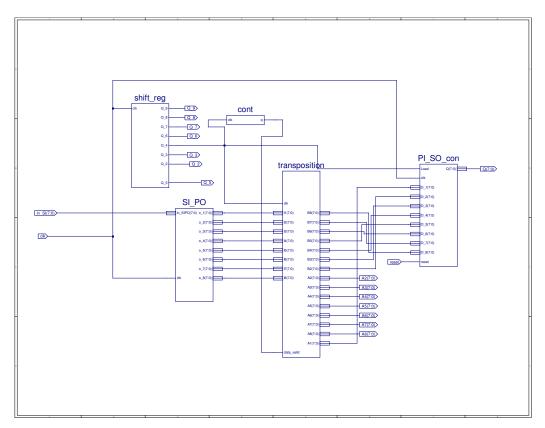

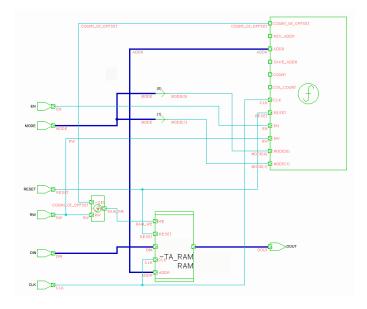

| 6.3  | Schematic of the proposed 2D RNS-based DWT digital image processor                                | 10                 |

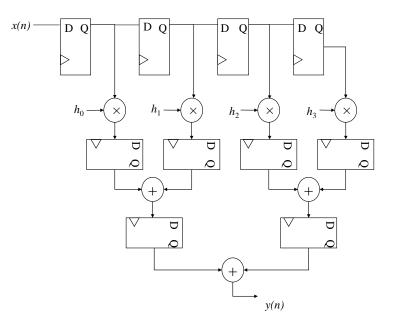

| 6.4  | A filter bank with a modular adder tree                                                           | 11                 |

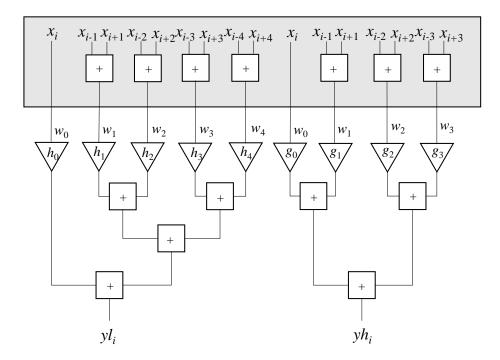

| 6.5  | Multiplierless implementation of DWT filter banks $[2]$                                           | 13                 |

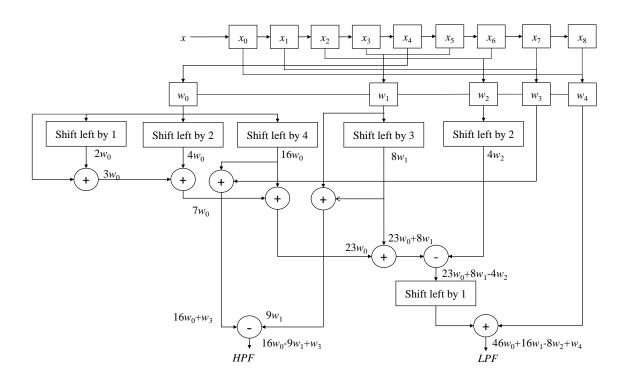

| 6.6  | Generating lowpass and highpass filter coefficients using shifts and ad-                          |                    |

|      | ditions                                                                                           | 14                 |

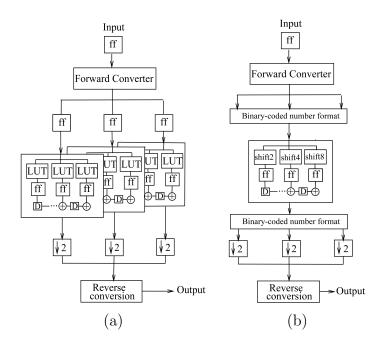

| 6.7  | Block diagram of (a) RNS-based filter banks based on the design in [3],                           |                    |

|      | (b) Proposed RNS-based filter banks                                                               | 15                 |

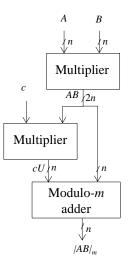

| 6.8  | Partitioned-operand modulo- $m$ multiplier [4] $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 115                |

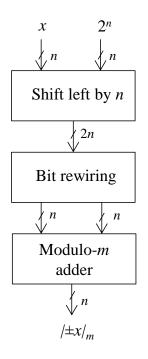

| 6.9  | Optimised modulo- $m$ multiplier $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 16                 |

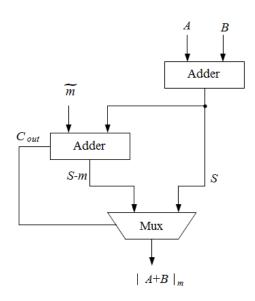

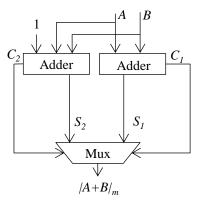

| 6.10 | Basic modulo- <i>m</i> adder where $(\tilde{m})$ denotes 2's-complement of $m$ [4]                | 117                |

| 6.11 | Proposed modulo- $m$ adder $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 117                |

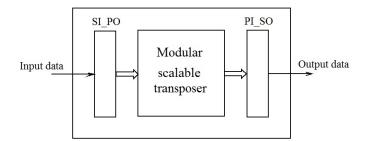

| 6.12 | Transposition unit                                                                                | 18                 |

| 6.13 | Modular scalable transposer                                                                       | 19                 |

| 6.14 | Serial-in, serial-out transposition unit                                                          | 19                 |

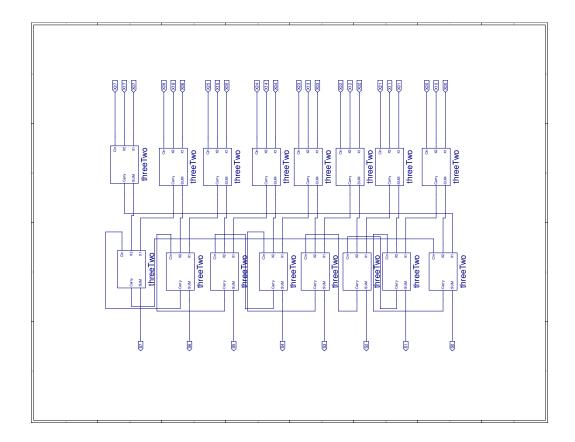

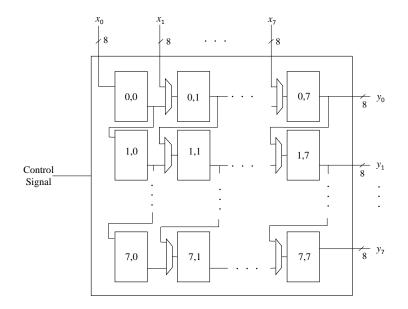

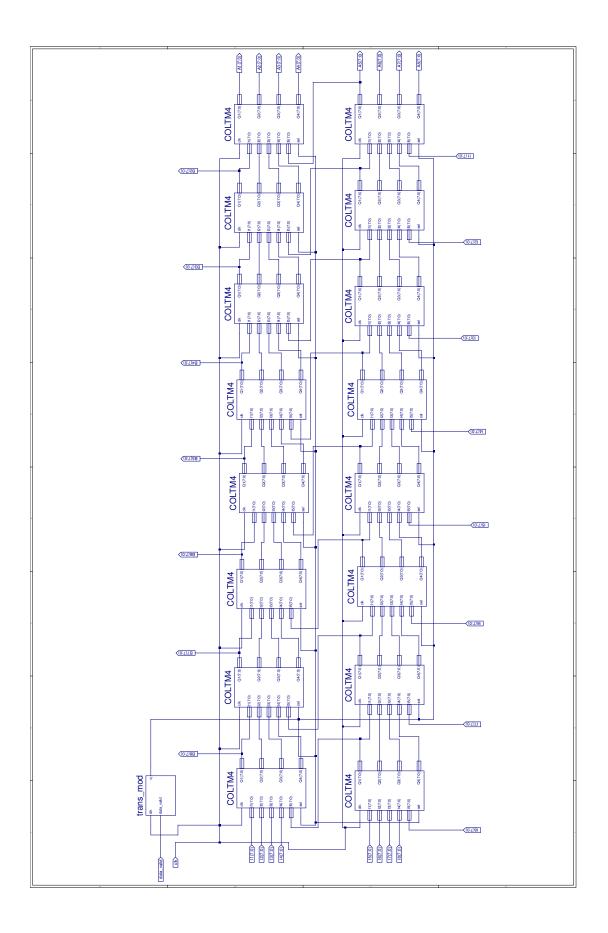

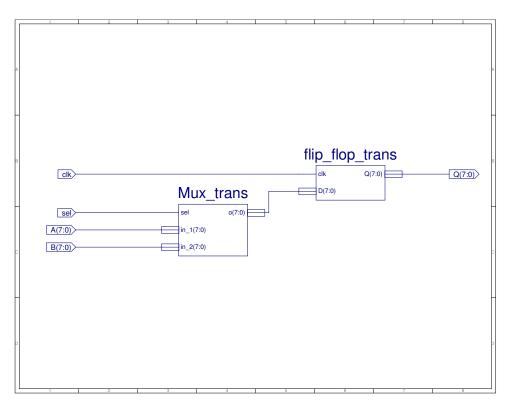

| 6.15 | VLSI architecture of the "transposition" in Figure $6.14$                                         | 21                 |

| 6.16 | VLSI architecture of COLTM4 in Figure 6.15                                                        | 22                 |

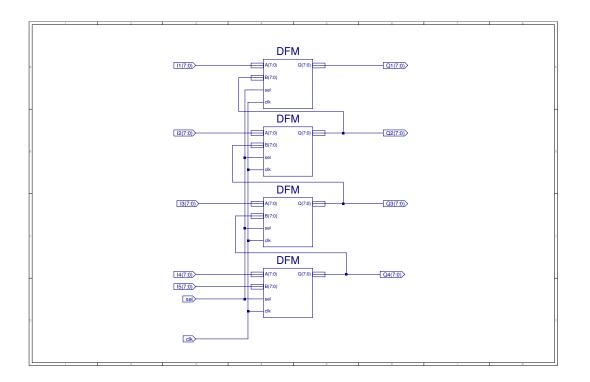

| 6.17 | VLSI architecture of DFM in Figure $6.16$                                                         | 22                 |

| 6.18 | Reading pattern of image data in transposition units                                              | .24                |

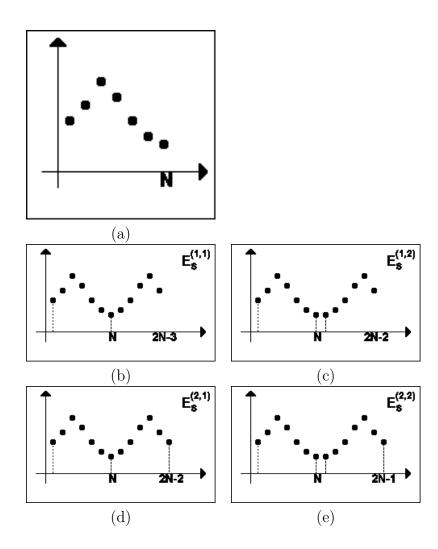

| 6.19 | Symmetric extension: (a) Original data of length $N$ , (b) Extension(1,1),        |      |

|------|-----------------------------------------------------------------------------------|------|

|      | (c) Extension $(1,2)$ , (d) Extension $(2,1)$ , (e) Extension $(2,2)$             | 125  |

| 6.20 | ModelSim simulation of proposed RNS-based image processor                         | 128  |

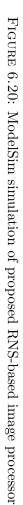

| 6.21 | Camera-man image after one level of 2D processing using proposed image            |      |

|      | processor                                                                         | 129  |

| 6.22 | Generation of iMPACT PROM file                                                    | 139  |

| 7.1  | Input and output files of Design Compiler for logic synthesis                     | 142  |

| 7.2  | Design constraints classified as design-rule constraints and design-optimisa      | tion |

|      | constraints $[5]$                                                                 | 144  |

| 7.3  | DC synthesis flow used for logic synthesis of the image processor                 | 149  |

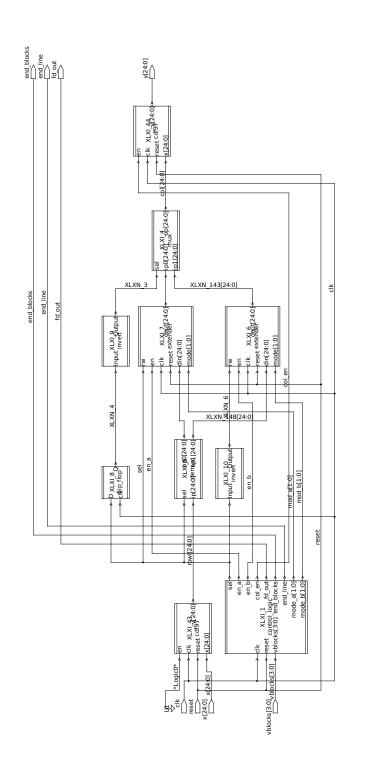

| 7.4  | Schematic of GTECH (technology independent) of the proposed 2D                    |      |

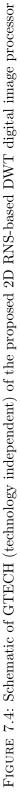

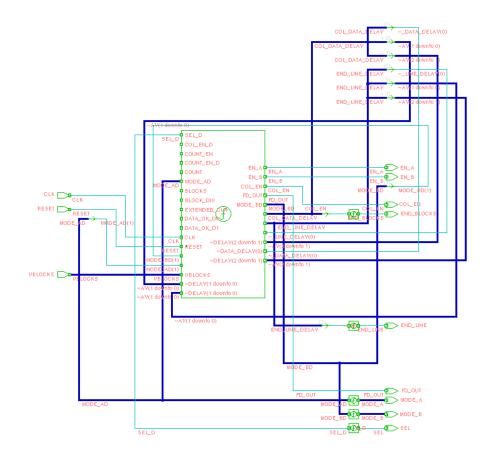

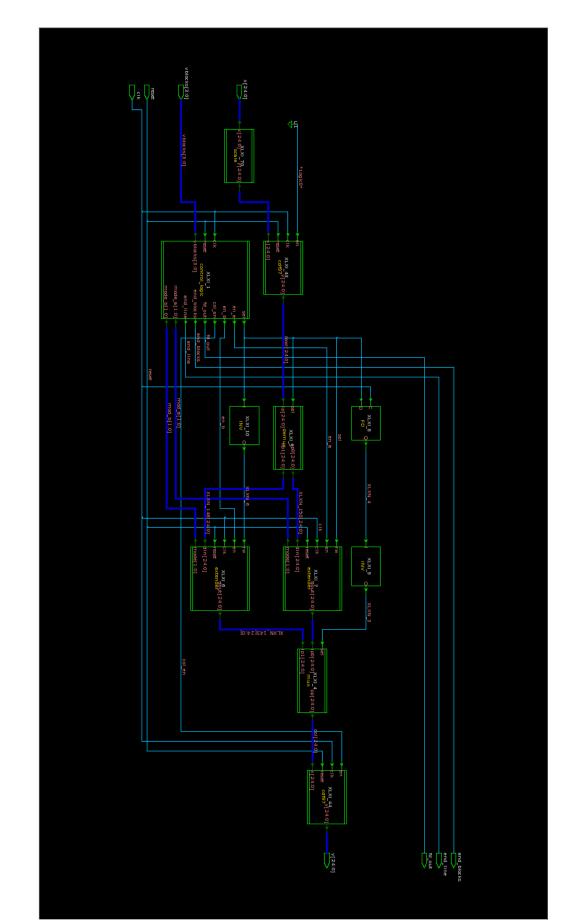

|      | RNS-based DWT digital image processor                                             | 151  |

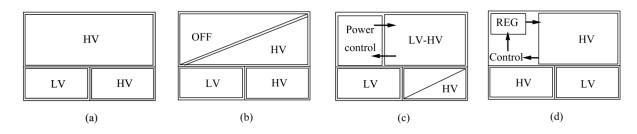

| 7.5  | The multi-voltage strategies: (a) Static, (b) With power gating, (c)              |      |

|      | Dynamic voltage/frequency scaling, (d) Adaptive voltage scaling (AVS)             |      |

|      | [6]                                                                               | 161  |

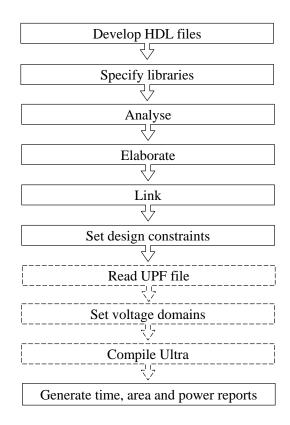

| 7.6  | Optimised synthesis flow to synthesise the proposed RNS-based image               |      |

|      | processor using the multi-voltage technique                                       | 163  |

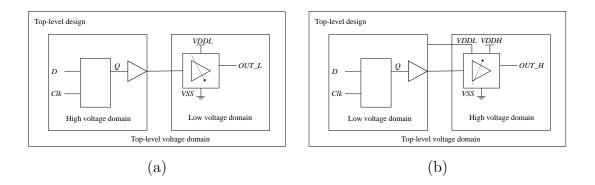

| 7.7  | Structure of level shifters: (a) High to low, (b) Low to high                     | 165  |

| 7.8  | Level-shifter placements in power domains                                         | 165  |

| 7.9  | Unified Power Format (UPF) diagram of the proposed image processor                | 166  |

| 7.10 | VCS schematic of the test bench including top-level, read and write               |      |

|      | modules                                                                           | 169  |

| 7.11 | VCS schematic of a RNS-based filter of the image processor $\hdots$               | 169  |

| 7.12 | VCS schematic of the main controller of the image processor $\ldots \ldots$       | 170  |

| 7.13 | VCS schematic of a transposition unit of the image processor                      | 170  |

| 7.14 | VCS schematic of demux module of the image processor $\ldots \ldots \ldots$       | 171  |

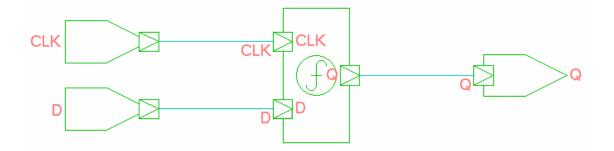

| 7.15 | VCS schematic of a flip flop of the image processor $\ldots \ldots \ldots \ldots$ | 171  |

| 7.16 | VCS schematic of a invert module the image processor                              | 171  |

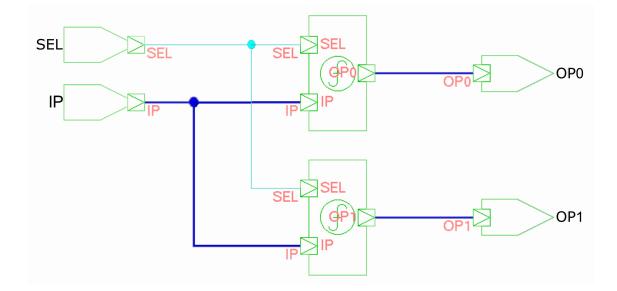

| 7.17 | VCS schematic of mux module of the image processor                                | 172  |

| 7.18 | Files generated by Synopsys tools to be used for power analysis                   | 174  |

| 7.19 | Overall view of the proposed RNS-based image processor waveforms                  | 178  |

| 7.20 | Zoomed view of the proposed RNS-based image processor waveforms $% \mathcal{A}$ . | 179  |

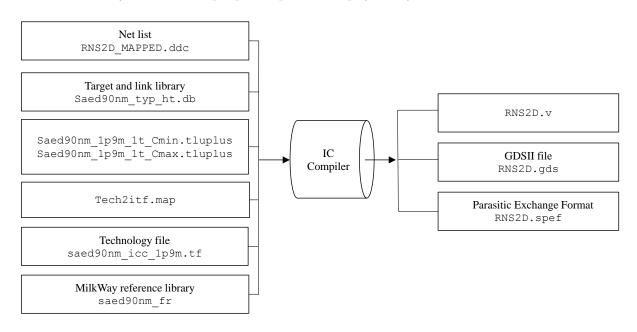

| 8.1  | Input and output of IC compiler                                                   | 182  |

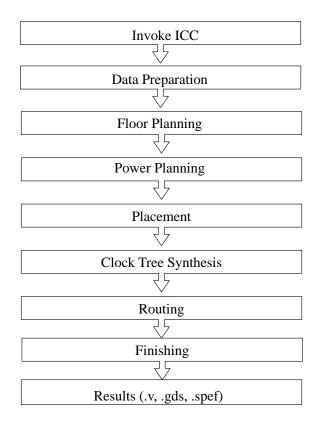

| 8.2  | Physical synthesis flow used to implement the RNS-based processor $\ . \ .$       | 183  |

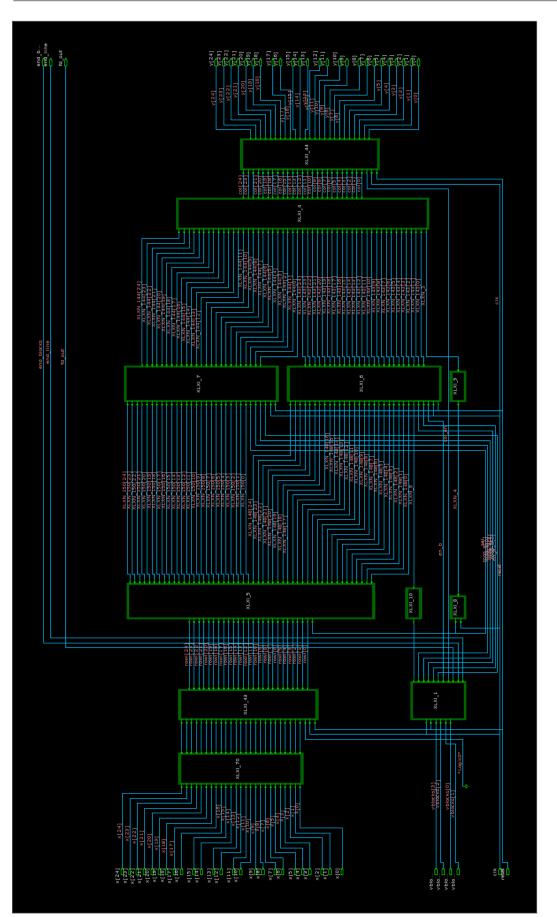

| 8.3  | Path-to-path schematic of the proposed 2D RNS-based image processor               | 191  |

| 8.4 | Schematic of the proposed 2D RNS-based image processor | 192 |

|-----|--------------------------------------------------------|-----|

| A.1 | Computer benchmark used for running MATLAB             | 201 |

| A.2 | MATLAB benchmark                                       | 202 |

## List of Tables

| 2.1  | The RLE Algorithm: results for encoding and decoding the test images          | 19 |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | The Canonical Huffman algorithm: results for encoding and decoding            |    |

|      | the test images                                                               | 19 |

| 2.3  | The DCT variant's encoding delay $(s)$ over the test images $\ldots$ $\ldots$ | 20 |

| 2.4  | The DCT variant's decoding delay $(s)$ over the test images $\ldots$ $\ldots$ | 20 |

| 2.5  | The DWT encoding and decoding delay for the test images                       | 20 |

| 2.6  | Performance of RLE over standard DCT coefficients                             | 21 |

| 2.7  | Performance of RLE over FFT-based DCT coefficients                            | 21 |

| 2.8  | Performance of RLE over AAN-based DCT coefficients                            | 22 |

| 2.9  | Performance of Huffman coding over Db4 coefficients                           | 22 |

| 2.10 | Performance of Huffman coding over Haar coefficients                          | 22 |

| 2.11 | Forward filter coefficients of lifting-based LeGall53                         | 26 |

| 2.12 | Reverse filter coefficients of lifting-based LeGall53                         | 27 |

| 2.13 | Pseudocode of the lifting scheme                                              | 28 |

| 3.1  | Haar lowpass and highpass filter coefficients $[7]$                           | 37 |

| 3.2  | CDF97 analysis filter coefficients $[8]$                                      | 40 |

| 3.3  | LeGall53 analysis filter coefficients                                         | 40 |

| 3.4  | Area, speed and power consumption of selected wavelet families $\ . \ . \ .$  | 41 |

| 3.5  | Library $TCB015GHDWC$ report                                                  | 42 |

| 3.6  | Area comparison of the selected wavelet families $(\mu m^2)$                  | 43 |

| 3.7  | Top-level design power analysis                                               | 43 |

| 3.8  | Critical path delay $(ns)$                                                    | 44 |

| 4.1  | Decimal, binary and one-hot residue modulo- $m_i$                             | 57 |

| 5.1  | Hardware utilisation of modular-reducer-based scaler                          | 71 |

| 5.2  | Power supply summary of modular-reducer-based scaler                          | 71 |

| 5.3  | On-chip power summary of modular-reducer-based scaler                                                        | 71  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 5.4  | Hardware utilisation of full-adder-based scaler                                                              |     |  |  |  |

| 5.5  | Supply power of full-adder-based scaler                                                                      |     |  |  |  |

| 5.6  | On-chip power summary of full-adder-based scaler                                                             | 73  |  |  |  |

| 5.7  | Numerical example of proposed hybrid scaler for residue set (123, 55,                                        |     |  |  |  |

|      | 250) and scaling factor 256 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 76  |  |  |  |

| 5.8  | Hardware utilisation of hybrid scaling scheme                                                                | 79  |  |  |  |

| 5.9  | On-chip power summary of hybrid scaling scheme                                                               | 79  |  |  |  |

| 5.10 | Supply power of hybrid scaling scheme                                                                        |     |  |  |  |

| 5.11 | Estimation of unit gate area of the proposed hybrid scaler                                                   | 81  |  |  |  |

| 5.12 | Estimation of unit gate delay of the proposed hybrid scaler                                                  | 81  |  |  |  |

| 5.13 | Estimated number of transistors of proposed hybrid scaler                                                    |     |  |  |  |

| 5.14 | Comparison of estimated number of transistors in proposed hybrid scaler                                      |     |  |  |  |

|      | and other designs for $n = 8$ , (255, 256, 257), and $M = 16776960$                                          | 82  |  |  |  |

| 5.15 | Comparison of estimated unit gate delay of proposed hybrid scaler and                                        |     |  |  |  |

|      | other designs for $n = 8$ , (255, 256, 257), and $M = 16776960$                                              | 82  |  |  |  |

| 5.16 | Numerical example of proposed scaler for four-moduli set $(3, 16, 5, 17)$                                    |     |  |  |  |

|      | and scaling factor 16                                                                                        | 101 |  |  |  |

| 5.17 | Full adder based (Chang) scaler Scale 1 $(2^n - 1)$ synthesis results $\ldots$                               | 102 |  |  |  |

| 5.18 | Full adder based (Chang) Scaler Scale 2 $(2^n)$ synthesis results $\ldots$                                   | 102 |  |  |  |

| 5.19 | Full adder based (Chang) scaler Scale 3 $(2^n + 1)$ synthesis results $\ldots$                               | 102 |  |  |  |

| 5.20 | Full adder based (Chang) scaler all components synthesis results $(2^n -$                                    |     |  |  |  |

|      | $1, 2^n, 2^n + 1$ )                                                                                          | 103 |  |  |  |

| 5.21 | Four-moduli Scale 1 $(2^n - 1)$ synthesis results $\ldots \ldots \ldots \ldots \ldots$                       | 103 |  |  |  |

| 5.22 | Four-moduli Scale 2 $(2^{2n})$ synthesis results                                                             | 103 |  |  |  |

| 5.23 | Four-moduli Scale 3 $(2^n + 1)$ synthesis results $\ldots \ldots \ldots \ldots \ldots$                       | 104 |  |  |  |

| 5.24 | Four-moduli Scale 4 $(2^{2n} + 1)$ synthesis results                                                         | 104 |  |  |  |

| 5.25 | Four-moduli scaler all components $(2^n - 1, 2^n + 1, 2^{2n}, 2^{2n} + 1)$ synthesis                         |     |  |  |  |

|      | results                                                                                                      | 104 |  |  |  |

| 5.26 | Four-moduli Scale 3 $(2^n + 1)$ synthesis results $\ldots \ldots \ldots \ldots \ldots$                       | 105 |  |  |  |

| 5.27 | Four-moduli Scale 4 $(2^{2n} + 1)$ synthesis results                                                         | 105 |  |  |  |

| 5.28 | Four-moduli scaler all components $(2^n - 1, 2^n + 1, 2^{2n}, 2^{2n} + 1)$ synthesis                         |     |  |  |  |

|      | results                                                                                                      | 105 |  |  |  |

| 6.1  | CDF97 filter coefficients multiplied by decimal number 256                                                   | 111 |  |  |  |

| 6.2  | Dyadic fractions of CDF97 filter coefficients                                                                | 112 |  |  |  |

| 6.3  | Symmetric extensions of signal $x$ with filter length of $N_0$                                             | 125 |

|------|------------------------------------------------------------------------------------------------------------|-----|

| 6.4  | Target FPGA device                                                                                         | 129 |

| 6.5  | Parameter set                                                                                              | 129 |

| 6.6  | Delay of the modular adder                                                                                 | 130 |

| 6.7  | FPGA resource consumption and power consumption of modular adders                                          | 130 |

| 6.8  | Delay of the modular multiplier                                                                            | 131 |

| 6.9  | FPGA resource consumption and power consumption of modular mul-                                            |     |

|      | tipliers                                                                                                   | 131 |

| 6.10 | Delay of modular channels                                                                                  | 131 |

| 6.11 | FPGA resource and power consumption of the modular channels                                                | 132 |

| 6.12 | Delay of modular scalable and proposed transposers                                                         | 132 |

| 6.13 | FPGA resource consumption and power consumption of transposers                                             | 133 |

| 6.14 | Delay of CDF97 filter banks designed by existing and proposed RNS-                                         |     |

|      | based modules                                                                                              | 133 |

| 6.15 | FPGA resource consumption and power consumption of modular filter                                          |     |

|      | banks                                                                                                      | 134 |

| 6.16 | Delay of binary and RNS-based image processors                                                             | 134 |

| 6.17 | FPGA resource consumption and power consumption of processors $\ $                                         | 135 |

| 6.18 | Comparison of the proposed RNS-based image processor with similar                                          |     |

|      | designs                                                                                                    | 136 |

| 7.1  | Setting up the search path, and target, link, symbol and work libraries                                    | 143 |

| 7.2  | Design constraints                                                                                         | 144 |

| 7.3  | Design environment                                                                                         | 145 |

| 7.4  | Library saed90nm_max_hth report                                                                            | 146 |

| 7.5  | Power hierarchy of all the references of the initial binary image processor                                | 153 |

| 7.6  | Area hierarchy of all the references of the initial binary image processor                                 | 154 |

| 7.7  | Power hierarchy of all the references of the RNS image processor                                           | 154 |

| 7.8  | Area hierarchy of all the references of the RNS image processor                                            | 155 |

| 7.9  | Critical path delay (In/out put: 25 bits, Filter coefficients: 6 bits, Op-                                 |     |

|      | erating voltage: 1.08 $V$ )                                                                                | 155 |

| 7.10 | Area comparison of the binary and RNS designs (In/out put: 25 bits, $% \left( 1 + \frac{1}{2} \right) = 1$ |     |

|      | Filter coefficients: 6 bits, Operating voltage: 1.08 $V$ )                                                 | 156 |

| 7.11 | Top-level design power analysis of initial binary and RNS processors                                       |     |

|      | (In/out put: 25 bits, Filter coefficients: 6 bits, operating voltage: $1.08V)$                             | 156 |

| 7.12 | Comparison of common LPD methods [9]                                                                       | 160 |

| 7.13 | Library saed90nm_max report used as low-voltage library                    | 164 |  |

|------|----------------------------------------------------------------------------|-----|--|

| 7.14 | 4 Power state table (PST) of the multi-voltage processor                   |     |  |

| 7.15 | Critical path delay of the initial binary and proposed RNS-based designs   |     |  |

|      | (In/out put: 25 bits, Filter coefficients: 6 bits, Top-level voltage: 1.08 |     |  |

|      | V, Extender voltage: 0.7 $V$ )                                             | 166 |  |

| 7.16 | Area comparison of the initial binary and proposed RNS-based designs       |     |  |

|      | (In/out put: 25 bits, Filter coefficients: 6 bits, Top-level voltage: 1.08 |     |  |

|      | V, Extender voltage: 0.7 $V$ )                                             | 167 |  |

| 7.17 | Top-level-design power analysis of initial binary and proposed RNS-        |     |  |

|      | based processors (In/out put: 25 bits, Filter coefficients: 6 bits, Top-   |     |  |

|      | level voltage: 1.08 $V$ , Extender voltage: 0.7 $V$ )                      | 167 |  |

| 7.18 | List of cells in the proposed processor                                    | 175 |  |

| 7.19 | Power domains of the multi-voltage processor                               | 176 |  |

| 7.20 | Supply nets of the multi-voltage processor                                 | 176 |  |

|      | Supply sets of the multi-voltage processor                                 | 176 |  |

| 0.1  |                                                                            |     |  |

| 8.1  | The Max_TLU+, Min_TLU+, and the layer-mapping file between tech-           | 104 |  |

|      | nology library and ITF file                                                | 184 |  |

| 8.2  | Planner summary of RNS-based image processor implementation                | 185 |  |

| 8.3  | The power and ground nets and pins setting of RNS-based image pro-         |     |  |

|      | cessor implementation                                                      | 185 |  |

| 8.4  | Creating rectangular rings for VDD and VSS nets of the RNS-based           |     |  |

|      | image processor                                                            | 186 |  |

| 8.5  | Place optimisation settings used in placement step of RNS-based image      |     |  |

|      | processor implementation                                                   | 186 |  |

| 8.6  | RNS-based image processor chip summary report                              | 187 |  |

| 8.7  | Legalise displacement of the chip                                          | 187 |  |

| 8.8  | Clock tree summary                                                         | 188 |  |

| 8.9  | Route optimisation strategy for the design                                 | 189 |  |

| 8.10 | Filler cell insertion                                                      | 189 |  |

| 8.11 | Comparison of the proposed RNS-based image processor with dedicated        |     |  |

|      | hardware designs                                                           | 194 |  |

| 8.12 | Chip characteristics                                                       | 196 |  |

| B.1  | Synopsys DC synthesis results of Chang scaler-Scale 1                      | 204 |  |

| B.2  | Synopsys DC synthesis results of Chang scaler-Scale 2                      | 205 |  |

| B.3  | Synopsys DC synthesis results of Chang scaler-Scale 3                      | 206 |  |

| B.4 | Synopsys DC synthesis results o | f Chang scaler | <br>207 |

|-----|---------------------------------|----------------|---------|

|     |                                 |                |         |

# Introduction

As technology has advanced in past decades, people have seen the potential of computing devices and have dreamed of the faster and more efficient products and services that can be provided only by digital hardware. This has created a demand for continual advancement in the speed and efficiency of existing systems.

Advances in science and technology have also required the use of digital image compression in demanding applications such as commercial photography, industrial imagery, geophysics, machine vision, medical imaging, control and automation, telemetry, satellite imagery, military and security sciences, agriculture applications, graphic arts and multimedia, network, Internet, or storage media. All these applications require a large volume of computational operations for processing images. Hence, exploring a way to increase the processing speed and reduce the power consumption is essential.

Various methods have been developed and introduced to optimise existing image processing systems. Among proposed schemes, optimising the arithmetic level of image processors and replacing conventional number systems by the Residue Number System (RNS), have drawn more attention, since arithmetic system plays an important role in satisfying the requirement for a large volume of computational operations in image processing [10, 11].

Conventional number systems use a base approach, where each digit is multiplied

by a base value to attain its real value. All the weighted values are then added up to attain the actual number. The three most commonly used examples of conventional number systems are binary (base 2), decimal (base 10) and hexadecimal (base 16).

Replacing conventional binary number systems with the Residue Number System (RNS) has been steadily rising in favour over the last 50-60 years. The RNS-based architecture allows the processing of modular channels simultaneously, and saves significant delays in arithmetic operations. Using small integers in independent channels also reduces the carry propagation and the number of partial products in adders and multipliers, respectively [12, 13].

Despite many publications regarding the application of RNS for digital image processing [3, 14–19], it is still at an early stage. Due to RNS's complex operations (sign detection, division and magnitude comparison) most of these studies are based on ultimately unjustified assumptions, and are inexact with many errors in the results.

This thesis will provide a design and optimisation for a RNS-based digital image processor in detail and examine it against a binary processor. The study will also implement the proposed processor with static voltage scaling to achieve the best powerperformance trade-off in the proposed image processor.

## **1.1** Existing Literature

The literature regarding RNS-based image processing is sparse. An extensive literature search on the "RNS-based image processor" results in only a few tens of hits and many of them are not directly relevant to the interests of this thesis. The literature which has been deemed to be directly relevant to our topic is discussed below. The first FIR filter implementation using RNS has been reported in 1977, by Jenkins [20]. They implemented a dual-bandpass FIR filter using the moduli set (7, 9, 11, 13, 16), and compared it with a 2's-complement contender. The authors concluded that the RNS-based FIR filters perform with higher throughput than the 2's-complement contender. In 2000, a RNS application in implementing orthogonal wavelet filter banks was presented [21, 22]. The filter banks were designed using LUTs, and they processed 8-bit inputs with 10-bit filter coefficients. The resulting system ran 23.45% and 96.58% faster than a 2's-complement design for one and two octaves, respectively. The weakness of their design was using LUTs for modular multiplications. They provided a comparison between FPL implementation of RNS and binary 1D DWT architectures. No details of the synthesis results were provided.

In 2001, Ammar et al. [23] used RNS and the Chinese Remainder Theorem (CRT)

for encoding and encryption of image pixels. The result was an encrypted image that needed the moduli set (key) for decryption and reading. They used look-up tables (LUT) for conversion from RNS to the binary number system; however there was no compression process in the proposed technique.

The design and implementation of a RNS wavelet processor using custom IC technologies has been presented by in 2003 [14]. They used RNS for implementing wavelet filter banks using an enhanced index transformation over a Galois field. Their system was compared with 2's-complement designs, and showed up to 100% performance improvement. The authors only contributed to designing the filter banks rather than implementing the whole processor. The main shortcoming of the Ramirez design is that it does not address any other RNS modules in the RNS wavelet processor apart from the filter banks. Hence, they neglected the effect of the multi-dimensional requirement of processing an image, which is addressed in this thesis.

In contrast with [14], the authors in [24] used RNS to implement low-power and low-leakage FIR filters. This idea was contrary to the Ramirez design, that concluded that RNS increased the speed of operations but also increased the hardware complexity and power consumption. They applied RNS in order to reduce the static and dynamic power consumption of FIR filters. [24] compared 16-, 32- and 64-tap FIR filter implementations in 2's-complement and RNS, and showed that the RNS filters offer a reduction of 50% in static power dissipation and a total power reduction of 40%. The effect of RNS on power consumption of a system is provided in Chapter 7.

In 2004, the authors in [25] investigated the application of RNS for digital image processing. They presented a VLSI implementation of an image coding scheme using the RNS and modified CRT. The proposed scheme encrypted the entire image and did not require any additional component other than a standard RNS system. Again, no compression algorithm was used for image compression. The details of the modular units, nor the synthesis results of their processor were not provided.

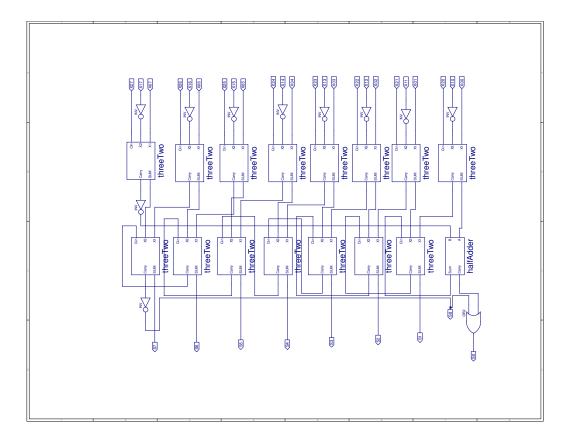

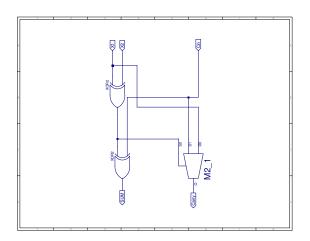

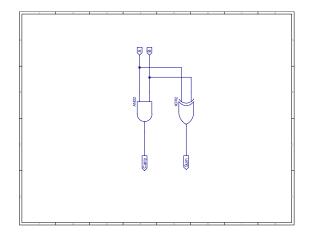

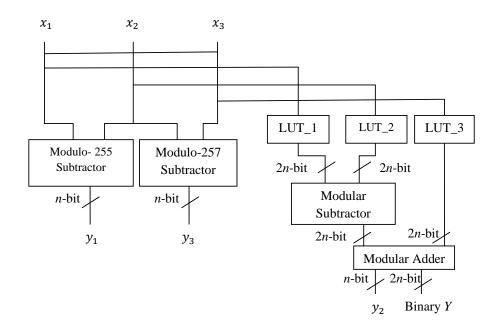

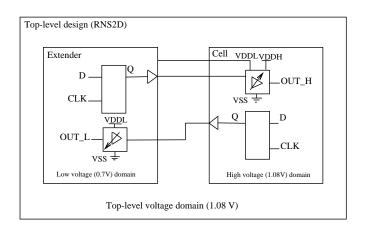

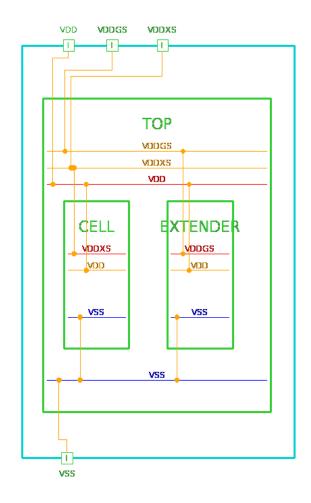

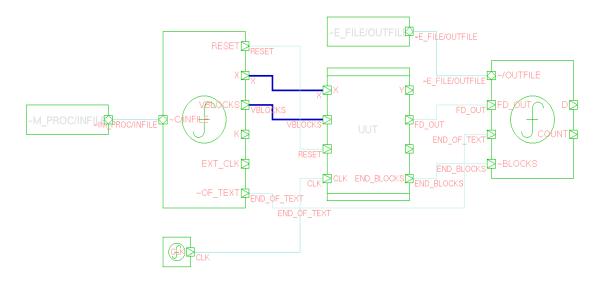

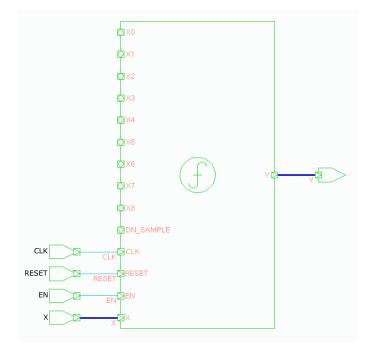

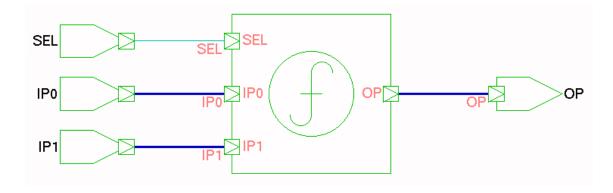

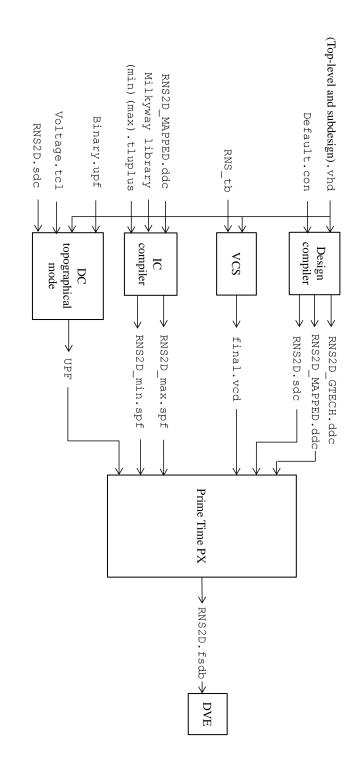

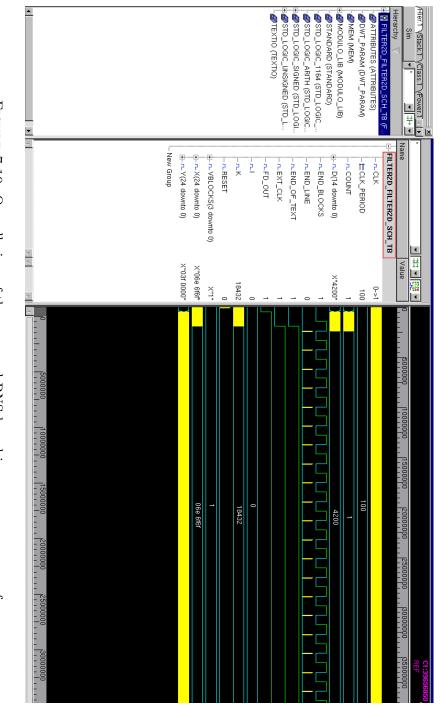

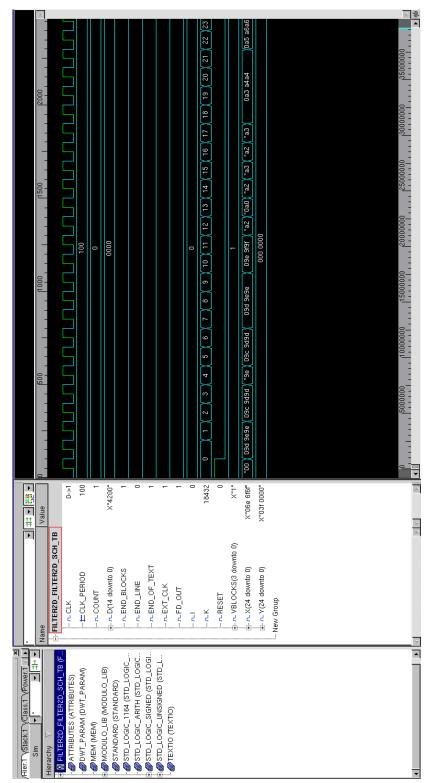

Another RNS-based design in 2004 was the design and implementation of an RNSbased image processor using DWT filter banks and RNS arithmetic in [3]. The proposed design used 27 look-up tables (LUT) for modular multiplication, each with 8-bit width and 256 entries. The downside of their processor was that the LUTs and RAMs are the main sources of leakage power, which is the major concern of standalone applications like mobile phones and cameras. In addition, the authors in [14] have reported that the best RNS designs have a hardware cost about the same as or more than the binary designs. In other words, while using RNS can help to enhance the performance of an image processor, the architecture of using modular arithmetic might increase the hardware complexity and power consumption of the system [26]. Therefore, one question that needs to be answered is what aspects of RNS-based designs are superior to binary designs.