## ANALOGUE RF FRONT-END IC DESIGN FOR ULTRA-WIDEBAND IMPLANTABLE WIRELESS BODY AREA NETWORK RADIO

$\mathbf{b}\mathbf{y}$

IJI AYOBAMI BABATUNDE

Dissertation submitted in fulfilment of the requirements

for the degree of

### DOCTOR OF PHILOSOPHY

Department of Engineering Faculty of Science Macquarie University Sydney, Australia

December 12, 2013.

#### ABSTRACT

Implantable wireless body area networks (WBAN) are a promising technology for health monitoring and treatment of patients requiring special care, where sensors are placed inside the human body to carry out measurements which may include telemetry or video streaming. Ultra-Wideband technology (UWB) is investigated as a candidate for the proposed implanted wireless body area sensor network due to its wide frequency spectrum and, hence, its low bit energy. UWB is introduced and then explored in terms of system constraints and circuit implementation.

In this work the author has explored the unlicensed frequency spectrum to achieve better communication for implantable medical devices, since the licensed frequency band has been occupied and is overcrowded. The advantages of the unlicensed frequency band technology include a wide bandwidth which allows for Gigabit data rates over short distances. This technology only requires low power consumption due to the low complexity of the Ultra-wideband system and the low transmit power. However, with the growing demand for wireless communications systems, more challenging requirements arise. Since a wide frequency range is required, the design of a transceiver front end in the entire frequency range is challenging. In this work the author has designed a transceiver RF front end, optimised for low power using Silicon on Sapphire (SOS) CMOS technology. The circuit designed has been fabricated and measured.

The author also describes how applicable UWB is used for implantable WBANs and invites future work on designing a radio capable of being installed inside the human body for medical care and monitoring.

### STATEMENT OF CANDIDATE

I certify that the work in this thesis entitled "Analogue RF Front-End IC Design For Ultra Wideband Implantable Wireless Body Area Network Radio" has not previously been submitted for a degree nor has it been submitted as part of the requirements for a degree to any other university or institution other than Macquarie University.

I also certify that the thesis is an original piece of research and it has been written by me. Any help and assistance that I have received in my research work and the preparation of the thesis itself have been appropriately acknowledged.

In addition, I certify that all information sources and literature used are indicated in the thesis.

. . . . . . . . . . . . . . . . . .

IJI Ayobami Babatunde (Student ID: ) December 12, 2013.

#### ACKNOWLEDGMENTS

This thesis would not have been possible without the help, support and patience of my principal supervisor Professor Michael Heimlich in supervising my PhD. He gave me the best in terms of material and knowledge. He encouraged me to work on a variety of projects and thereby provided me with a well-rounded perspective in engineering education. His philosophy of researching fundamental issues that limit the availability of low-cost commercial electronics is both compelling and challenging. I am grateful to him for giving me the freedom to work on things that fitted within the framework of my project. He is an inspiring mentor and a good supervisor; he is always willing to assist.

I would like to express my gratitude to my co-supervisor Professor Anthony Parker for his words of advice as well as giving me books from his library on circuit design when I knocked at his door for assistance. Projects managed by him and Professor Eryk Dutkiewicz funded the circuit design tape-out; without them the tape-out would have been difficult.

This project is also partially funded by the David Skellern Electronics Research Grant.

I should like to thank Dr Xi Zhu (Forest) who now works at Nanyang Technological University, Singapore for his support and contributions to the success of my design. Many thanks are due to Oya Sevimli for sharing with me her experience in circuit design and measurement. Eahteshamul Hoque, Carl Svensson, Aaron Pereira and Sayed Albahrani are my colleagues in the office; they have also contributed in one way or another to the success of my research work. In particular Jabra Terazi provided a lot of support in device modelling; many thanks for his assistance.

A special thanks to Dr Keith Imrie, an associate to the Department of Engineering, for his professional editorial advice on language and illustrations as well as completeness and consistency, and the program manager Daniel McGill for personally volunteering to provide assistance on professional editorial advice on language and illustration.

I have often greatly benefited from the experience and opinion of other researchers in the field and I should like to thank the following people for their indirect contributions to my thesis: Gengfa Fang and Ana Borba. On a personal note I want to express my regard for all members of staff at the Department of Engineering.

Finally, I acknowledge the encouragement and support given by my parents Chief MWO Olusogo Iji and mrs Sarah Iji; and other members of my family most especially my wife Rachael and our son Abraham; my uncle Comrade Sola Iji and his family; my siblings mrs Bankole Bosede, mrs Abbey Abidemi, mrs Alewi Oluwayemisi, mrs Isowa Abolanle, Pastor Michael Iji, Ayotunde Iji and Elizabeth Oluwakemi Iji. To The Most High GOD and my father Thomson Olusogo Iji.

Romans 9:16 So then, it is not of him that willeth, nor of him that runneth, but of God that showeth mercy.

#### STATEMENT OF ORIGINALITY

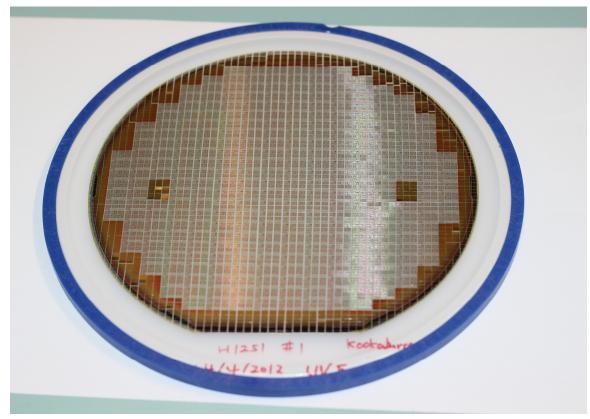

The designs reported in this thesis were carried out at the Engineering Department, Faculty of Science, Macquarie University between August 2010 and December 2013, under the supervision of Professor Michael Heimlich and cosupervised by Professor Anthony Parker. I Also closely worked with a postdoctoral research fellow in the project, Dr Xi Zhu. The circuits designed in this thesis were fabricated at the Silanna foundry, which is the only silicon laboratory in Australia.

This thesis comprises of eight chapters and three appendix sections. An outline of the main achievements of the work for the thesis is given in Chapter 1. The work of others is acknowledged and referred to in the body of the thesis. The following paragraphs state those portions of the work which are claimed as original contributions of the author.

Chapter 2 and Chapter 3 contain a summary of the work of others. Chapter 2 is mainly background information on the importance of the technology, device process, and characterisation, and citations are been made from different books and publications. The work in Chapter 3 contains some details about the entire UWB system to be designed. Here the author has used existing link budget equations to calculate the required metric for the proposed system architecture.

In Chapter 4, circuit design commences, based on the details of the work in Chapter 2. The first stage of a receiver circuit after the receiving antenna, the low noise amplifier (LNA), requires special consideration and design techniques; some topologies used in the past for LNA circuit design are referred to in various books. In this work the author has proposed a low power LNA, achieved with the SOS CMOS process technology as a result of it's low threshold operation capability.

The component that follows the LNA in the receiver chain is the mixer; in Chapter 5, the author has reviewed various mixer architectures which include active and passive types of mixer. Both types have been designed for experimental purposes to actually determine the most appropriate type for the receiver circuit. The author has designed both active and passive mixers from existing topologies but with the aim of utilising low power design. The idea of designing a passive mixer was initiated by the author. A passive mixer does not occupy much chip area compared to an active mixer. The circuits in Chapter 4 and Chapter 5 when cascaded make the receiver RF front end.

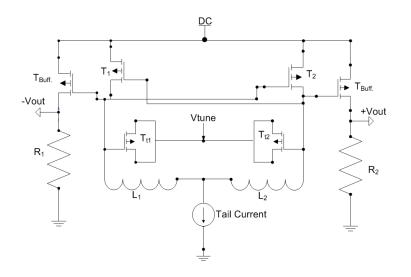

In UWB transmitter design the major components are the voltage controlled oscillator (VCO) and the pulse generator. In Chapter 6 various VCOs have been reviewed, and the Inductor Capacitor (LC) tank VCO type was proposed due to its low DC power consumption and better phase noise compared to others. The idea of using a MOS varactor was suggested by Dr Xi Zhu.

The pulse generator was designed by the author, who proposed that the pulse generator be driven by a VCO to generate the required UWB pulses.

In Chapter 7, describing the transceiver RF front end, the author has made cascade circuits of mixer and LNA which make up the receiver, and a combination of VCO and pulse generator which make up the transmitter. Chapter 8 concludes the thesis and give suggestions for future work.

Overall, most usage issues associated with the AWR simulation software were solved by Professor Michael Heimlich, and in circuit design layout, similar issues were solved by Dr Xi Zhu.

The material in this thesis has not been submitted towards another degree at

this or any other university.

## List of Publications

Some of the work presented in this thesis has appeared as published peer-reviewed journal or conference papers, has been accepted for publication at the time of writing, or has been presented at conferences. I was the main contributor to the publications listed below.

- Iji Ayobami, Forest Zhu and Michael Heimlich, "Design of Low Power, Wider Tuning Range CMOS Voltage Controlled Oscillator for Ultra Wideband Applications", IEEE International Conference on Integrated Circuit Design and Technology (ICI-CDT), May, 2012. (cf. Chapter 6)

- Iji Ayobami, Forest Zhu and Michael Heimlich, "Low Power, High gain, Low Noise Amplifier (LNA) for Ultra Wide-band Applications", Microwave and Optical Technology Letters, Vol. 55, Issue 12, February, 2013. (cf. Chapter 4)

- Iji Ayobami, Forest Zhu and Michael Heimlich, "A Folded-Switching Mixer in SOI CMOS Technology", 55th Int'l Midwest Symposium on Circuits and Systems (MWSCAS), August, 2012. (cf. Chapter 5)

- 4. Iji Ayobami, Forest Zhu and Michael Heimlich, "A 3 5 GHz LNA in 0.25μm SOI CMOS Process for Implantable WBANs", 55th Int'l Midwest Symposium on Circuits and Systems (MWSCAS), August, 2012. (cf. Chapter 4)

- Iji Ayobami, Forest Zhu and Michael Heimlich, "Proposed Ultra-Wideband System, and Receiver Circuit for Implantable Wireless Body Area Networks", 12th International Symposium on Communications and Information Technologies (ISCIT), October, 2012. (cf. Chapter 2)

- Iji Ayobami, Forest Zhu and Michael Heimlich, "A Down Converter Active Mixer, in 0.25μm SOI CMOS process for Ultra Wide-Band Applications", International Symposium on Communications and Information Technologies (ISCIT), October, 2012. (cf. Chapter 5)

- Iji Ayobami, Forest Zhu and Michael Heimlich, "High Gain/Power Quotient Variable-Gain Wideband LNA for Capsule Endoscopy Application", Microwave and Optical Technology Letters, Vol. 54, Issue 11, November, 2012. (cf. Chapter 4)

- Iji Ayobami, Forest Zhu and Michael Heimlich, "A 4.5 mW 3 5 GHz Low-Noise Amplifier in 0.25μm Silicon-on-Insulator CMOS Process for Power - Constraint Application", Microwave and Optical Technology Letters, Vol. 55, Issue 1, January, 2013. (cf. Chapter 4)

# Contents

| Ab                   | stra                                                  | let                                                                                                                                                                                                                                                                               | iii                                                                                                                |

|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Ac                   | knov                                                  | wledgments                                                                                                                                                                                                                                                                        | vii                                                                                                                |

| Sta                  | atem                                                  | nent of Originality                                                                                                                                                                                                                                                               | xi                                                                                                                 |

| $\operatorname{Lis}$ | t of                                                  | Publications                                                                                                                                                                                                                                                                      | $\mathbf{x}\mathbf{v}$                                                                                             |

| Tal                  | ble o                                                 | of Contents 2                                                                                                                                                                                                                                                                     | xvii                                                                                                               |

| $\operatorname{Lis}$ | t of                                                  | Figures                                                                                                                                                                                                                                                                           | xxi                                                                                                                |

| $\operatorname{Lis}$ | t of                                                  | Tables                                                                                                                                                                                                                                                                            | vii<br>xi<br>xv<br>xvii<br>xvii<br>xxi<br>xxv<br>1<br>logy 2<br>                                                   |

|                      | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | PoductionMotivationOverview of Ultra-Wideband TechnologyUltra-Wideband Standards1.3.1IEEE 802.15.6Task Group1.3.2Impulse Radio-Based UWB SystemUpdate on UWB CMOS Transceiver DesignAuthor's ContributionsSynopsis                                                                | $     \begin{array}{c}       1 \\       2 \\       4 \\       4 \\       5 \\       7 \\       8     \end{array} $ |

|                      | Bac<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                | kgroundImplantable WBAN TransceiverApplication RequirementsUWB Standardisation and Spectrum RegulationUWB Transceiver ArchitectureSelected IR-UWB Modulation Schemes2.5.1Pulse Position Modulation2.5.2Pulse Amplitude Modulation2.5.3On-Off Keying2.5.4Binary Phase Shift Keying | 13<br>14<br>15<br>17<br>19<br>19<br>20<br>20                                                                       |

|          | $2.6 \\ 2.7$ | Design Process Technology                               | 22<br>23 |

|----------|--------------|---------------------------------------------------------|----------|

|          |              | 11                                                      | 24       |

|          |              | 0 ( )                                                   | 25       |

|          |              | 0 0                                                     | 26       |

|          |              | 2.7.4 Transistor IN-RF DC-IV Characteristics Analysis   | 28       |

|          | 2.8          | Discussion                                              | 30       |

|          | 2.9          | Summary                                                 | 32       |

| 3        | IR-          | UWB System Analysis                                     | 35       |

|          | 3.1          | Introduction                                            | 35       |

|          | 3.2          | Link Budget Analysis                                    | 36       |

|          |              |                                                         | 36       |

|          |              | 3.2.2 Multipath and Fade Margin                         | 37       |

|          |              | 3.2.3 Range and Path Loss                               | 38       |

|          |              | 3.2.4 Noise Power                                       | 38       |

|          |              | 3.2.5 Receiver Sensitivity                              | 39       |

|          |              |                                                         | 40       |

|          | 3.3          | Prospective Circuit DC Power Consumption                | 40       |

|          | 3.4          | Discussion                                              | 42       |

| 4        | Wic          | leband Low Noise Amplifier                              | 43       |

|          | 4.1          | -                                                       | 43       |

|          | 4.2          |                                                         | 44       |

|          | 4.3          | Low Noise Amplifier Topologies                          | 46       |

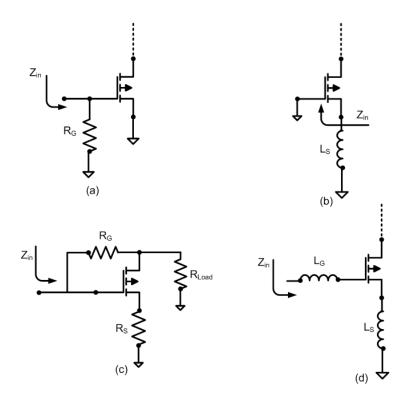

|          |              | 4.3.1 Common-source amplifier with shunt input resistor | 46       |

|          |              |                                                         | 47       |

|          |              |                                                         | 48       |

|          |              | 4.3.4 Inductively degenerated common-source amplifier   | 48       |

|          | 4.4          |                                                         | 48       |

|          |              |                                                         | 48       |

|          |              |                                                         | 50       |

|          |              | 4.4.3 Linearity Improvement Technique                   | 52       |

|          |              |                                                         | 56       |

|          | 4.5          |                                                         | 58       |

|          | 4.6          | Č ·                                                     | 59       |

|          | 4.7          | •                                                       | 62       |

|          | 4.8          |                                                         | 63       |

| <b>5</b> | Wic          | leband Mixers                                           | 65       |

| -        | 5.1          |                                                         | 65       |

|          | 5.2          |                                                         | 66       |

|          | <b>.</b>     |                                                         | 67       |

|          |              |                                                         |          |

xviii

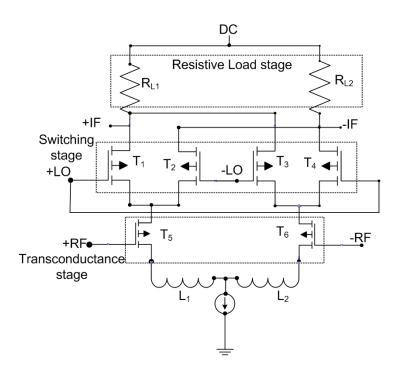

|   |     | 5.2.2  | Gilbert-Cell Mixers                        |

|---|-----|--------|--------------------------------------------|

|   |     | 5.2.3  | Passive FET Mixer                          |

|   | 5.3 | Wideb  | and FET-Based Gilbert-Cell (Active) Mixer  |

|   |     | 5.3.1  | Gilbert-Cell Mixer Conversion Gain         |

|   |     | 5.3.2  | Gilbert-Cell Mixer Noise Figure            |

|   |     | 5.3.3  | Gilbert-Cell Mixer Linearity               |

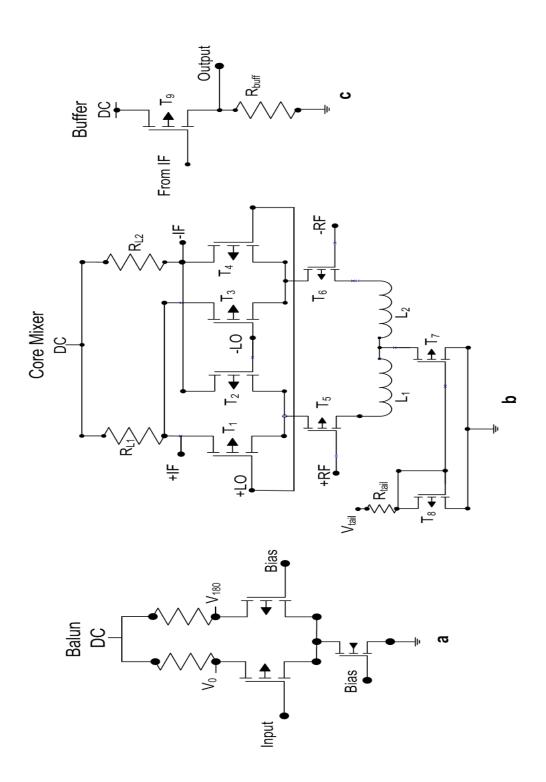

|   | 5.4 | Propos | sed Ultra Wideband Active Mixer Design     |

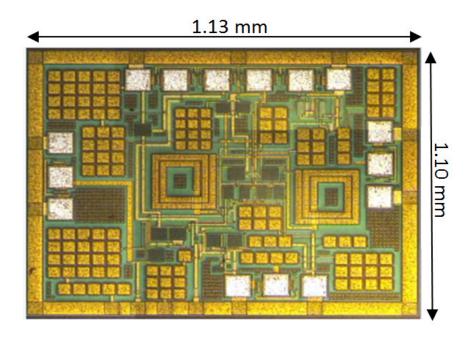

|   |     | 5.4.1  | Designed Active Mixer Layout               |

|   |     | 5.4.2  | Designed Active Mixer; Experiment Results  |

|   | 5.5 | Wideb  | and Passive Down Converter                 |

|   |     | 5.5.1  | Passive Mixer Switching                    |

|   |     | 5.5.2  | Designed Passive Mixer Layout              |

|   |     | 5.5.3  | Designed Passive Mixer; Experiment Results |

|   | 5.6 | Summ   | ary of Mixer Design                        |

| 6 | Wie | lehand | Oscillators and Pulse Generators 89        |

| U | 6.1 |        | uction                                     |

|   | 6.2 |        | e Controlled Oscillator Design             |

|   | 6.3 |        | rties of Oscillator                        |

|   |     | 6.3.1  | Oscillator Design Theory                   |

|   |     | 6.3.2  | Phase noise of an ideal oscillator         |

|   |     | 6.3.3  | Tuning Frequency of VCO                    |

|   |     | 6.3.4  | VCO Designed with MOS Varactor             |

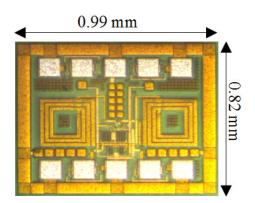

|   |     | 6.3.5  | VCO Layout                                 |

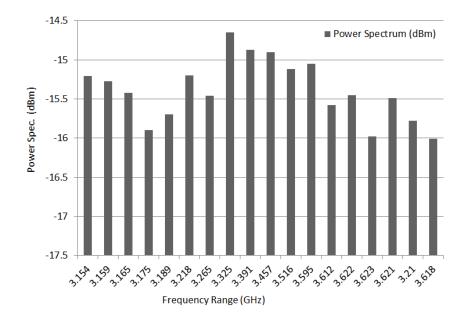

|   |     | 6.3.6  | Designed VCO Experiment Results            |

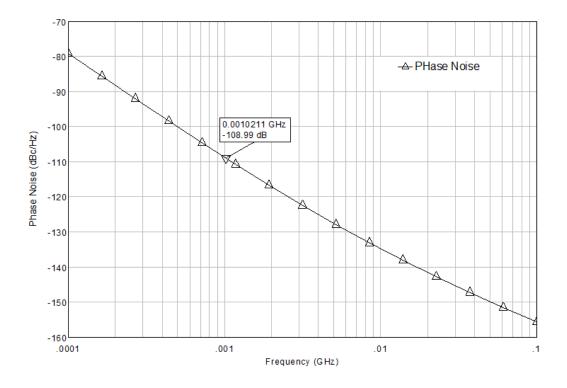

|   |     | 6.3.7  | Phase Noise Calculation                    |

|   |     | 6.3.8  | Automated Phase Noise Measurement          |

|   |     | 6.3.9  | VCO Figure of Merit (FoM) Calculation      |

|   | 6.4 | Discus | sion of the Designed VCO                   |

|   | 6.5 | Pulse  | Generator                                  |

|   |     | 6.5.1  | Motivation                                 |

|   |     | 6.5.2  | Pulse Generator Design                     |

|   | 6.6 | Pulse  | Generator Discussion                       |

| 7 | UW  | B Tra  | nsceiver RF Front End 117                  |

| • | 7.1 |        | uction to receiver design                  |

|   | 7.2 |        | Receiver Design Consideration              |

|   | 7.3 |        | VB Receiver Architecture                   |

|   | 7.4 |        | sed UWB Receiver Design                    |

|   |     | 7.4.1  | Receiver Circuit Layout                    |

|   |     | 7.4.2  | Receiver Design with Active Mixer          |

|   |     | 7.4.3  | Receiver Design with Passive Mixer         |

|   | 7.5 |        | er Design Summary                          |

|   | -   |        |                                            |

$\mathbf{xix}$

|    | 7.8<br>7.9        | Introduction to UWB Transmitter                                                                   | 130<br>131<br>131<br>134 |

|----|-------------------|---------------------------------------------------------------------------------------------------|--------------------------|

| 8  | <b>Con</b><br>8.1 | clusion and Future WorkSummary of Completed Work8.1.1Future Work                                  |                          |

| A  | A.1<br>A.2        | ivationMOSFET Two-Port Noise Parameters [1]Third-Order Non Linearity [1]VCO Design Constraint [1] | 142                      |

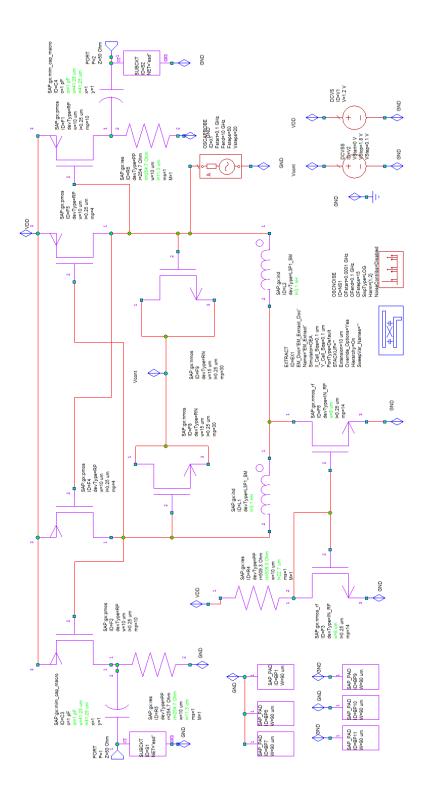

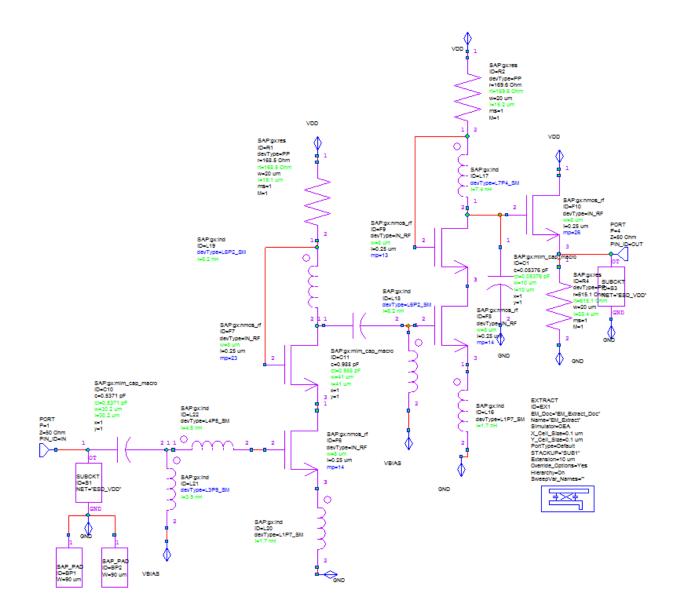

| В  | Circ              | cuit Schematics in AWR                                                                            | 145                      |

| С  | Abb               | previations                                                                                       | 153                      |

| Bi | bliog             | raphy                                                                                             | 157                      |

# List of Figures

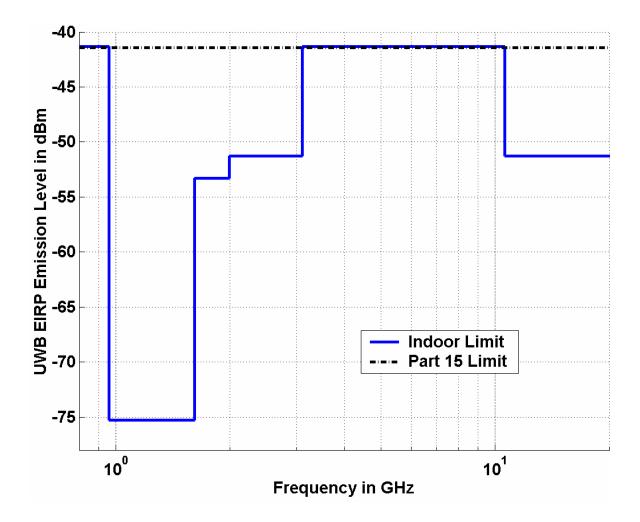

| 2.1  | Spectrum Mask of UWB for Indoor Environments                                                                  | 16 |

|------|---------------------------------------------------------------------------------------------------------------|----|

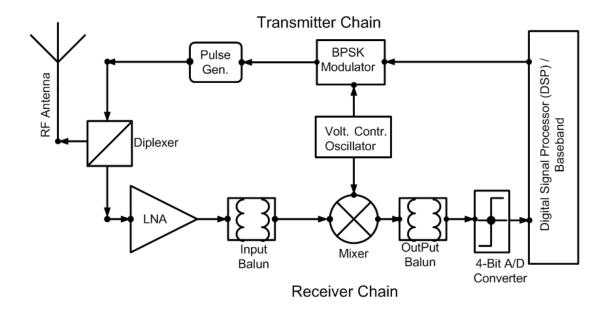

| 2.2  | The UWB System for Implantable WBANs                                                                          | 18 |

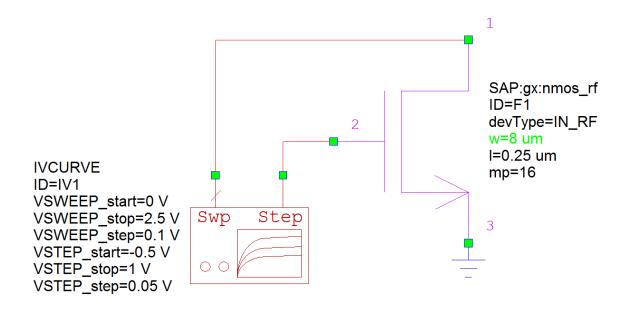

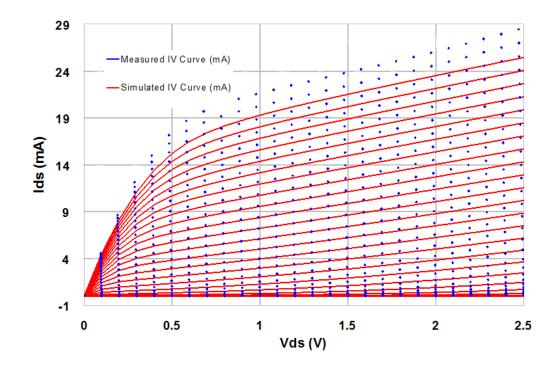

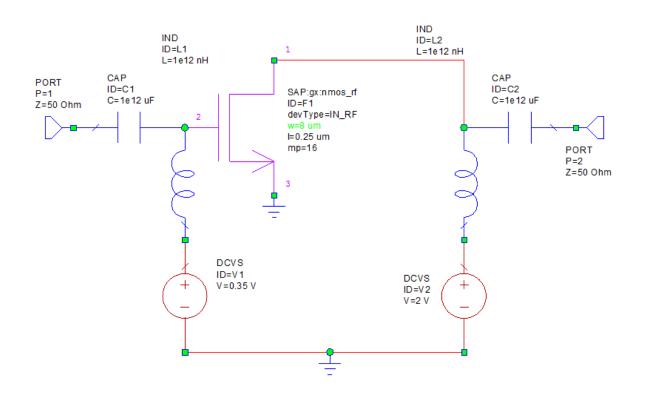

| 2.3  | DC-IV Characteristics Circuit                                                                                 | 29 |

| 2.4  | DC-IV Characteristics of the Transistor, Measured vs. Simulated                                               | 29 |

| 2.5  | Simulation Setup for the Transistor S-Parameter                                                               | 30 |

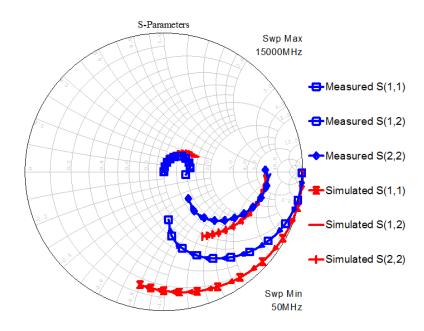

| 2.6  | Simulated and Measured S-Parameters of the Transistor in Smith Chart                                          | 31 |

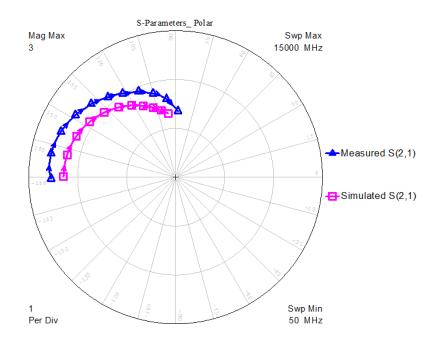

| 2.7  | Simulated and Measured S-Parameters of the Transistor in Polar plot                                           | 31 |

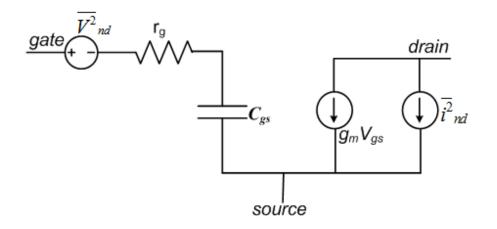

| 4.1  | MOS Noise Model [1] $\ldots$ | 45 |

| 4.2  | (a) Common-source Amplifier with Shunt Input Resistor, (b) Shunt-series                                       |    |

|      | Amplifier $(1/g_m \text{ termination})$ , (c) Common Gate Amplifier (Passive feed-                            |    |

|      | back termination), (d) Inductively Degenerated Common-source Amplifier                                        | 47 |

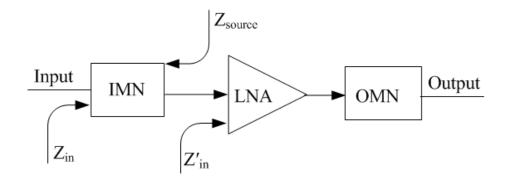

| 4.3  | LNA Matching Network                                                                                          | 49 |

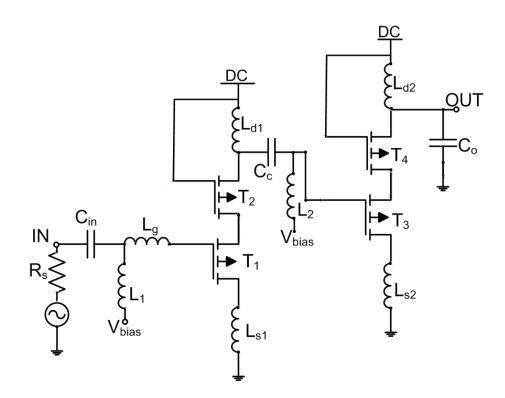

| 4.4  | Low Noise Amplifier Circuitry                                                                                 | 49 |

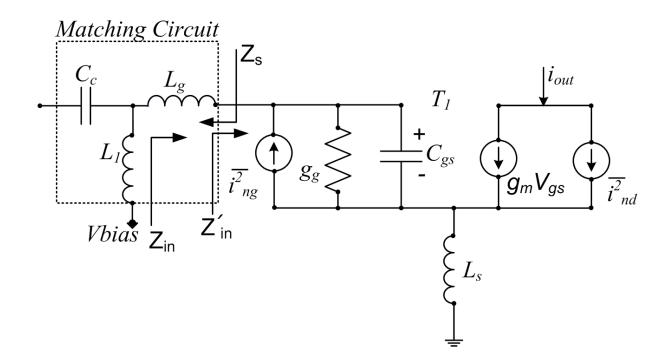

| 4.5  | LNA Input Matching Network                                                                                    | 51 |

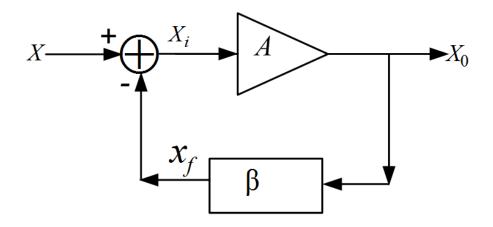

| 4.6  | Nonlinear Amplifier with Negative Feedback                                                                    | 54 |

| 4.7  | (a) Inductive Source-degeneration LNA (b) Small-signal Model                                                  | 55 |

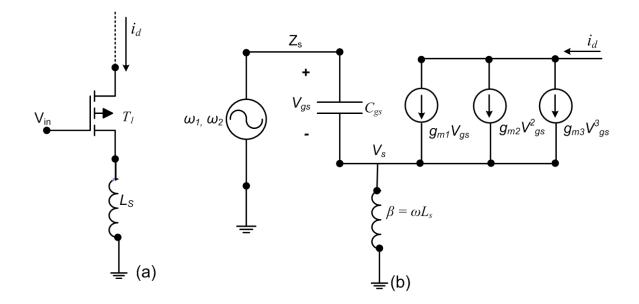

| 4.8  | Buffer Circuit for LNA Output Impedance Matching                                                              | 57 |

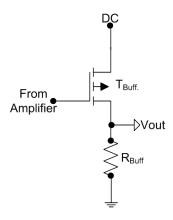

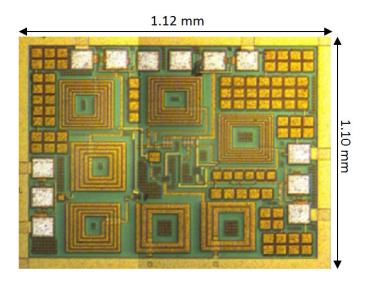

| 4.9  | Fabricated LNA Micrograph                                                                                     | 58 |

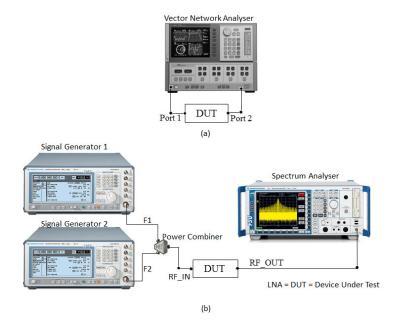

| 4.10 | (a) VNA Calibration Setup, (b) Measurement Setup for Linearity of a Two-                                      |    |

|      | port Device                                                                                                   | 59 |

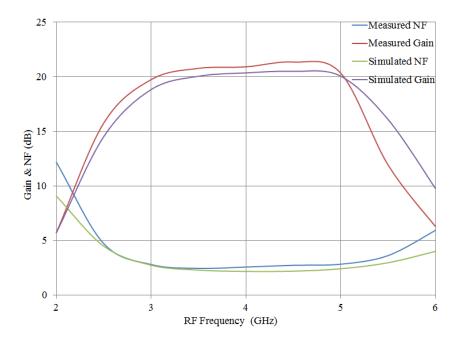

| 4.11 | Measured LNA Gain vs Noise Figure                                                                             | 60 |

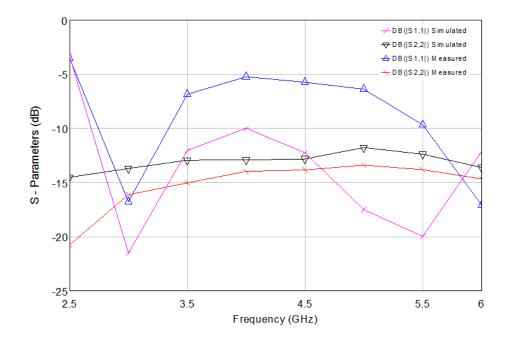

| 4.12 | Measured Input and Output Return Loss                                                                         | 61 |

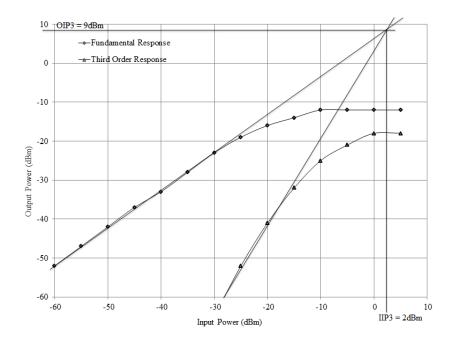

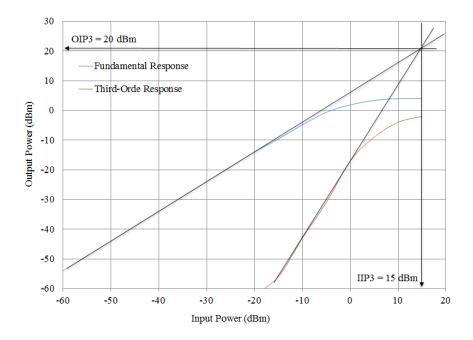

| 4.13 | Measured IIP3 of the Designed LNA                                                                             | 61 |

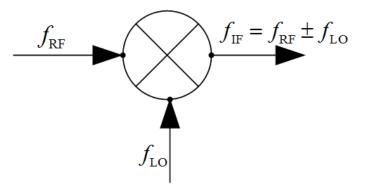

| 5.1  | Fundamental Mixer Block Diagram                                                                               | 67 |

| 5.2  | Gilbert-Cell Mixer                                                                                            | 70 |

| 5.3  | Proposed Gilbert-Cell Mixer: (a) Single-End to Differential Balun, (b) Core                                   |    |

|      | Mixer, (c) Output Buffer.                                                                                     | 76 |

| 5.4  | Fabricated Active Mixer Micrograph                                                                            | 77 |

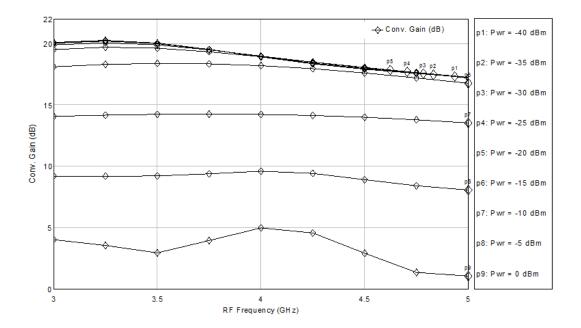

| 5.5  | Active Mixer Conversion Gain vs Frequency Post-layout Result                                                  | 78 |

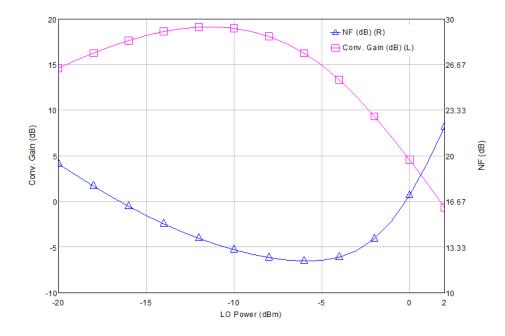

| 5.6  | Active Mixer Conversion Gain and NF vs LO Power Post-layout Result                                            | 79 |

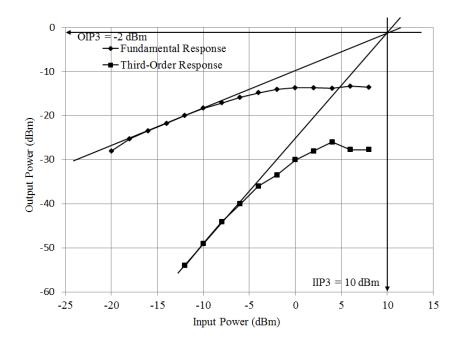

| 5.7  | Measured Active Mixer Linearity                                                                               | 79 |

|      |                                                                                                               |    |

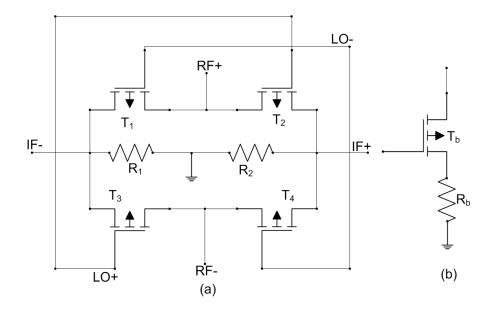

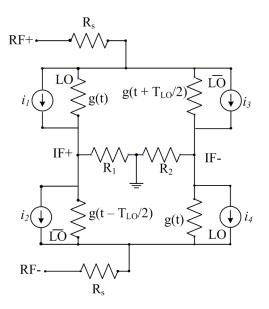

| 5.8                                       | (a) Passive Mixer and (b) Output Balun                                                                                                               | 81  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9                                       | Equivalent Core Passive Mixer Circuit                                                                                                                | 81  |

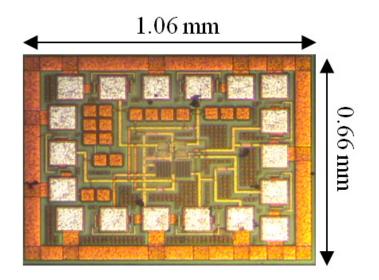

| 5.10                                      | Fabricated Passive Mixer Micrograph                                                                                                                  | 84  |

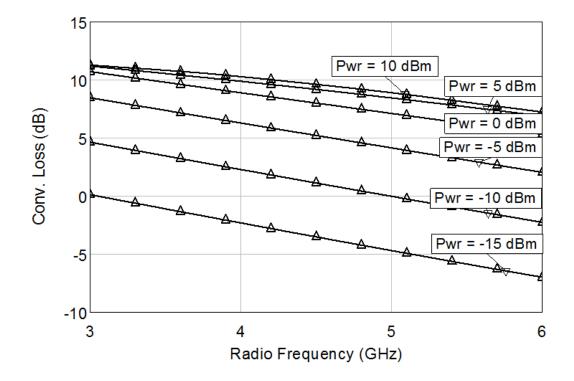

|                                           | Passive Mixer Conversion Loss vs Frequency Post-layout Result Passive Mixer with Active Balun, Gain and Noise Figure vs LO Power                     |     |

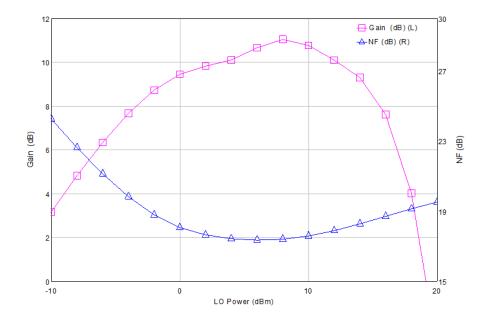

| 5 19                                      | Post-layout Result                                                                                                                                   |     |

| 0.13                                      | Measured Passive Mixer Linearity                                                                                                                     | 80  |

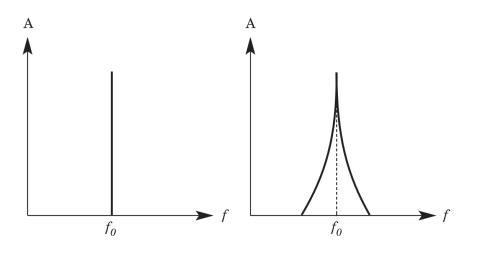

| 6.1                                       | An Ideal, Noiseless Signal has a Single Spectral Line (left); The Addition<br>of Phase Noise Results in a Signal with Modulation Sidebands Extending | 01  |

| ເຄ                                        | above and below the Nominal Centre Frequency (right)                                                                                                 |     |

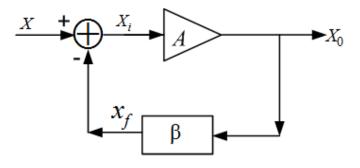

| 6.2                                       | Basic Oscillator Feedback Model                                                                                                                      |     |

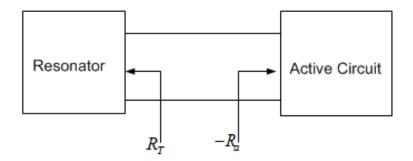

| $\begin{array}{c} 6.3 \\ 6.4 \end{array}$ | One-port Network View of an Oscillator                                                                                                               |     |

| $\begin{array}{c} 0.4 \\ 6.5 \end{array}$ | MOS Varactor VCO                                                                                                                                     |     |

| 0.5<br>6.6                                | Fabricated MOS Varactor VCO Micrograph                                                                                                               |     |

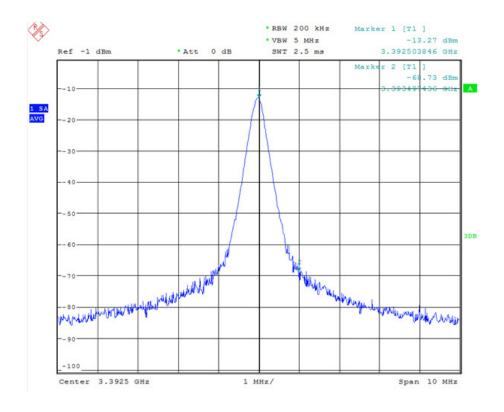

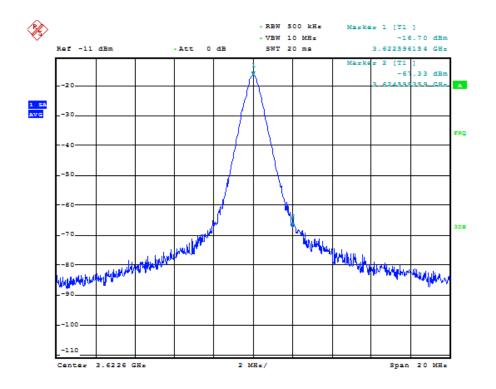

| 6.7                                       | Measured Power Spectrum of the MOS Varactor VCO                                                                                                      |     |

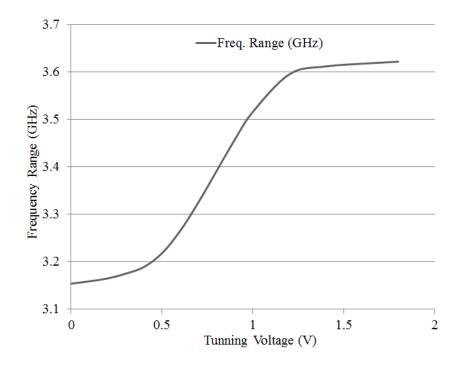

| 6.8                                       | Measured Frequency Tuning Range of the MOS Varactor VCO                                                                                              |     |

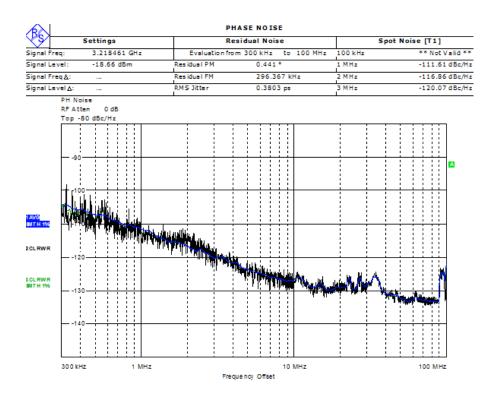

| 6.9                                       | Measured Prequency Tuning Italge of the MOS variactor VCO Measured Phase Noise of the MOS Variactor VCO is -109 dBc/Hz at 1MHz                       | 100 |

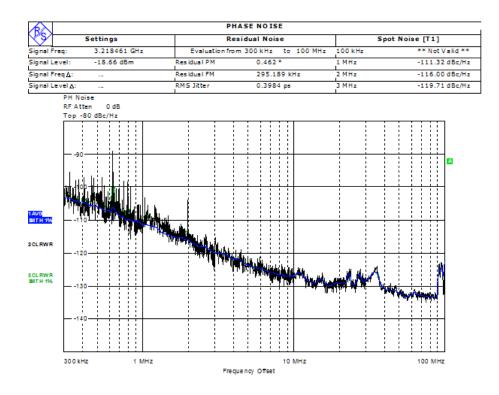

| 0.9                                       | Offset                                                                                                                                               | 104 |

| 6.10                                      | Measured Phase Noise of the MOS Varactor VCO is -118 dBc/Hz at 2MHz                                                                                  | 104 |

| 0.10                                      | Offset                                                                                                                                               | 105 |

| 6.11                                      | Automated Measured Phase Noise of the MOS Varactor VCO at Different                                                                                  | 100 |

| 0.11                                      | Offset                                                                                                                                               | 106 |

| 6.12                                      | Automated Measured Phase Noise of the MOS Varactor VCO at Different                                                                                  |     |

|                                           | Offset                                                                                                                                               | 106 |

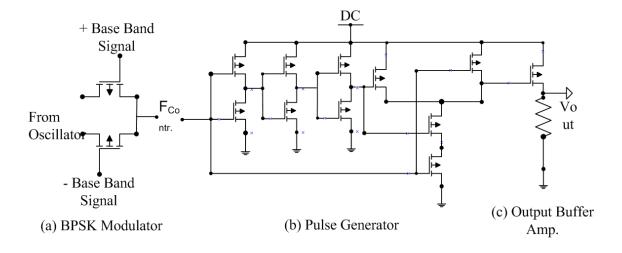

| 6.13                                      | Pulse Generator Circuit                                                                                                                              |     |

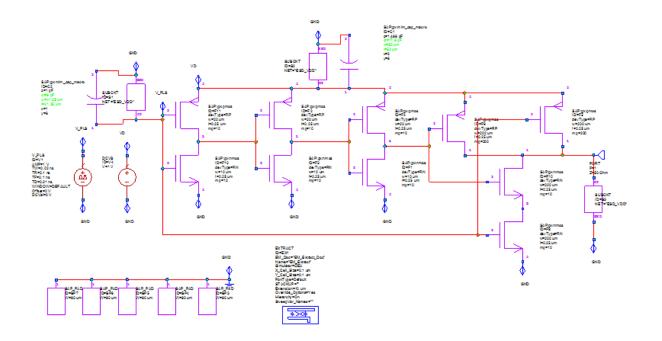

|                                           | Schematic of Designed Pulse Generator Circuit in AWR                                                                                                 |     |

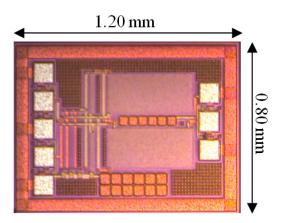

|                                           | Pulse Generator Micrograph                                                                                                                           |     |

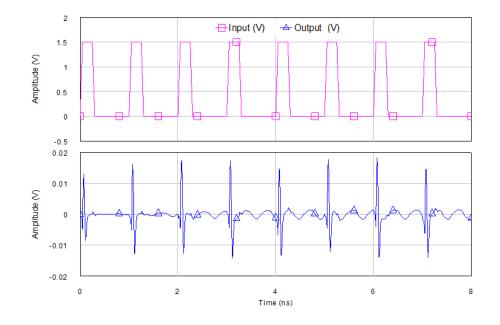

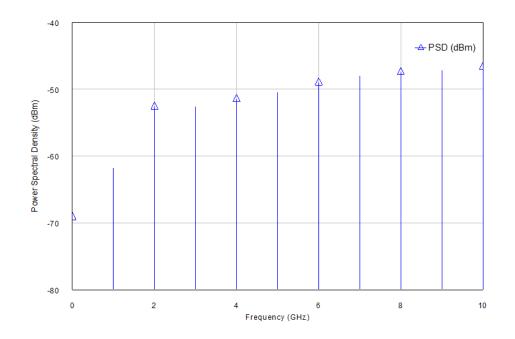

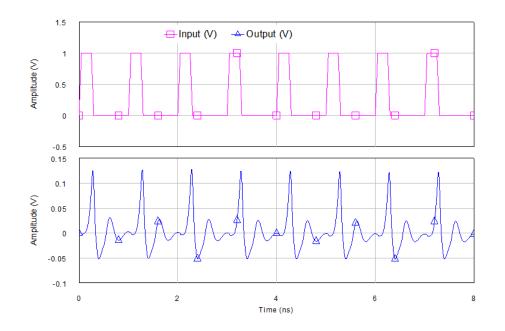

| 6.16                                      | Simulated Gaussian Monocycle Pulse of the Pulse Generator                                                                                            | 115 |

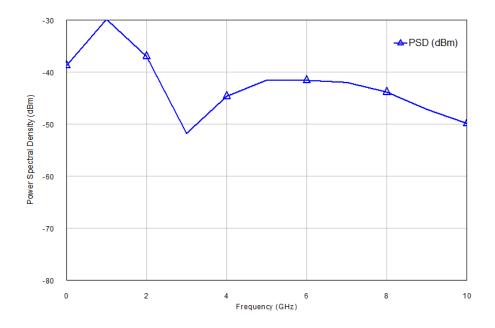

| 6.17                                      | Simulated Power Spectral Density of the Pulse Generator                                                                                              | 115 |

|                                           |                                                                                                                                                      |     |

| 7.1                                       | The Receiver Architecture                                                                                                                            |     |

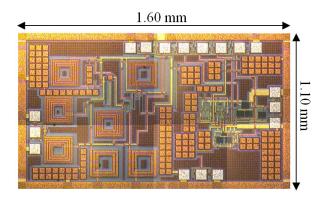

| 7.2                                       | Micrograph of Receiver with Active Mixer                                                                                                             |     |

| 7.3                                       | Micrograph of Receiver with Passive Mixer                                                                                                            |     |

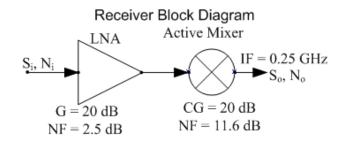

| 7.4                                       | Receiver with Active Mixer Chain                                                                                                                     | 122 |

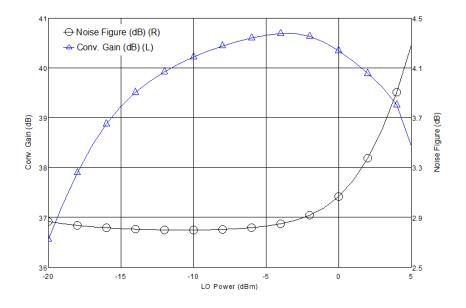

| 7.5                                       | Receiver with Active Mixer: Conversion Gain vs LO Power and Noise                                                                                    | 100 |

| -                                         | Figure vs Lo Power Post-layout Result                                                                                                                |     |

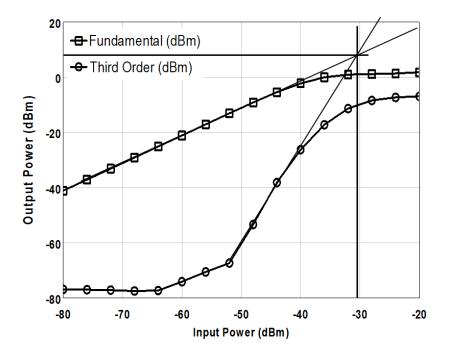

| 7.6                                       | Receiver with Active Mixer: Measured Linearity                                                                                                       |     |

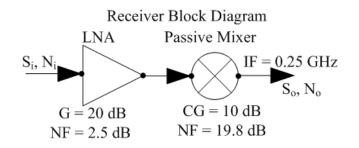

| 7.7                                       | Receiver Chain with Passive Mixer                                                                                                                    | 124 |

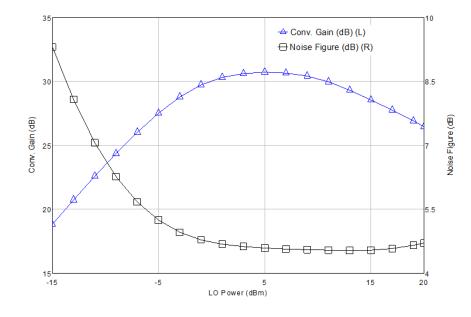

| 7.8                                       | Receiver with Passive Mixer: Conversion Gain vs LO Power and Noise                                                                                   | 105 |

| 7.0                                       | Figure vs LO Power Post-layout Result                                                                                                                |     |

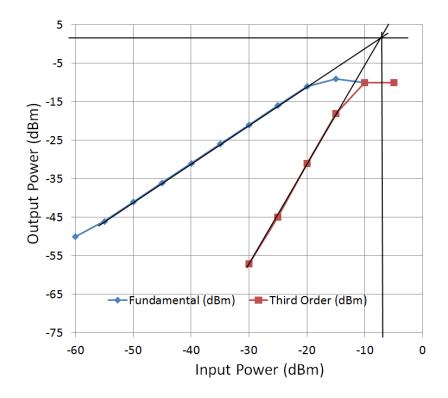

| 7.9                                       | Receiver with Passive Mixer: Measured Linearity                                                                                                      | 125 |

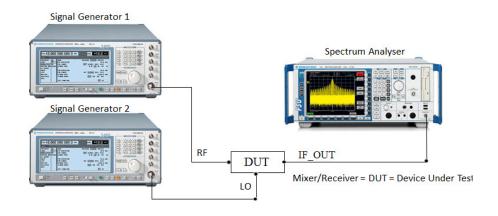

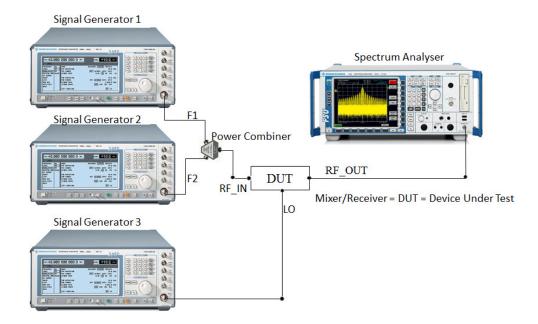

| 7.10 | Measurement Setup for Mixer/Receiver Gain           |

|------|-----------------------------------------------------|

|      | Measurement Setup for Mixer/Receiver Linearity      |

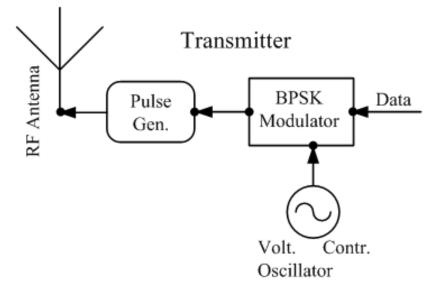

|      | Proposed IR-UWB Transmitter Block Diagram           |

| 7.13 | Simulated Gaussian Monocycle Pulses                 |

| 7.14 | Simulated Power Spectral Density of the Transmitter |

| D 1  |                                                     |

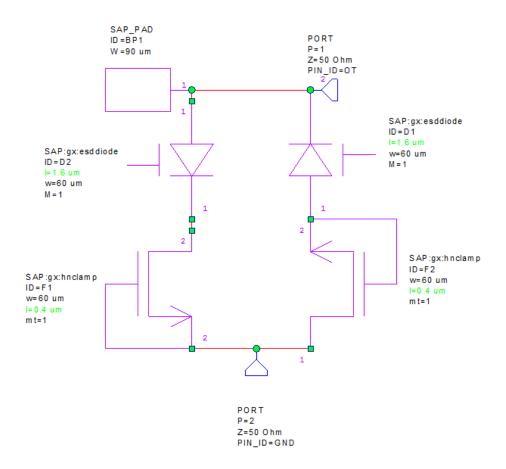

| В.1  | ESD Circuit Schematic                               |

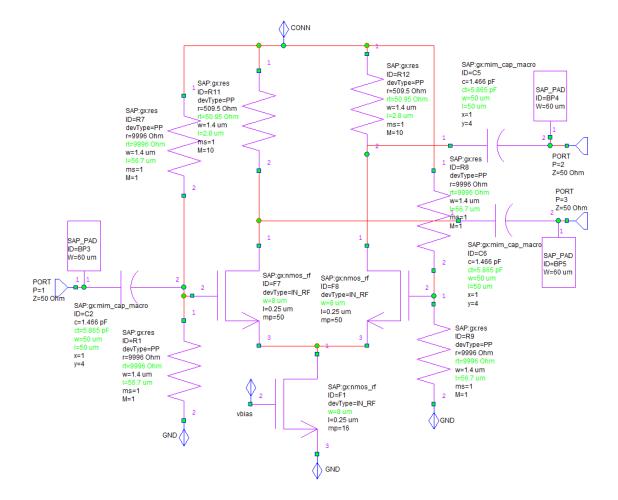

| B.2  | LO and RF Balun Circuit Schematic                   |

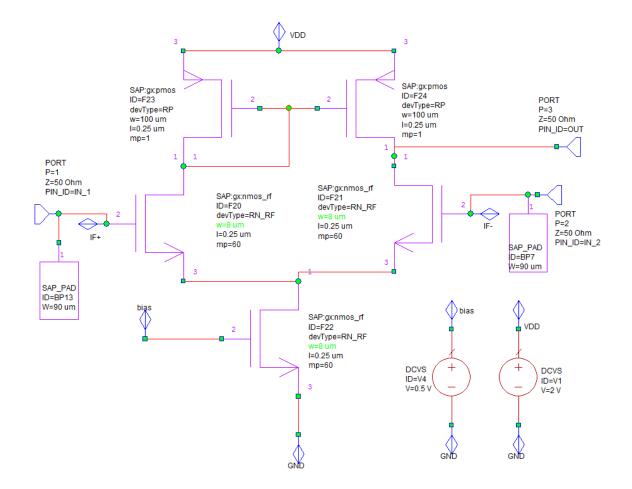

| B.3  | IF Balun Circuit Schematic                          |

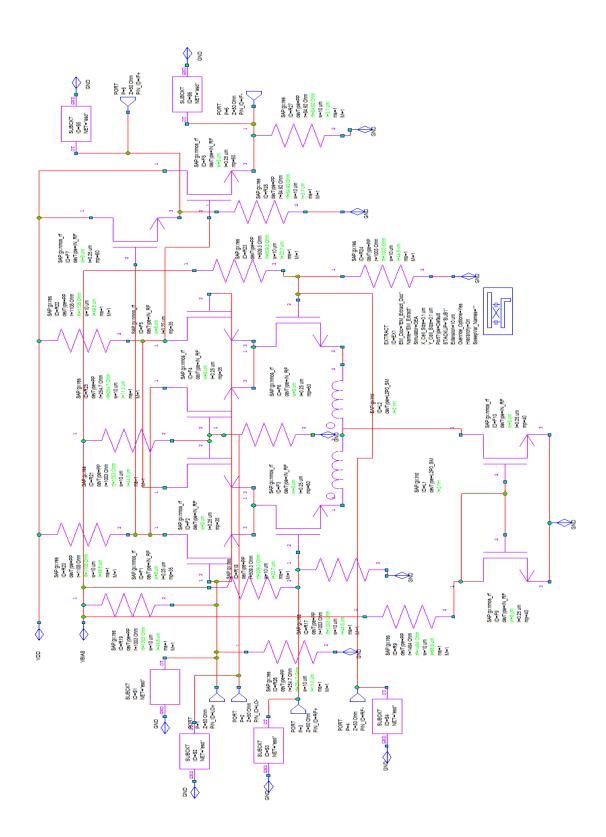

| B.4  | Core Gilbert Cell Mixer Circuit Schematic           |

| B.5  | VCO Circuit Schematic                               |

| B.6  | LNA Circuit Schematic                               |

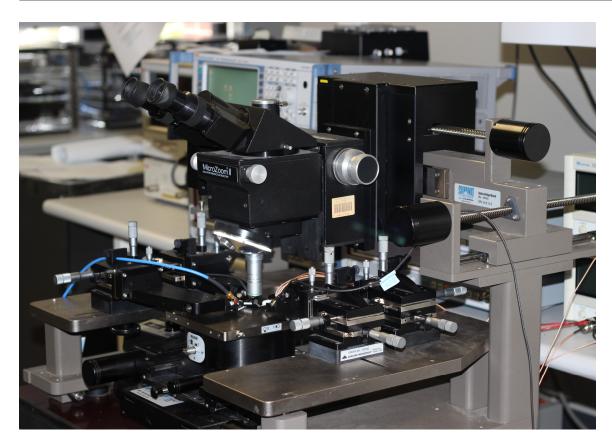

| B.7  | Probe Station and Equipment                         |

| B.8  | Wafer Micrograph                                    |

#### $\mathbf{x}\mathbf{x}\mathbf{i}\mathbf{i}\mathbf{i}$

# List of Tables

| 2.1          | Transistor Type Descriptions [2]                                                                                    | 27  |

|--------------|---------------------------------------------------------------------------------------------------------------------|-----|

| $3.1 \\ 3.2$ | Dielectric Properties of Human Intestine: A Worst-case Scenario [3]<br>Link Budget for the Proposed UWB Transceiver |     |

| 4.1          | Performance Summary and Comparison with State-Of-The-Art CMOS Wide-<br>band LNAs                                    | 62  |

| 5.1          | Performance Summary and Comparison with State-Of-The-Art CMOS Wide-<br>band Mixers                                  | 87  |

| 6.1          | Performance Summary and Comparison with State-Of-The-Art CMOS Wide-<br>band VCO                                     | 109 |

| 7.1          | Summary and Comparison with State-Of-The-Art CMOS Wideband Receivers                                                | 128 |

## Chapter 1

## Introduction

### 1.1 Motivation

The emergence of wireless communication has called for new developments and presented increasingly challenging requirements for improvements of the required technology and to foster more convenience to its users and consumers. However, today, challenges include development of a communication device suitable for implant inside the human body for video streaming and telemetry. The technology required to achieve this involves availability of high data access, long battery life, localisation and tracking capabilities, and applications offering un-disrupted service across different networks. As more devices rely on wireless, new technologies are presently facing spectral crowding and the coexistence of wireless devices is a major issue. Considering the limited bandwidth available and accommodating the demand for high data rates is a major task which requires substantive technology that can coexist with devices operating in various frequency bands. Ultra-Wideband technology is a potential candidate for the proposed implantable design; the IEEE TG 802.15.4a group has drafted several proposals for this technology and its implementation such that the carrier of the implantable devices or its user will be free from other forms of hazards including electromagnetic radiation or electrical burns from the device component sub-assembly such as antenna or electronic components. These new developments in the world of wireless technology have improved medical technology and engineering, enabling the doctor or medical practitioner to have access inside the human body as many times as they want without the need for surgical operations, as technology has led to implantable wireless radios suitable for communication and video streaming inside the human body, using the unlicensed Ultra-Wideband frequency band.

### 1.2 Overview of Ultra-Wideband Technology

The majority of the initial concepts and patents for Ultra-Wideband (UWB) technology originated in the late 1960s at the Sperry Research Center (Sudbury, MA), then part of the Sperry Rand Corporation, under the direction of Dr Gerald F. Ross. At that time, this technology was alternatively referred to as baseband, carrier-free or impulse. The term "ultra-wideband" was not applied to this technology until 1989 according to [4]. Thus, by the early 1970s the basic designs for UWB signal systems were available and there remained no major impediment to progress in perfecting such systems. After the 1970s, the only innovations in the UWB field would come from improvements in particular instantiations of subsystems, but not in the system concept itself. The basic components were variously known, e.g., pulse-train generators, pulse-train modulators, switching pulse-train generators, detection receivers and wideband antennas. Moreover, particular instantiations of the subcomponents and methodologies were also known, e.g., avalanche-transistor switches, light-responsive switches, use of "sub-carriers" in coding pulse trains, leadingedge detectors, ring demodulators, monostable-multivibrator detectors, integrating and averaging matched filters, template signal-match detectors, correlation detectors, signal integrators, synchronous detectors and antennas driven by a stepped-amplitude input [5].

The pioneering work of Harmuth, Ross, Robbins, van Etten, and Morey [4] defined UWB systems and did so in a very practical manner. Others have contributed to particular instantiations of the subsystems described by these pioneers but, after these pioneering contributions, no one can, or should, lay claim to have invented the field of UWB radio, radar or communications, nor to have invented a particular component or components which made it practical. There never was a time such that a particular subcomponent invention was required for UWB systems to become possible, except, perhaps, the sampleand-hold oscilloscope. In the commercial arena, UWB systems have been utilised and commercialised beginning in the 1970s according to [5].

Today UWB communications has developed such that some of its characteristics have presented great advantages over traditional narrowband systems. The advantages of UWB emanate from Shannon's channel capacity formula which states that the capacity of a channel increases linearly with bandwidth and logarithmically with an increased signalto-noise ratio (SNR). The Shannon's capacity formula can be stated mathematically as follows:

$$C = B \log_2(1 + \text{SNR}) \tag{1.1}$$

From Shannon's capacity formula, it can be deduced that UWB communications has the capacity to offer both high-data-rate communications over short distances and low-data-rate communications over long distances. Hence, when the bandwidth is extremely large, only a very small signal power is needed to achieve a high data rate. This property offers a UWB system better performance than narrowband systems. UWB signals are also localised in the time domain, which enables precise location and ranging capabilities [6].

### 1.3 Ultra-Wideband Standards

Ultra-Wideband physical layer systems standards have been defined by the Institute of Electrical and Electronics Engineers (IEEE) for various usages. The IEEE 802.11 Task Group is responsible for Wireless Local Area Network (WLAN) standards and IEEE 802.15 is responsible for Wireless Personal Area Network (WPAN). UWB technology emerged as a potential solution for the IEEE 802.15.3a standard for WPAN, targeting high-data-rate, short-range multimedia applications. The UWB technology for 802.15.3a uses one or more carrier frequencies modulated by a baseband signal, which is essentially an extension of conventional narrowband wireless technology. However, UWB technology has also been adopted at the physical layer by the 802.15.4a low-data-rate task group. The IEEE 802.15.4a low-data-rate physical layer (PHY) Task Group for personal Area Networks (WPAN) was established in March 2004 to develop an alternative PHY to amend 802.15.4. The principal interest is in providing communications and high precision ranging/location capability (1 metre accuracy and better), high aggregate throughput, and ultra-low power, as well as adding scalability to data rates, longer range, and lower power consumption and cost. These additional capabilities over the existing 802.15.4 standard are expected to enable significant new applications and market opportunities [7]. The IEEE 802.15.4a Task Group selected a baseline specification with two optional PHYs consisting of (a) UWB impulse radio and (b) Chirped spread spectrum in the 2.4 ISM band. In contrast to IEEE 802.15.4 (low data rate), it is expected that UWB impulse radio will be able to deliver both communication and precision ranging.

### 1.3.1 IEEE 802.15.6 Task Group

Today, Task Group 4a has been further modified to IEEE 802.15 Task Group 6 (WBAN), with a standard suitable for real-time health monitoring of a patient and diagnosing many

life threatening diseases. Task Group 6 (WBAN) standard applies in close vicinity to, on, or inside a human body and supports a variety of medical and non-medical applications.

The IEEE 802.15.6 standard for WBAN has been ratified. The purpose of the standard is to define a communication system optimised for low-power in-body/on-body nodes (but not limited to humans) to serve a variety of medical and non-medical applications including consumer electronics/personal entertainment and others [8]. The baseline specification for Task Group 6 (WBAN) impulse radio covers the (3.1 - 4.6) GHz range and offers data rates of up to 10 Mbps.

### 1.3.2 Impulse Radio-Based UWB System

UWB technology has its origins in impulse radio, which has been studied since the early 1960s. In recent years, impulse based radio experienced a revival due to its promising properties for short range, low power and high speed applications [9]. It was also noted that the first efficient radio transmissions were performed on the basis of impulse transmission.

The major benefit of impulse radio is its low complexity. Compared to conventional receivers, no power-consuming Phase Lock Loop (PLL) synthesizers are required. Due to the large bandwidth available, the demands for frequency accuracy are much more relaxed. Impulse radios are used to generate very short pulses directly from baseband without a carrier, with the corresponding spectrum extending from DC up to microwave frequencies. As a result of its extreme bandwidth, they are capable of reduced interference, resistance against jamming, enhanced encryption and low probability of interception. Potential modulation schemes for UWB impulse radio include On-Off Keying (OOK), Pulse Amplitude Modulation (PAM), Binary Phase Shift Keying (BPSK) and Pulse Position Modulation (PPM).

However the impulse based WBAN UWB radio has the following advantages: low

complexity, low power, relaxed phase noise requirements, lower sensitivity to multipath, lower interference level, position location capability, low probability of interception and lower susceptibility to interference. UWB signals have been demonstrated to propagate through certain obstructions that cannot be penetrated by conventional narrowband systems; this property shows that UWB has very strong penetrating power as demonstrated by through-the-wall imaging systems and ground penetrating radar [10].

It was also noted that UWB impulse radio systems are resistant to multipath fading compared to narrowband systems. In narrowband systems, the received multipath signals of a given symbol can overlap with a subsequent received symbol due to multipath delay; because multipath delays are less than the symbol duration, the received signal from multipath can add either constructively or destructively. Whereas, for pulse based UWB radio the multipath delay is longer than the pulse width, such that the received pulse due to multipath can be resolved. Since the multipath delay is shorter than the time between two consecutive pulses, no overlap will occur between the multipath signals of the two symbols.

An impulse radio transmitter structure consists of a pulse generator, a timing circuit and a clock oscillator [10]. The desired waveform is produced by the pulse generator, while the clock oscillator defines the pulse repetition frequency. Step, Gaussian or Monocycle pulses are suited for UWB communication since they have a broadband frequency spectrum [11]. Hence, with ultra-short time domain pulses, impulse radio based UWB systems transmiting with a very short pulse duration (say nanoseconds) are similar to those used in radar. Impulse radio transmitters are less complex since no sophisticated filters are required. Power consumption is very low since the output power is restricted to avoid for interference with other standards.

## 1.4 Update on UWB CMOS Transceiver Design

Behzad *et al.* [12] present a UWB CMOS transceiver for multiband OFDM applications. The circuit consumed 105 mW of DC power, with a data rate of 480 Mbps. The circuit architecture in the design is more complex than for impulse radio (IR) and hence it consumes more energy. On the other hand, the CMOS process used in this design is more advanced.

Chi *et al.* [13] present a low power wireless transceiver analogue front end for an endoscopy capsule system. This design is not UWB since it operates at 2.5 GHz, the circuit consumes 29 mW of DC power, and the data rate is 1 Mbps.

A new development came in 2008 when a UWB system for wireless endoscopy emerged; as presented in [14] this work enables real-time diagnosis with high-resolution images. A non-coherent transmitted reference (TR) UWB architecture with differential binary phase shift keying (DBPSK) modulation, it uses the IEEE 802.15.4a channel model. The data rate is 125 Mbps; This work has shed more light on UWB transceiver design for implants. The transmitter in this design is all digital whereas digital circuits at these clock rates are power hungry compared to analogue circuits. Analogue circuits are considered when designing for low power applications.

Another work on CMOS IR-UWB transceiver design is presented in [15]; the proposed architecture in this work composed of a simple and robust design using a Gaussian monocycle impulse generator at the transmitter. The data rate is up to 5 Gbps and consumes 9 mW of power. This design is built on a more advanced 90nm CMOS technology. The transmitter modulation scheme is OOK, which is not as efficient as BPSK.

In 2011, another article on an IR-UWB transceiver was published [16]; this work exploits 6 - 10 GHz of the UWB band to achieve a higher data rate of 2 Gbps. The modulation scheme here is BPSK, due to its simplicity and energy efficiency, as a solution suitable for short-range wireless applications. The circuits are designed on 130nm CMOS technology. Another publication in 2011 by Solda *et al.* [17] presented an IR-UWB transceiver operating in a similar frequency range as in [16]; the frequency band here is 7.25 - 8.5 GHz and the data rate is 5 Mbps. The circuit is built on  $0.13\mu$ m CMOS technology.

Following the analysis of previous work on UWB transceiver design and their techniques for low power applications, there are various challenges associated with implementation, which include frequency of operation, modulation scheme, power consumption, circuit architecture etc. The proposed IR-UWB transceiver design in this project has been designed to strike a balance to achieve the design goals with limited resources available. A 3 - 5 GHz IR-UWB transceiver has been proposed using less complex circuitry, hence low power and a better transmit coverage area. The proposed transmitter is based on a BPSK modulator and the circuit is built on  $0.25\mu$ m SOS process technology.

## 1.5 Author's Contributions

WBANs require short range, low power and highly reliable wireless communications for use in close proximity to or inside the human body. WBANs are divided into two categories depending on their operating environment: one is a wearable WBAN which mainly operates on the surface or vicinity of the human body and the other is called an implantable WBAN which operates inside the human body. This project has focused on how to make a simple and effective UWB impulse-radio RF front end, comprised of low complexity circuits at low power consumption, suitable for a high data rate. The circuits are designed for an implantable RF front end.

Impulse radio UWB (IR-UWB) promises a significantly higher data rate in low cost, low power wireless applications than conventional narrow-band systems, IR-UWB systems can have much simpler architectures and are more versatile under various channel conditions. However, there are two important challenges in building an IR-UWB system:

- I Ability to achieve large signal bandwidth, or, the ability to generate and process pulses with sub-nanosecond time resolution.

- II Ability to accomplish this with low power consumption and low circuit complexity, which translate into low cost.

This work was designed on a  $0.25\mu$ m CMOS process silicon-on-sapphire (SOS), which is one of the silicon-on-insulator (SOI) semiconductor manufacturing technologies. It is primarily used in aerospace and military applications because of its inherent resistance to radiation. This property makes it suitable for implantable medical electronics which we are explored in this work.

The main advantage for the electronic circuit in this project is the highly insulating sapphire substrate which prevents stray currents caused by EM coupling from spreading to nearby circuit elements. The benefit of the insulating substrate is its very low parasitic capacitance, which provides increased speed, low power consumption, better linearity and more isolation than bulk silicon. SOS has seen relatively little commercial use because of the difficulties in fabrication; they are very small transistors used in modern highdensity applications. Because sapphire is a highly insulating substrate there is almost no parasitic capacitance. This provides a wide range of benefits in designs targeting RF, mixed signal/analogue and radiation hard applications.

Following the above devices properties, the author has designed transceiver RF frontend sub-circuits optimised for low power and low complexity.

### 1.6 Synopsis

This thesis is organised as follows; Chapter 1 introduces the general concept and technology required for the work in this thesis. The design of wireless radio for Ultra-Wideband applications is discussed. A low power circuit design suitable for implantable radio is identified as a major obstacle. The aim of this thesis is to design low power circuits capable of a high data rate for implantable wireless applications.

Chapter 2 presents a comprehensive discussion on UWB transceiver architecture, analysing how to make a simple transceiver design, with low power consumption. Included in Chapter 2 are the device properties and characteristics.

Chapter 3 presents the link budget of the transceiver RF front-end design constraint as well as the requirements for the proposed transceiver. This helps to point out the requirements of the individual circuits to be designed and to maximise efficiency with low power design. A paper was published as a result of the review work in Chapter 2 and Chapter 3 as:

Iji Ayobami, Forest Zhu and Michael Heimlich, "Proposed Ultra-Wideband System and Receiver Circuit for Implant Wireless Body Area Networks", 12th International Symposium on Communications and Information Technologies (ISCIT), October, 2012.

Chapter 4 presents the building blocks for the receiver sub-circuits RF front end, this includes circuit structure, optimisation techniques for low power without much degradation in the required signal. Fabricated circuits and measured results are also presented. In this Chapter, the following papers have been published:

Iji Ayobami, Forest Zhu and Michael Heimlich, "Low Power, High gain, Low Noise Amplifier (LNA) for Ultra-Wideband Applications", *Microwave and Optical Technology Letters*, Vol. 55, Issue 12, February, 2013,

Iji Ayobami, Forest Zhu and Michael Heimlich, "A 3 - 5 GHz LNA in  $0.25\mu$ m SOI CMOS Process for Implantable WBANs", 55th Int'l Midwest Symposium on Circuits and Systems (MWSCAS), August, 2012,

Iji Ayobami, Forest Zhu and Michael Heimlich, "High Gain/Power Quotient Variable-Gain Wideband LNA for Capsule Endoscopy Application", *Microwave and Optical Technology Letters*, Vol. 54, Issue 11, November 2012,

and

Iji Ayobami, Forest Zhu and Michael Heimlich, "A 4.5 mW 3 - 5 GHz Low-Noise Amplifier in 0.25μm Silicon-on-Insulator CMOS Process for Power -Constraint Application", *Microwave and Optical Technology Letters*, Vol. 55, Issue 1, January 2013.

For chapter 5, in the receiver chain the next block to the LNA is the mixer. A down converter mixer, both an active and a passive type, for low power applications has been designed, with much design effort expended to achieve better linearity. The following papers have been published:

Iji Ayobami, Forest Zhu and Michael Heimlich, "A Down Converter Active Mixer, in 0.25μm SOI CMOS process for Ultra-Wideband Applications", International Symposium on Communications and Information Technologies (ISCIT), October, 2012.

and

Iji Ayobami, Forest Zhu and Michael Heimlich, "A Folded-Switching Mixer in SOI CMOS Technology", 55th Int'l Midwest Symposium on Circuits and Systems (MWSCAS), August, 2012.

Chapter 6 presents the building blocks for the transmitter RF front end sub-circuits, this includes voltage-controlled oscillator and pulse generator circuit structure, optimisation for low power, design method, fabricated circuits and measured results. A paper has been published on this work as: Iji Ayobami, Forest Zhu and Michael Heimlich, "Design of Low Power, Wider Tuning Range CMOS Voltage Controlled Oscillator for Ultra-Wideband Applications", *IEEE International Conference on Integrated Circuits Design and Technology (ICICDT)*, May, 2012.

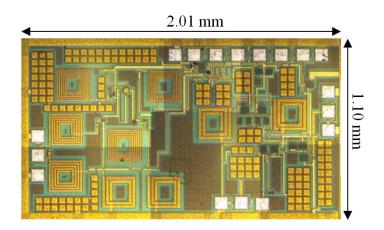

Chapter 7 presents the transceiver front end, divided into receiver and transmitter. The receiver circuit is made up of the LNA and Mixer cascaded while the transmitter is simply the pulse generator and the VCO cascaded to produce UWB pulses. On this work a journal paper has been written and submitted as:

Iji Ayobami, Forest Zhu and Michael Heimlich, "Low Power, Highly Linear, 3.1 - 5 GHz UWB Receiver for Implantable WBAN Applications", *Submitted* to IEEE Transactions on Circuit and Systems (TCASII).

Chapter 8 is the concluding chapter; summaries of the system design are made as well as suggestions for future research. Also details of experience gained during the PhD program are listed. All equations and schematic diagrams relevant to Chapters 2 to 7 can be found in Appendices A and B respectively, while all abbreviations used in this thesis are in Appendix C.

# Chapter 2

# Background

## 2.1 Implantable WBAN Transceiver

Ultra-Wideband (UWB) technology is a promising technology for low cost, high data rate, short range, and low power consumption for wireless transmission. This technology was initially developed to solve problems related to short range communications. As technology advances, engineers design smaller and more compact communication devices for easy use and handling. The need for an implantable device is to be very small so that it will be easy for its user to carry without feeling its weight. There are various design issues that should be considered by the circuit design engineer to achieve better properties, as it requires specific design features. Hence, the circuit design topology must be carefully chosen as this determines the size and complexity of the entire design. This work has defined a simple transceiver structure suitable for implantable radio.

An implantable wireless technology has both benefits and challenges which need to be balanced. One of the chief obstacles to implanting wireless devices within the body is the deleterious effects of absorbed radio frequency energy. UWB technology is highly attractive for implantable Wireless Body Area Networks (WBAN) due to its ability to transmit less energy per Hz within a wide spectrum and at a high data rate. While narrowband communication systems contain their data within a fractional bandwidth of less than 1%, the UWB system uses 20% or more for the same data rate. Secondly, narrowband and other wideband systems use radio frequency carriers to move the signal from baseband to the carrier frequency. Being a carrier-less technology, the implementation of UWB, is somewhat simpler and, therefore, it can be smaller due to its low complexity. However, UWB implementations can still be challenging. To get the several GHz of bandwidth, UWB must directly modulate an impulse, typically with requirements for very sharp rise/fall time. UWB is currently targeted for use between 3 and 10 GHz where significant absorption within the body is found, therefore making receiver signal-to-noise ratios (SNR) a concern.

## 2.2 Application Requirements

Part of the requirements considered here for the proposed UWB implantable WBAN is to transmit video inside the human body. A typical UWB PHY and MAC layer device should support (640 width 480 height) a resolution of 8 bits per pixel, 3 (Red, Green, Blue) bits for colour (2 frames per second) frame rate, at a data rate of 9.8 Mbps. An additional 50 Kbps is needed for telemetry and 50 Kbps for future use such as controls and actuators. Hence, up to 10 Mbps is sufficient to support no-compression, real-time multimedia applications. The principal requirement, however, of WBANs is low emission due to the fact that it is within the human body (but not limited to humans); hence the emitted power must be as low as possible to avoid damage to organs or tissue. Careful consideration of the regulations are stipulated by the International Commission of Nonionizing Radiation Protection safety level (ICNIRP). The guideline includes the specific absorption rate (SAR) as the measure of energy absorption, which can be manifested as heat, and gives a measure of the internal fields which could affect the biological system without heating (non-thermal interactions). The SAR is the rate at which radiation energy is absorbed by tissue per unit weight, and should be referred to as a maximum level. At 3 - 5 GHz, SAR should be  $3.23 \times 10^{-6} (W/Kg)$  [18]. The low emission level means that the interference level of WBANs should be reasonably low so that it could be tolerable and tolerant of other wireless systems and serve as a short range communication technology [19]. Other design requirements for WBANs include high security and large scalability. WBANs require short range, low power and highly reliable wireless communications for use in close proximity to or inside the human body. WBANs are divided into two categories depending on their operating environment; one is a wearable WBAN which mainly operates on the surface or in the vicinity of the human body and the other is called an implantable WBAN which operates inside the human body [20].

## 2.3 UWB Standardisation and Spectrum Regulation

The Federal Communication Commission (FCC) spectral mask was released in February 2002 as 'The First Report and Order' (RO). The RO allowed commercialisation of UWB technology if the UWB design radiation adheres to the spectrum mask. A UWB signal has been defined as a signal whose fractional bandwidth,  $B_f$ , is greater than 0.25, where the definition of  $B_f$  is as follows:

$$B_f = 2\frac{f_h - f_l}{f_h + f_l}$$

(2.1)

where  $f_h$  and  $f_l$  are the higher and lower -10dB frequencies, respectively [21]. A signal is defined as being UWB if the -10dB signal bandwidth is 500 MHz or larger [22]. The existing FCC radiation limits for different indoor and outdoor UWB applications are presented in Figure 2.1; the Part 15 limit was included as reference, and permits the operation of authorised low-power radio-frequency (RF) devices without a licence from the Commission or the need for frequency coordination under general emission limits [23]. According to the FCC Indoor Mask Part 15, for indoor emission, the maximum effective isotopic radiated power (EIRP) level in the 3.1 - 10.6 GHz band is set to -41.3 dBm/MHz. All UWB devices must meet this spectral mask for legal operation.

Figure 2.1: Spectrum Mask of UWB for Indoor Environments

The IEEE 802.15.6 Task Group 6 standards for WBAN's physical layer (PHY) operates in two frequency bands: low band and high band. Each band is divided into channels; both of them are characterised by a bandwidth of 499.2 MHz. The low band consists of 3 channels 1 - 3 only, and it ranges from 3.1 - 4.6 GHz.

### 2.4 UWB Transceiver Architecture

This project is focused on implantable WBANs, whose basic function is to provide an effective and reliable network for transmission of data such as video through wireless communication links. WBANs can be used to provide assistance for automatic medical treatment, automated dosing and vital signal monitoring. The author considers implantable WBANs for video and other medical monitoring, in a situation where the device will be installed inside the human body to monitor in-situ, dynamic health related issues. As such, key considerations are signal propagation in terms of SAR and spectral mask, circuit implementation in terms of link budget, and overall performance over time as characterised by DC power.

The UWB definition by the FCC gives radio designers the opportunity to employ two different methods to design UWB systems: Impulse-Radio (IR-UWB) and Multi-Carrier based (MC-UWB). IR-UWB has a less complex hardware implementation, less demanding digital processing and greater resiliency to multipath fading effects. Hence, its simple implementation results in low power consumption and simple radio frequency (RF) circuitry. MC-UWB proponents claim greater spectral efficiency and flexibility, more efficient energy capture, but more complicated, bulky circuitry, and more power consumption. Hence, for implantable systems, low power consumption drives the focus of this work to IR-UWB, and then the proposed transceiver architecture is as shown in Figure 2.2. Furthermore, IR-UWB for communications is established by modulating an impulse waveform with sharp rise/fall times over the entire wide bandwidth. The pulse could last for several hundreds of picoseconds and have a bandwidth greater than 0.5

Figure 2.2: The UWB System for Implantable WBANs

GHz for more energy transfer. The Gaussian monocycle has been widely used for UWB design due to its appropriate mathematical properties and its good approximation to actual measurements. The pulse name (e.g. monocycle) simply means the number of zero crossing points in the time domain; for example Gaussian pulses do not cross the x-axis, while the Gaussian monocycle crosses the x-axis once. A train of Gaussian pulses without modulation causes discrete spectral lines with high peak power.

The human body is the medium for electromagnetic wave transfer in this work, hence we have to consider several issues related to the human body. The human body is not an ideal medium for radio frequency transmission. It is partially conductive and consists of materials of different dielectric constant, electrical conductivity, thickness, and characteristic impedance. Therefore, depending on the frequency of operation, the human body can lead to high losses caused by power absorption, centre frequency shift, and radiation pattern destruction. The absorption affects the magnitude with both frequencies of the applied field and the characteristics of the tissue.

The electromagnetic penetration depth is one of the major issues considered. This is the measure of how deep electromagnetic radiation can penetrate into a material. As investigated, blood has the least penetration depth compared to bone, fat and other organs as well as the relationship between frequency, conductivity and penetration depth of blood as analysed in [24]. Considering the amount of energy absorbed by the human body, it is necessary to recognise that the percentage of incident radiation which is actually absorbed depends on the frequency and the orientation of the subject related to the field. In human tissue, RF radiation may be absorbed, reflected, or may pass through the tissue; it depends on the body structure and the tissue interfaces involved. These interfaces are the interactions from tissue to tissue, or tissue - air - tissue and are clearly complex in the human body. The depth of RF penetration of the human body is also an important factor. Following the FCC standard, the effective isotropic radiated power is limited for this technology at - 41.3 dBm/MHz [19].

## 2.5 Selected IR-UWB Modulation Schemes

Of the various types of modulation schemes used for IR-UWB modulation, few selected ones including, PPM, PAM, OOK and BPSK modulation scheme will be discussed in this section.

### 2.5.1 Pulse Position Modulation

Pulse Position Modulation (PPM) is based on the principle of encoding information with two or more positions in time, a pulse modulation technique that uses pulses having uniform height and width but displaced in time from some base position according to the amplitude of the signal at the instant of sampling. Pulse position modulation has higher noise immunity since the UWB receiver detects the presence of a pulse at the correct time; the duration and amplitude of the pulse are not important [25].

### 2.5.2 Pulse Amplitude Modulation

Pulse Amplitude Modulation (PAM) is based on the principle of encoding information with the amplitude of the impulses and is the simplest form of pulse modulation that transmits data by varying the voltage or power amplitudes of individual pulses in a timed sequence of electromagnetic pulses. PAM can also be used for generating additional pulse modulations. In general, amplitude modulation is not the preferred way for most short-range communication. Furthermore, more power is required to transmit the higher amplitude pulse [25]

### 2.5.3 On-Off Keying

OOK is the simplest form of amplitude-shift keying (ASK) modulation that represents digital data as the presence or absence of a carrier wave. In its simplest form, the presence of a carrier for a specific duration represents a binary, one, while its absence for the same duration represents a binary, zero [25].

### 2.5.4 Binary Phase Shift Keying

Binary Phase Shift Keying (BPSK) is a type of phase modulation using two distinct carrier phases to signal ones and zeros. BPSK is the simplest form of PSK. It uses two phases which are separated by 180° and so can also be termed 2-PSK. It does not particularly matter exactly where the constellation points are positioned, just that they are 180° out of phase. This modulation is the most robust of all the PSKs since it takes serious distortion to make the demodulator reach an incorrect decision. In bi phase modulation, information is encoded with the polarity of the impulses,

BPSK has an advantage over the other types of modulations due to an inherent 3 dB increase in separation between constellation points [26]. BPSK modulator guarantees superior matching between positive and negative pulses and supports high data rates at low power consumption, since its functional operation is in the digital domain

Implantable WBAN systems are designed for low power in order to achieve long battery life. A simple and efficient modulation scheme will enhance low power design, but there are few modulation schemes that actually support low power architecture; these include On-Off Keying (OOK), Differential Phase Shift Keying (DPSK) and Binary Phase Shift Keying (BPSK). All the above mentioned modulation schemes are well known and have relative advantages in bandwidth efficiency, sidelobe reduction, and ease of implementation [27].

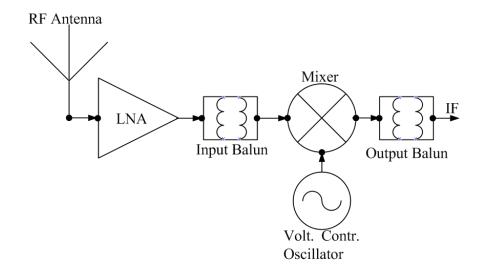

The choice of the modulation scheme affects the amount of smoothing; the author has chosen binary phase shift keying (BPSK) for modulation because its implementation is simpler, it has a better bit error rate, and it accommodates the bandwidth required, compared to QPSK and other modulation schemes. The UWB BPSK transmitter consists of a pulse generator, a voltage controlled oscillator (VCO) and a driving amplifier, as shown in Figure 2.2. The transmitter generates an amplitude modulated signal by translating a digital pulse train into monocycle shaped signals with binary information data emitted by an antenna. The receiver consists of a low noise amplifier (LNA), balun, a Mixer (down converter), and an analogue to digital converter (ADC). Weak pulse sequences on the receiver side are amplified by the LNA, and the output of the LNA is fed to the single ended to differential balun so that fully differential signals are generated. Then the generated differential signals are self-mixed to down convert the received RF signal to baseband. The down converted signal from the mixer is shaped by an ADC whose output is the recovered data. The pulse shape is sharp and is designed to concentrate energy over the broad range of 3.1 - 4.6 GHz at the -41.3 dBm/MHz power limit of the FCC spectrum mask of UWB. The important feature of the impulse-based transmitter is the absence of a power amplifier. The radio does not require intermediate frequency (IF) processing and this greatly reduces the transceiver complexity and overall power consumption. In an impulse radio receiver, the main function of the LNA is to achieve an input match to the impedance of the antenna for noise optimisation and in order to filter out-of-band interference. Subsequently a flat gain must be achieved over the entire bandwidth, as well as the minimum possible noise figure (NF) and low power consumption. The ADC will transfer signal processing to the digital domain and recover the information data for baseband digital signal processing.

# 2.6 The Proposed UWB WBAN Transceiver Design Requirements

In a WBAN system data transmission reliability and latency are extremely important. The reliability and latency of a WBAN will depend on the design of the physical and Medium Access Control layers (MAC). This layer determine the power consumption profile of a WBAN which is an important design issue. The MAC layer plays an important role in determining network efficiency and resource utilisation, which ultimately determines a system and the operating cost of a WBAN as mentioned in [28]. Also, a PHY layer could select appropriate modulation and coding techniques to combat transmission channel variability. The performance of a WBAN transceiver can be defined in term of its power efficiency.

#### **Power Efficiency**

Power management in a WBAN is a very important operational issue. Power usage can be minimised by optimising the PHY and MAC layer processes. A PHY layer can increase the probability of successful transmissions by selecting appropriate modulation and coding techniques. One attractive method of UWB signalling suitable for low power operation uses short pulses on the order of nanoseconds, to spread energy over at least 500 MHz of bandwidth. The baseband-like nature of this signalling promises a low cost, low power architecture because of the simplified analogue front-end design [29]. The power saving capability of this design is due to the elimination of frequency translation and synthesis, removal of filtering and reduction of external components.

A WBAN should be able to operate in a power constrained environment where power sources such as a battery could last for a longer period of time. Power optimization for the implantable nodes is critical in any design.

## 2.7 Design Process Technology