## Hardware implementation of Elliptic Curve Cryptography based on Residue Number Systems

By

MohamadAli Mehrabi

A thesis submitted to Macquarie University for the degree of Doctor of Philosophy Department of Department of Computing September 2020

ii

© MohamadAli Mehrabi, 2020.

Typeset in  $\[Mathbb{E}]{Typeset}$  2 $_{\mathcal{E}}$ .

Except where acknowledged in the customary manner, the material presented in this thesis is, to the best of my knowledge, original and has not been submitted in whole or part for a degree in any university.

MohamadAli Mehrabi

## Acknowledgements

I would like to thank my supervisors Dr Christophe Doche and Dr Alireza Jolfaei for their endless support and encouragement throughout my PhD candidature. Continuous encouragement, guidance, and feedback received from my supervisors helped me to achieve the milestones efficiently.

I am also thankful to my fellow group members for their friendly discussion and appreciation.

I wish to thank Naila Mukhtar for her help in the lab equipment preparation, ECC core testing, and side-channel power data gathering of the proposed ECC architectures.

I am thankful to the staff in the department of computing for their support. Finally, I would like to acknowledge Macquarie University for awarding me the Research Training Program Scholarship (RTP).

\_\_\_\_\_

## List of Publications

Published papers:

- Mohamad Ali Mehrabi, Christophe Doche, and Alireza Jolfaei, *Elliptic Curve Cryptography Point Multiplication Core for Hardware Security Module*, *IEEE Transaction on computers*, AUG. 2020.

- Mohamad Ali Mehrabi, Naila Mukhtar, and Alireza Jolfaei, *Side-channel power data analysis on RNS GLV ECC using Machine-Learning and Deep-Learning algorithms, ACM Transactions on Internet Technology*, SEP. 2020.

- Mohamad Ali Mehrabi and Christophe Doche, Low-Cost, Low-Power FPGA Implementation of ED25519 and CURVE25519 Point Multiplication, *Information*, vol. 10, no. 9, 285, 2019.

- Mohamad Ali Mehrabi, Improved sum of residues modular multiplication algorithm, *MDPI Journal of Cryptography*, vol. 3, no. 2, 14, 2019.

- Naila Mukhtar, Mohamad Ali Mehrabi, Yinan Kong, and Ashiq Anjum, Machine-Learning-Based Side-Channel Evaluation of Elliptic-Curve Cryptographic FPGA Processor, *MDPI journal of applied Sciences*, vol. 9, no. 1, 64, 2019.

Papers submitted for publication:

• Mohamad Ali Mehrabi and Alireza Jolfaei, *Efficient Cryptographic Hardware for Safety Message Verification in Internet of Connected Vehicles, ACM Transactions on Internet Technology*, Under Review.

## Abstract

In today's technology, a sheer number of Internet of things applications use hardware security modules for secure communications. The widely used algorithms in security modules, for example, digital signatures and key agreement, are based upon elliptic curve cryptography (ECC). In many IoT applications, such as intelligent transportation systems and distributed control systems, thousands of safety messages need to be signed and verified within a very short time frame. Considerable research has been conducted in the design of fast elliptic curve arithmetic on finite fields using residue number systems (RNS). This thesis investigates fast hardware implementations for RNS elliptic curve cryptography (ECC) co-processors. Our focus is to speed up the ECC point multiplication operation by exploiting the properties of the residue number system (RNS). The RNS consists of independent and carry-free small-sized integer channels that make it suitable for long-integer arithmetic. By harnessing the RNS properties, hardware parallelism, and utilising different point multiplication algorithms, we designed a low-latency ECC point multiplication co-processor for the standard elliptic curves SECP256K1, ED25519, and Brainpool256r1 which are widely used in the industry. This thesis contributes to the field of hardware cryptography as follows: Two new architectures for RNS modular reduction are proposed. The first improvement is on the RNS Montgomery reduction algorithm in which its FPGA implementation utilises fewer hardware resources and is also much faster in terms of speed compared to the literature. In addition to the RNS modular reduction algorithm, a new modular reduction based on the sum of residues (SOR) is proposed. The SOR algorithm is highly parallelisable. Two variants of the SOR algorithm with different levels of parallelism are implemented on FPGA. Furthermore, the elliptic curve group law operations are optimised for parallel computation and are used in the design of an RNS ECC co-processor. This thesis analyses the security of RNS GLV ECC co-processors with respect to side-channel, power data analysis by making use of machine and deep learning algorithms. Finally, suitable countermeasures are proposed to make such co-processors immune to side-channel attacks.

## Contents

| Acknowledgements         |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|--------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| List of Publications vii |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Ał                       | Abstract   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| С                        | onten      | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Li                       | st of      | igures xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                          | SLOI       | ables xvii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Li                       | st of      | ymbols xxi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Li                       | st of .    | cronyms xxiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                        | Intro      | duction 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 2                        | Bac        | ground 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                          | 2.1        | The residue number systems52.1.1The Chinese Remainder Theorem52.1.2Arithmetic operations in RNS6Elliptic Curve Cryptography102.2.1Elliptic Curves112.2.2The order of an Elliptic Curve112.2.3Isomorphism and twist of an Elliptic Curve122.2.4Endomorphism of Elliptic Curves122.2.5Group law on elliptic curves122.2.6Coordinate systems and group law132.2.7Elliptic Curve Discrete Logarithm Problem152.2.8Elliptic Curves152.2.9Edwards curves162.2.10Elliptic curves used in this research172.2.11Elliptic Curve Diffie-Hellman18 |  |  |  |

|                          | 2.3<br>2.4 | 2.2.11 Elliptic Curve Dillie – Hellman       18         2.2.12 Elliptic Curve Point Multiplication algorithms       18         Hardware design       25         2.3.1 FPGA architecture       26         2.3.2 FPGA design principles       30         2.3.3 Algorithm-Specific Optimisations       32         Side-channel attacks       33         2.4.1 Simple side-channel analysis       33                                                                                                                                       |  |  |  |

|                          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|   |                | 2.4.2 Differential side-channel analysis                                                                                                                                                                                                                    |           |

|---|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 0.5            | 2.4.3 Countermeasures against Side-Channel attacks                                                                                                                                                                                                          |           |

|   | 2.5            | Applications of Machine-learning and Deep-learning in side-channel analysis .                                                                                                                                                                               |           |

|   |                |                                                                                                                                                                                                                                                             | 40        |

|   |                | g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = g = |           |

|   |                | 2.5.3 Related works in the application of deep learning for side-channel attacks                                                                                                                                                                            | 45        |

| 3 | <b>RNS</b> 3.1 |                                                                                                                                                                                                                                                             | <b>47</b> |

|   | 3.1            | Introduction                                                                                                                                                                                                                                                |           |

|   | 3.2<br>3.3     | RNS Addition                                                                                                                                                                                                                                                |           |

|   | 3.4            | RNS Subtraction                                                                                                                                                                                                                                             |           |

|   | 3.5            | RNS Multiplication                                                                                                                                                                                                                                          |           |

|   | 0.0            | 3.5.1 Modular reduction                                                                                                                                                                                                                                     |           |

|   |                | 3.5.2 Implementation of RNS Multipliers                                                                                                                                                                                                                     |           |

|   | 3.6            | Improving RNS Montgomery modular reduction                                                                                                                                                                                                                  |           |

|   | 0.0            | 3.6.1 Hardware implementation of the Modified Montgomery reduction algorithm                                                                                                                                                                                |           |

|   | 3.7            | The Sum of residues modular reduction                                                                                                                                                                                                                       |           |

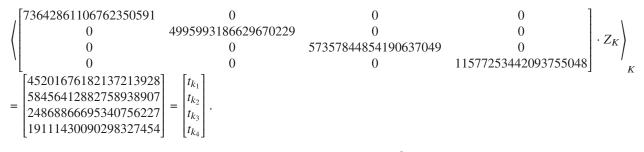

|   |                | 3.7.1 Calculation of $\kappa$                                                                                                                                                                                                                               |           |

|   |                | 3.7.2 The SOR algorithm hardware implementation and performance                                                                                                                                                                                             |           |

|   |                | 3.7.3 SOR performance                                                                                                                                                                                                                                       | 67        |

|   |                | 3.7.4 Hardware test and verification                                                                                                                                                                                                                        | 71        |

| 4 | RNS            | S Elliptic curve point multiplication Hardware design                                                                                                                                                                                                       | 79        |

| - | 4.1            |                                                                                                                                                                                                                                                             | 79        |

|   | 4.2            | New RNS ECC Point arithmetic Design                                                                                                                                                                                                                         |           |

|   |                | 4.2.1 Point arithmetic on Koblitz Curve SECP256K1                                                                                                                                                                                                           | 80        |

|   |                | 4.2.2 Point arithmetic on twisted Edwards curve ED25519                                                                                                                                                                                                     | 82        |

|   |                | 4.2.3 Point arithmetic on Brainpool256r1                                                                                                                                                                                                                    | 85        |

|   | 4.3            | RNS ECC arithmetic hardware architecture                                                                                                                                                                                                                    |           |

|   | 4.4            | Point multiplication state machines                                                                                                                                                                                                                         |           |

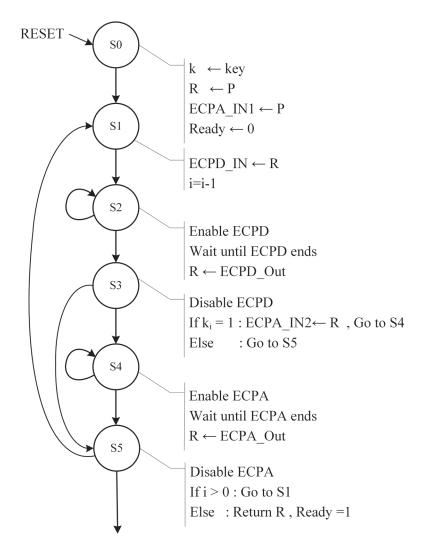

|   |                | 4.4.1 Double-and-add scalar multiplication state machine                                                                                                                                                                                                    |           |

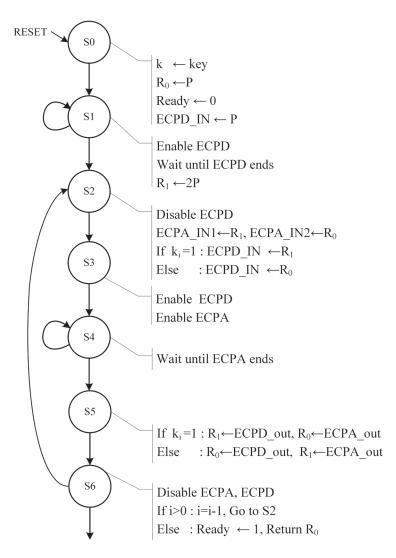

|   |                | 4.4.2 Montgomery ladder scalar multiplication state machine                                                                                                                                                                                                 |           |

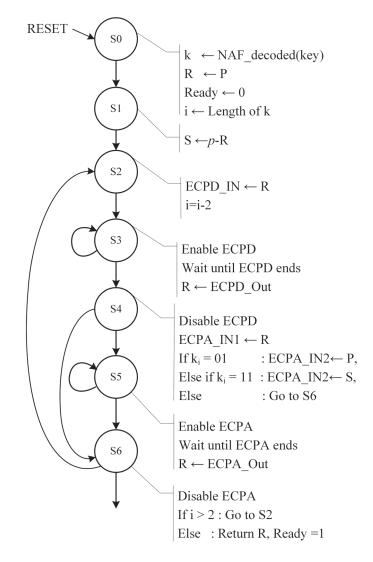

|   |                | 4.4.3 NAF method scalar multiplication state machine                                                                                                                                                                                                        |           |

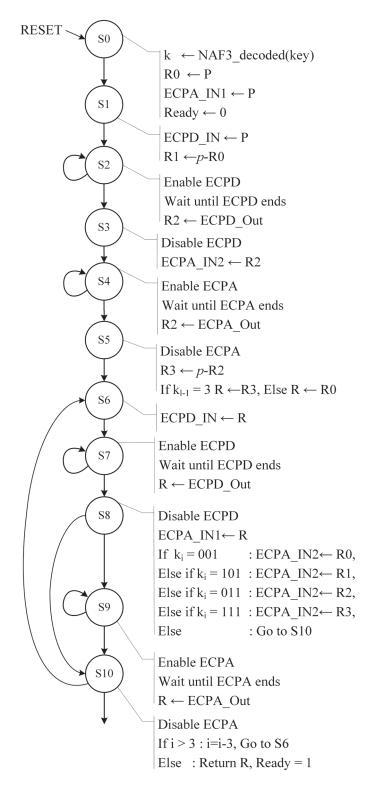

|   |                | 4.4.4 NAF <sub>3</sub> method scalar multiplication state machine                                                                                                                                                                                           |           |

|   |                | 4.4.5 DBC scalar multiplication state machine                                                                                                                                                                                                               |           |

|   | 4.5            | 4.4.6 GLV method scalar multiplication state machine                                                                                                                                                                                                        |           |

|   | 4.5<br>4.6     | Conclusion                                                                                                                                                                                                                                                  |           |

|   | 4.0            |                                                                                                                                                                                                                                                             | 01        |

| 5 |                |                                                                                                                                                                                                                                                             | 07        |

|   | 5.1            | Introduction                                                                                                                                                                                                                                                |           |

|   | 5.2            | Design of a low-cost RNS GLV ECC                                                                                                                                                                                                                            |           |

|   | 5.3            |                                                                                                                                                                                                                                                             |           |

|   |                | 5.3.1         Experimental setup         1           5.3.2         Methodology         1                                                                                                                                                                    |           |

|   | 5.4            | Applying Machine learning algorithms on side- channel power data                                                                                                                                                                                            |           |

|   | 0.1            | 5.4.1 Simple Machine-learning algorithms                                                                                                                                                                                                                    |           |

|   |                | 5.4.2 Design of a Fully-Connected DNN                                                                                                                                                                                                                       |           |

|   |                | - ·                                                                                                                                                                                                                                                         |           |

|     | 5.5<br>5.6               | 5.4.3 Design of a 1D-CNN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 119                                           |

|-----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|     | <b>Con</b><br>6.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>125</b><br>126                             |

| Α   | Арр                      | endix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 127                                           |

|     | A.1<br>A.2<br>A.3<br>A.4 | Maple program for testing proposed RNS Montgomery reduction algorithmMaple program for testing sum of residues reduction algorithm                                                                                                                                                                                                                                                                                                                                                                                           | 128<br>129                                    |

|     | A.5                      | Python code for creating training dataset from the raw side-channel power data                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|     | A.6                      | Python code for fully connected deep-learning model                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

|     | A.7                      | Python code for 1D-CNN Model 1 with two convolutional layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |

|     | A.8                      | Python code for 1D-CNN Model 2 with one convolutional layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 145                                           |

|     |                          | wendix B         VHDL package for RNS Montgomery reduction         Hardware description for RNS Motgomery reduction         RNS Package for SOR Mudular reduction algorithm         Hardware description for SOR_2 algorithm         Test and verification of SOR_2         B.5.1         Python program for generating random test vectors         B.5.2         Testbench for SOR_2         Hardware Description of RNS ECC point multiplication         Hardware Description of Low-cost RNS GLV ECC point multiplication | 157<br>163<br>183<br>191<br>191<br>192<br>194 |

| Rei | ferer                    | nces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 207                                           |

## List of Figures

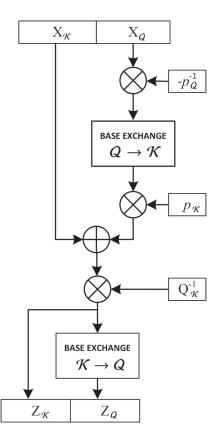

| 2.1  | Flow diagram of RNS Montgomery reduction algorithm                                                              | 10 |

|------|-----------------------------------------------------------------------------------------------------------------|----|

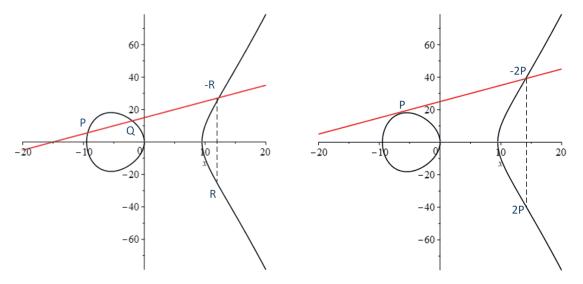

| 2.2  | Geometrically illustrated group law on elliptic curves on $\mathbb{R}$ .                                        | 13 |

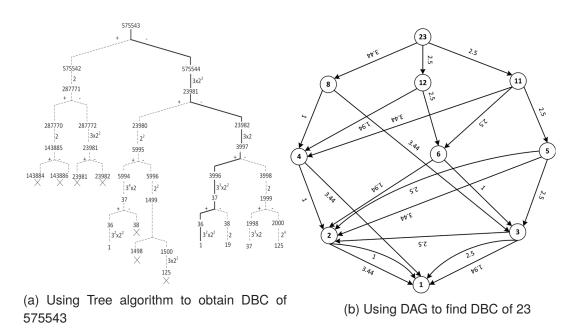

| 2.3  | Finding canonic DBC using Tree and DAG algorithms                                                               | 25 |

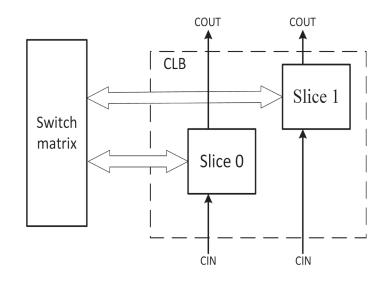

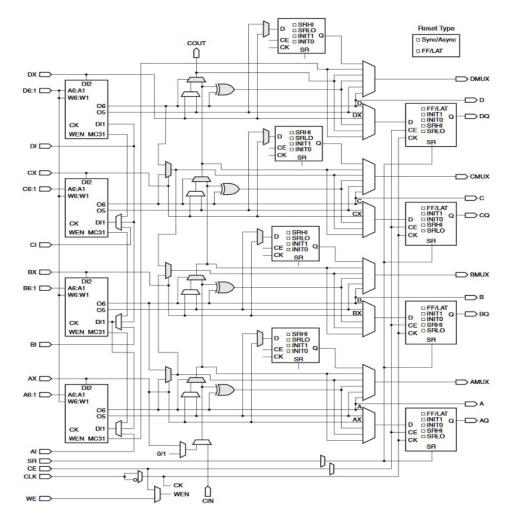

| 2.4  | Configuration of a CLB in Virtex-7 family FPGAs (Courtesy of Xilinx)                                            | 27 |

| 2.5  | Architecture of a SLICEM in Virtex-7 family FPGAs (Courtesy of Xilinx)                                          | 29 |

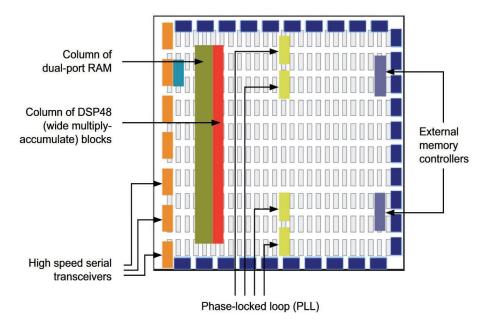

| 2.6  | Contemporary FPGA layout (Courtesy of Xilinx).                                                                  | 29 |

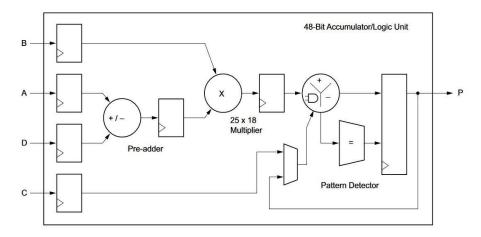

| 2.7  | Xilinx series-7 family embedded DSP block diagram (Courtesy of Xilinx)                                          | 30 |

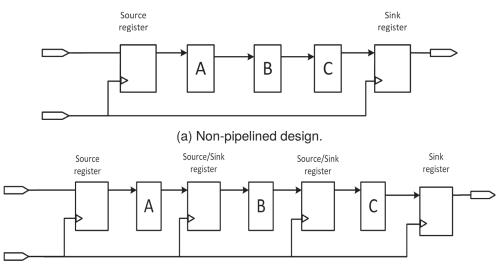

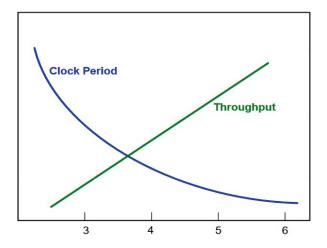

| 2.8  | Pipelined vs. none pipelined design.                                                                            | 32 |

| 2.9  | Circuit clock period and Throughput versus number of pipeline stages (n)                                        | 32 |

| 2.10 | Sample ECC side-channel power signal.                                                                           | 33 |

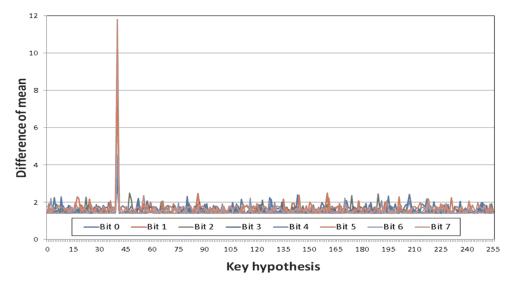

| 2.11 | A sample of differential power analysis on AES hardware                                                         | 35 |

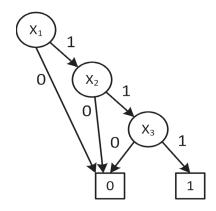

| 2.12 | A Decision Tree performing 3 bit AND operation                                                                  | 40 |

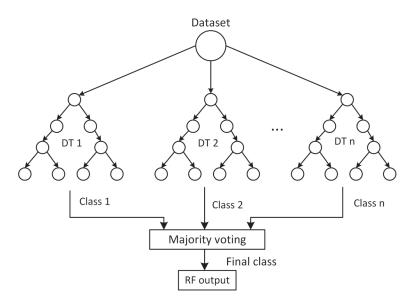

| 2.13 | Random Forest ensemble classification                                                                           | 41 |

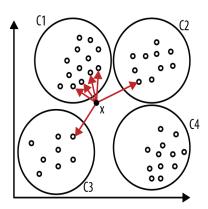

| 2.14 | kNN classification with four classes, $\{C1, C2, C3, C4\}$                                                      | 42 |

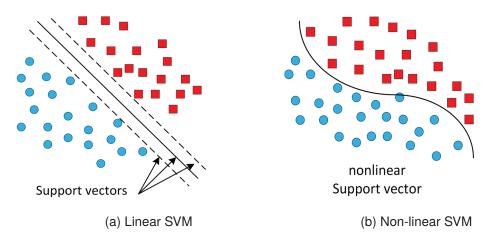

| 2.15 | Linear and non-linear Support Vector Machine                                                                    | 42 |

| 2.16 | Linear and non-linear Support Vector Machine                                                                    | 43 |

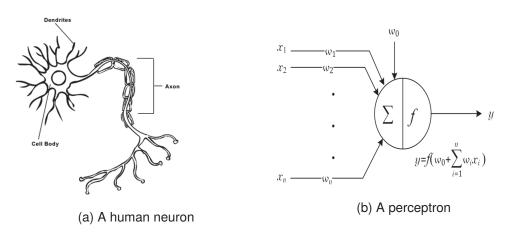

| 2.17 | Multi-layer perceptrons including input, output, and hidden layers                                              | 44 |

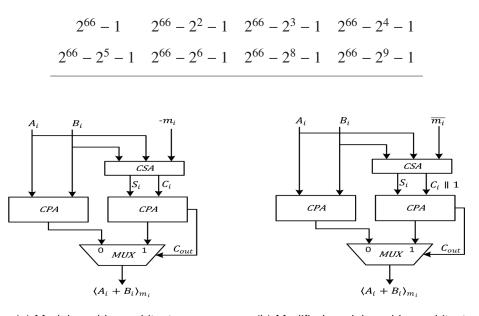

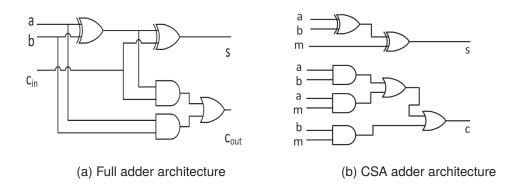

| 3.1  | RNS adder design adder architectures                                                                            | 48 |

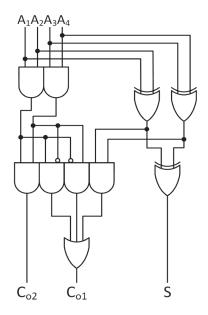

| 3.2  | Architecture of CPA and CSA adders at gate level.                                                               |    |

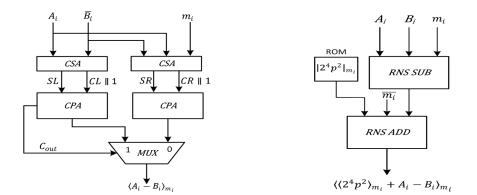

| 3.3  | Subtraction in RNS                                                                                              | 50 |

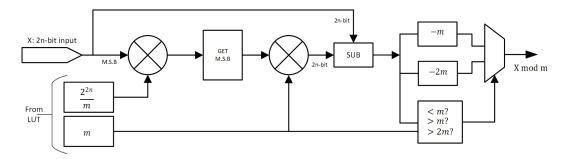

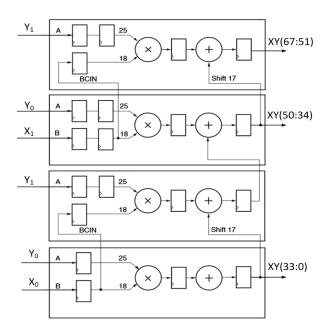

| 3.4  | Implementation of a Barrett reduction $X \mod m$                                                                | 52 |

| 3.5  | Implementation of (3.17) using 4 DSP48E                                                                         | 53 |

| 3.6  | Flow diagram of two Modifications on the RNS Montgomery reduction algorithm.                                    |    |

| 3.7  | 4-input CSA adder circuit                                                                                       | 59 |

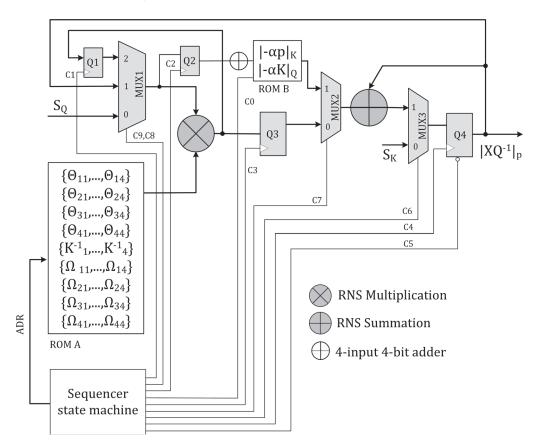

| 3.8  | Proposed hardware for modified RNS Montgomery reduction Algorithm 16                                            | 60 |

| 3.9  | Data flow of modified RNS Montgomery reduction (Algorithm 16) per clock cycle.                                  |    |

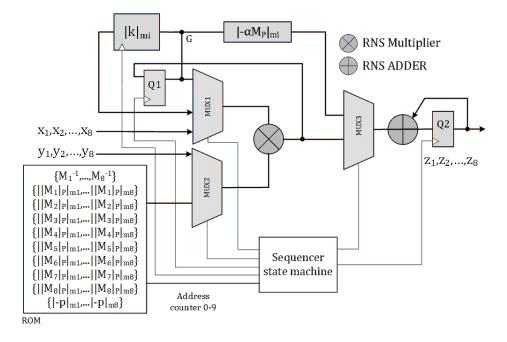

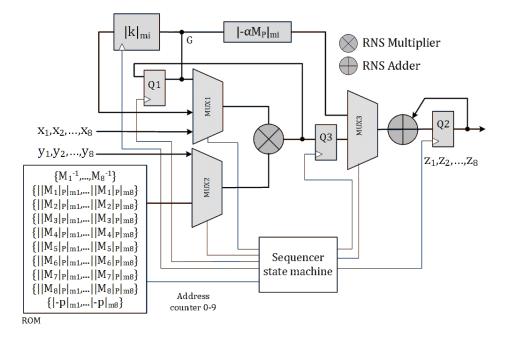

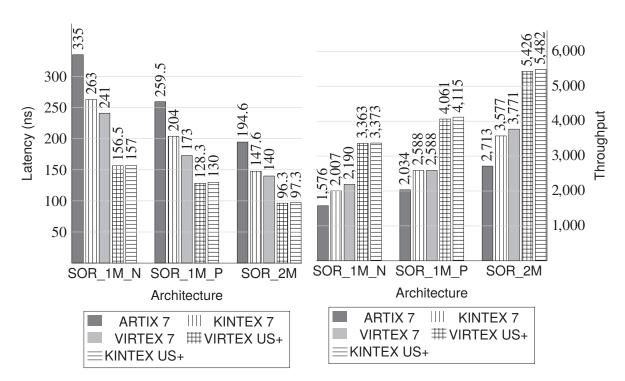

|      | Sum of residues reduction block diagram non-pipelined (SOR_1M_N) design                                         | 67 |

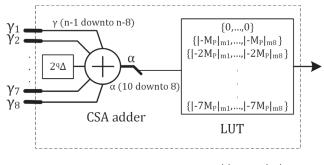

|      | Implementation of $\langle \langle -\alpha M \rangle_p \rangle_{m_i}$ .                                         | 67 |

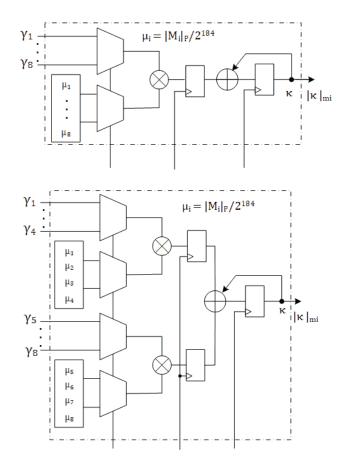

| 3.12 | Implementation of $\langle \kappa \langle -p \rangle \rangle_{m_i}$ in architectures SOR_1M_N and SOR_1M_P (Up) |    |

|      | and in architecture SOR_2M (Down).                                                                              | 68 |

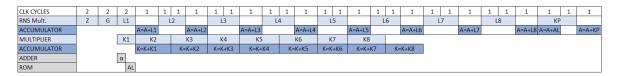

|      | Data flow of SOR non-pipelined SOR_1M_N architecture.                                                           | 68 |

|      | Sum of residues reduction block diagram with pipelined (SOR_1M_P) design                                        | 69 |

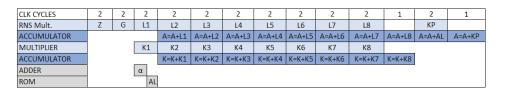

|      | Data flow of SOR pipelined SOR_1M_P architecture                                                                | 69 |

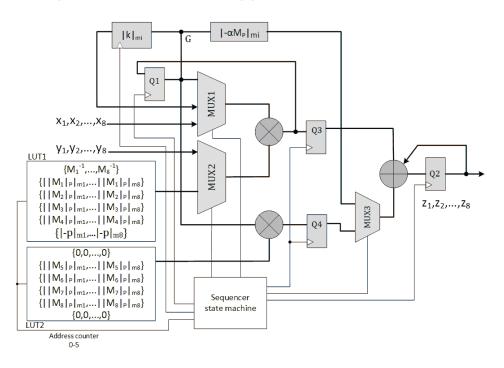

|      | Sum of residues block diagram using two parallel pipelined (SOR_2M) design                                      | 69 |

|      | Data flow of SOR with two RNS multiplier architecture SOR_2M                                                    | 70 |

|      | SOR architectures Latency and Throughput on Xilinx FPGAs                                                        | 71 |

|      | Hardware simulation of the proposed RNS Montgomery reduction algorithm                                          | 77 |

| 3.20 | Hardware simulation of the proposed sum of residues reduction algorithm                                         | 78 |

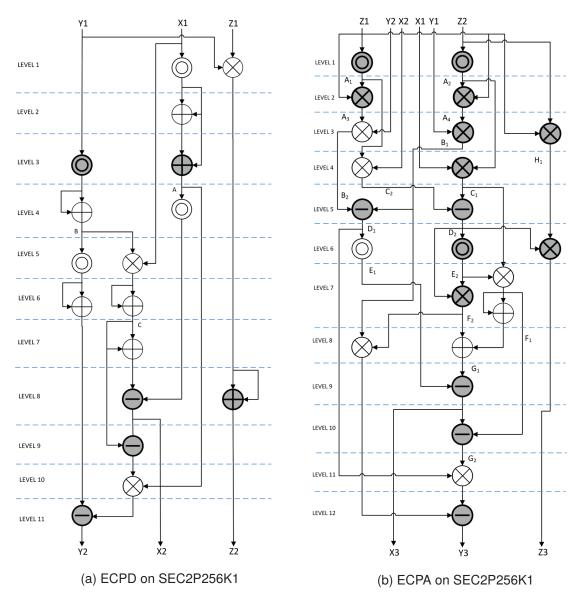

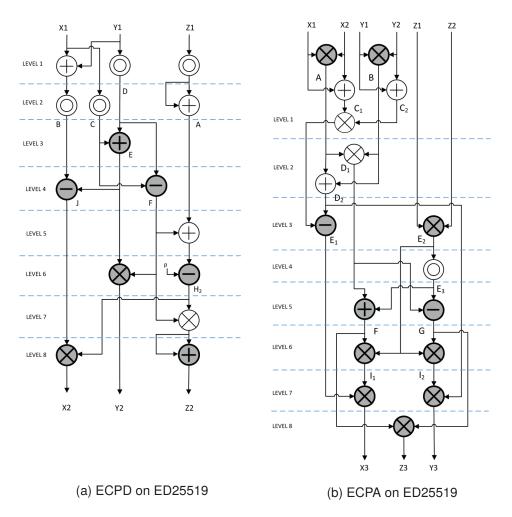

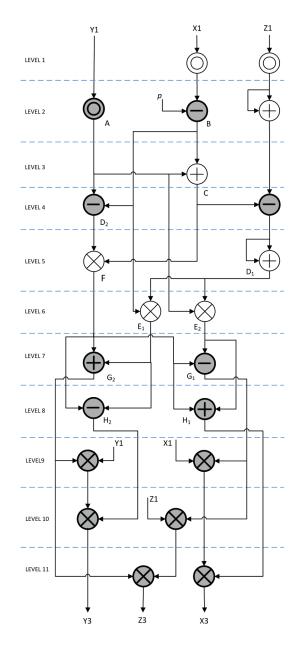

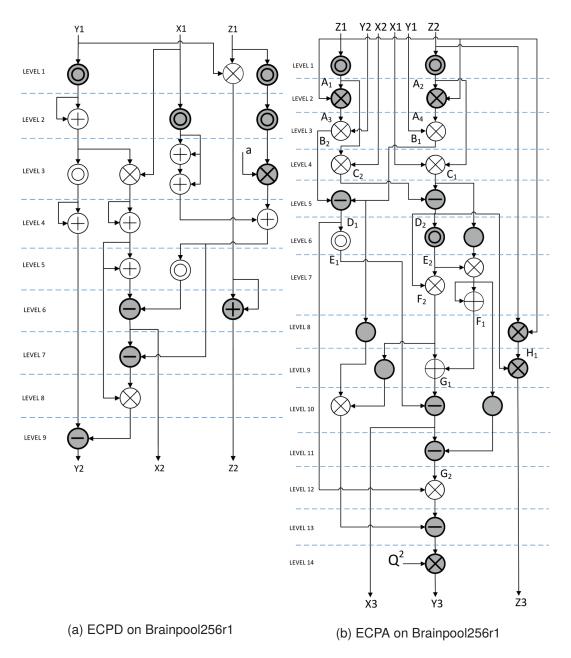

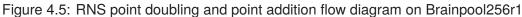

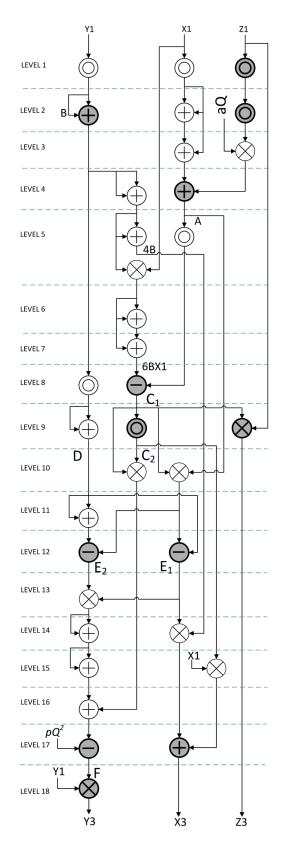

| 4.1        | RNS point doubling and point addition flow diagram on SECP256k1 ECPT flow diagram on SECP256K1 |     |

|------------|------------------------------------------------------------------------------------------------|-----|

| 4.2        |                                                                                                |     |

| 4.3<br>4.4 | RNS point doubling and point addition flow diagram on ED25519                                  |     |

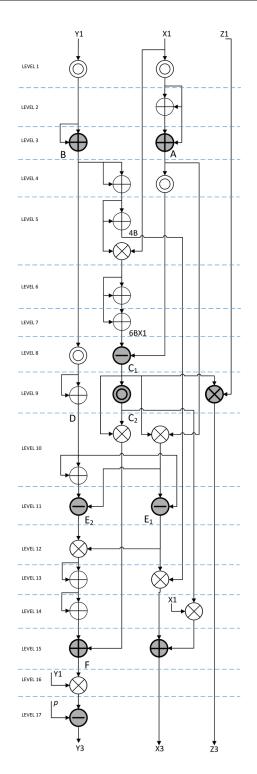

| 4.5        | RNS point doubling and point addition flow diagram on Brainpool256r1                           |     |

| 4.6        | RNS point tripling flow diagram on Brainpool256r1                                              |     |

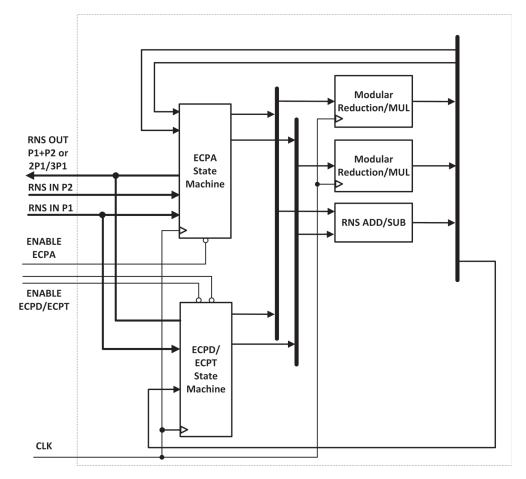

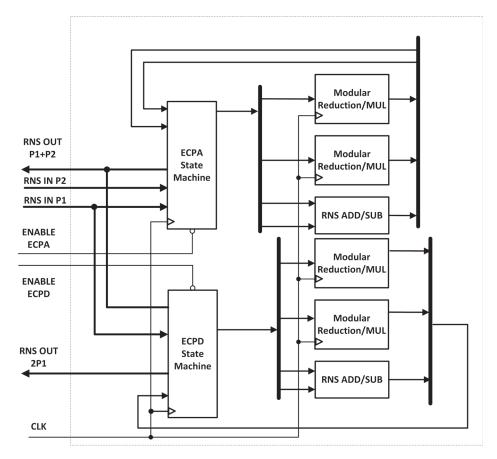

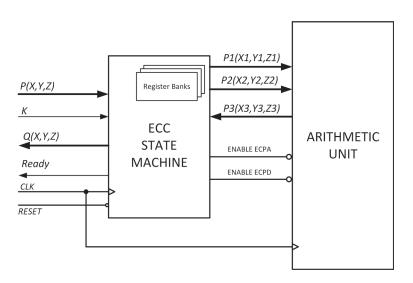

| 4.7        | General Arithmetic hardware architecture of ECPM                                               |     |

| 4.8        | Arithmetic unit hardware architecture for Montgomery ladder algorithm                          |     |

| 4.9        | RNS ECC Core Hardware implementation                                                           |     |

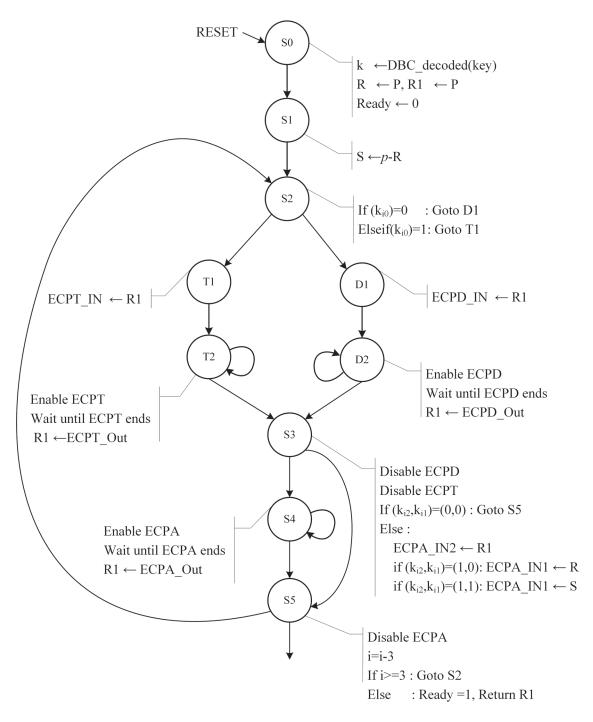

| 4.10       | Double-and-Add algorithm state machine                                                         |     |

|            | Montgomery ladder algorithm state machine                                                      |     |

|            | NAF algorithm state machine                                                                    |     |

|            | NAF <sub>3</sub> algorithm state machine                                                       |     |

|            | DBC algorithm state machine                                                                    |     |

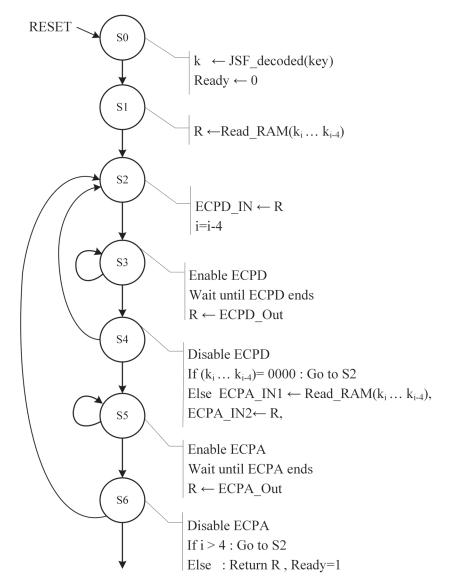

| 4.15       | Scalar multiplication state machine using GLV algorithm                                        | 99  |

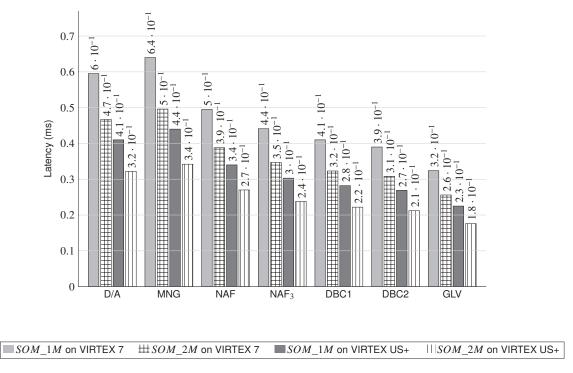

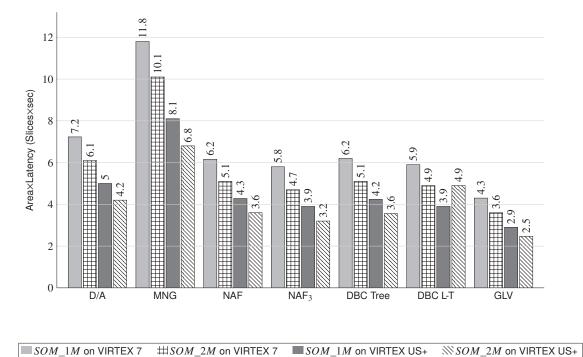

| 4.16       | SECP25k1 point multiplication latency on Xilinx FPGAs                                          | 103 |

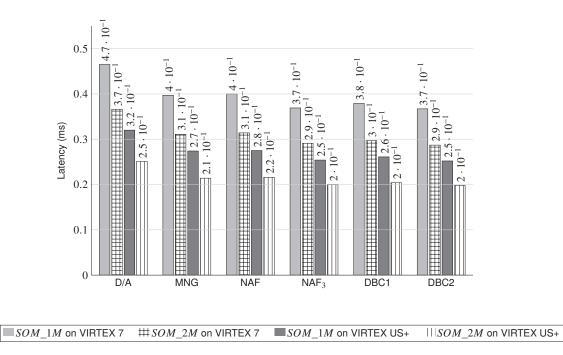

|            | ED25519 point multiplication latency on Xilinx FPGAs                                           |     |

| 4.18       | SECP25k1 point multiplication performance Area × Timing                                        | 104 |

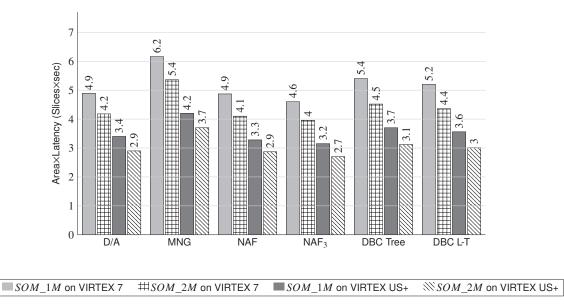

| 4.19       | ED25519 point multiplication performance Area × Timing                                         | 104 |

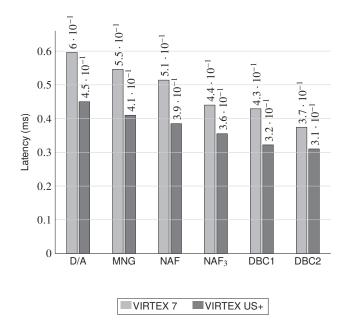

| 4.20       | Brainpool256r1 point multiplication latency on Xilinx FPGAs                                    | 105 |

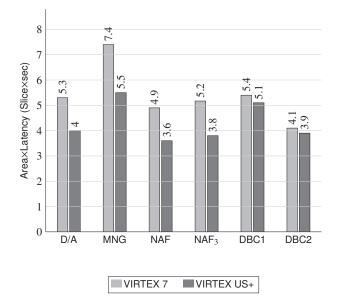

| 4.21       | Brainpool256r1 point multiplication performance Area $\times$ Timing $\ldots$ .                | 105 |

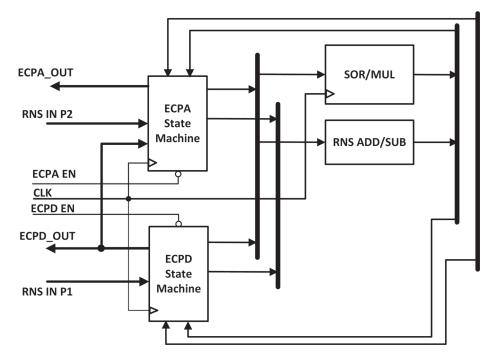

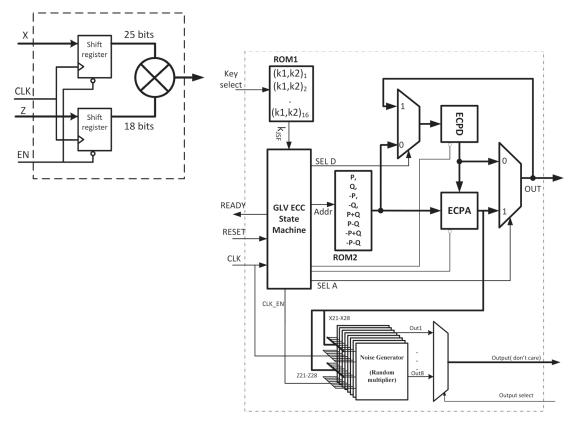

| 5.1        | RNS GLV core arithmetic unit architecture.                                                     | 108 |

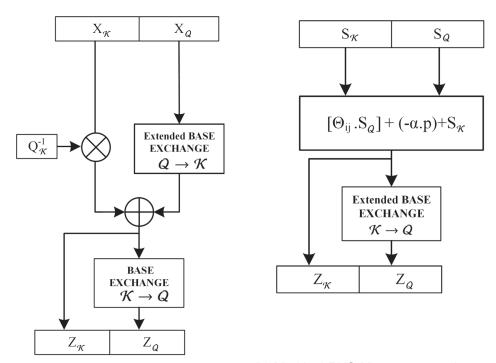

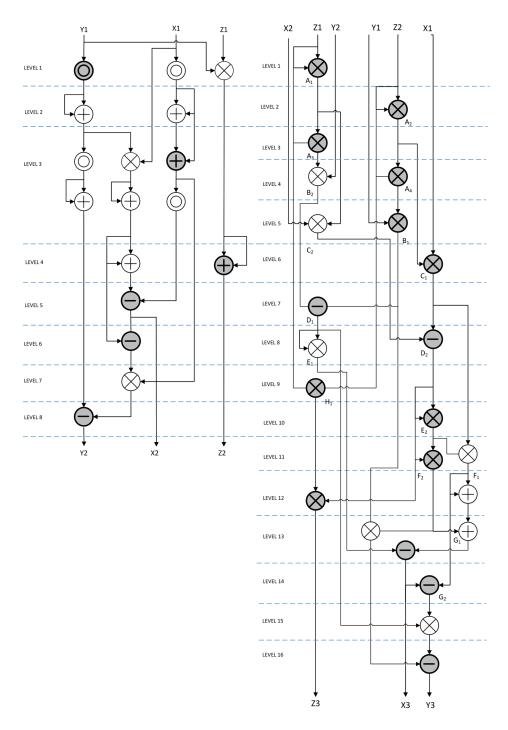

| 5.2        | ECPD (left) and ECPA (right) flow diagram in the RNS GLV core                                  | 109 |

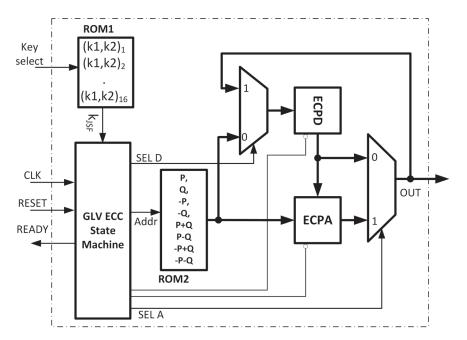

| 5.3        | RNS GLV ECC point multiplication design                                                        | 110 |

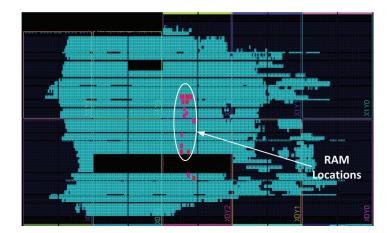

| 5.4        | Distributed ROM locations on KINTEX-7 FPGA                                                     | 110 |

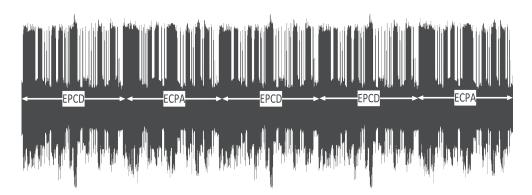

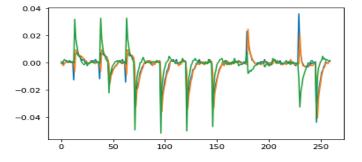

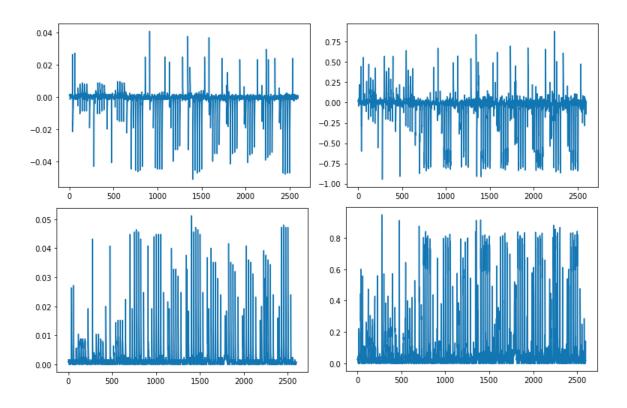

| 5.5        | Three side-channel power traces of a modular reduction operation on $\ensuremath{FPGA}$        | 112 |

| 5.6        | side-channel power trace top: two doubling, middle: doubling then addition with                |     |

|            | P, down: doubling then addition with P+Q $\ldots$                                              | 112 |

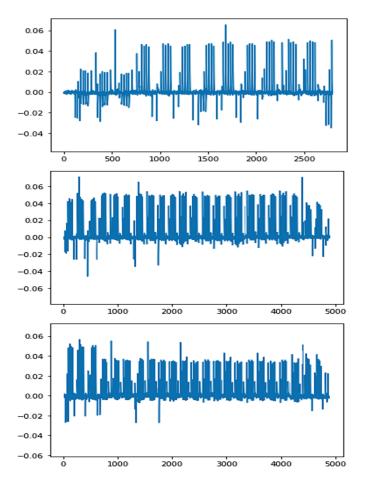

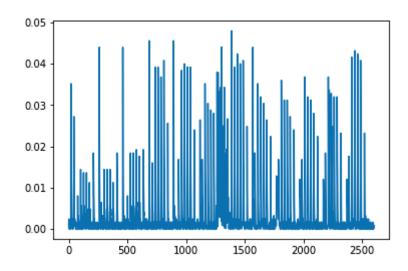

| 5.7        | Dataset window, top: ECPD-ECPA, down: ECPD-ECPD sequence                                       | 113 |

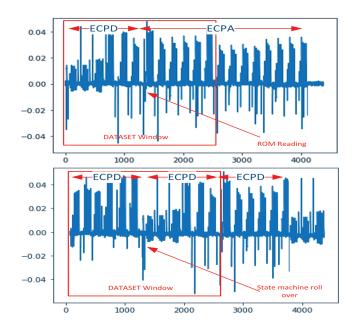

| 5.8        | Raw power signal (top left), Scaled power signal (top right), absolute power                   |     |

|            | signal (bottom left), and absolute scaled signal (bottom right)                                | 115 |

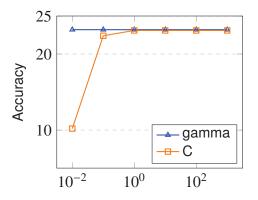

| 5.9        | Linear SVM accuracy vs algorithm parameters                                                    | 115 |

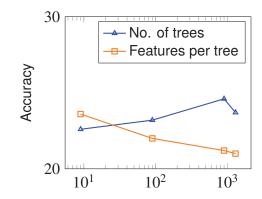

| 5.10       | Random Forest accuracy on power signal dataset vs parameters                                   | 116 |

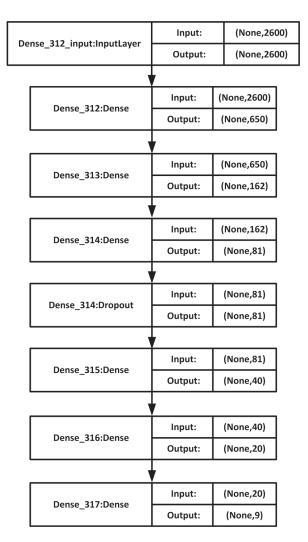

|            | Fully connected deep neural network configuration                                              |     |

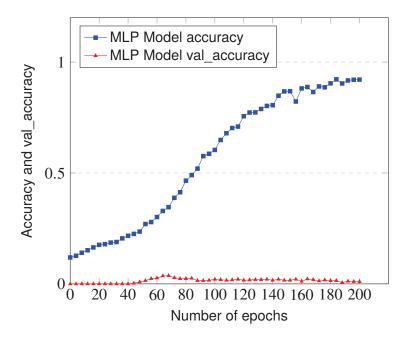

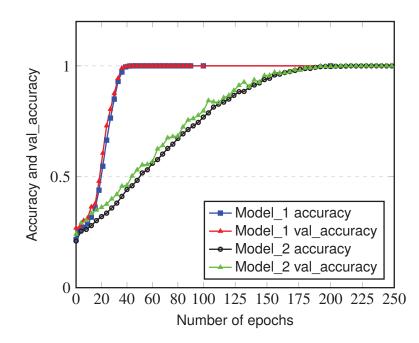

|            | Accuracy and accuracy validation for fully connected DNN model                                 |     |

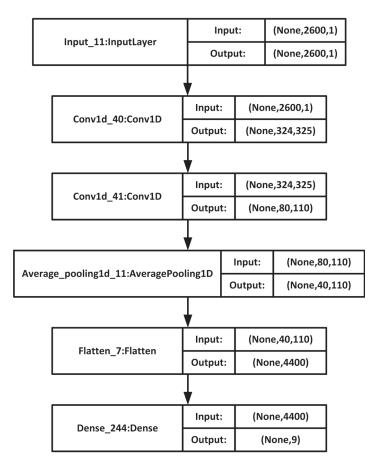

|            | 1D-CCN Model_1 configuration                                                                   |     |

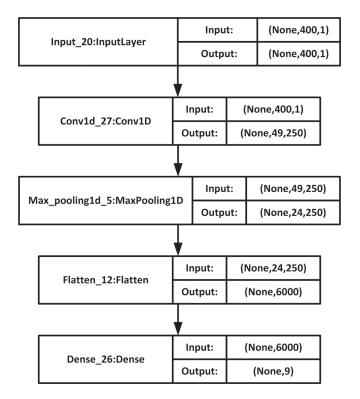

| 5.14       | 1D-CCN Model_2 configuration                                                                   | 120 |

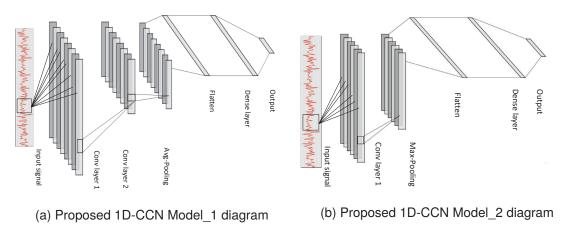

|            | 1D-CNN models                                                                                  |     |

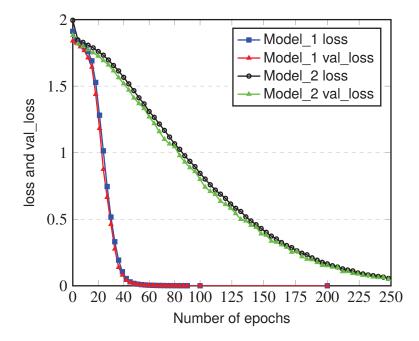

|            | Loss and loss validation for 1DCNN Model_1 and Model_2                                         |     |

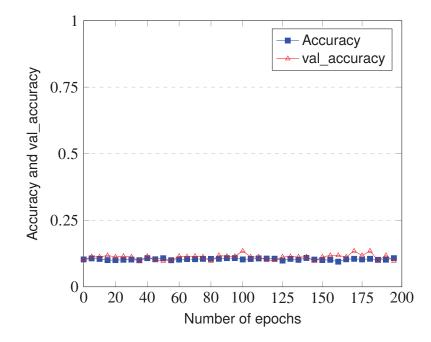

|            | Accuracy and accuracy validation for 1DCNN Model_1 and Model_2                                 |     |

|            | RNS GLV ECC design immune to side-channel attack.                                              |     |

|            | ECPD-ECPA power signal with applying a dummy operation                                         |     |

| 5.20       | 1DCNN Model accuracy/val_accuracy after applying countermeasures                               | 123 |

## List of Tables

| 2.1<br>2.2<br>2.3                                    | Curve SEC2P256K1 domain parameters17Curve Brainpool256r1 domain parameters18Curve ED25519 domain parameters18                |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | 66-bit co-primes of moduli set $\mathcal{B}$                                                                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | SECP256K1 and ED25519 point operations latency in nano seconds 90<br>Brainpool256r1 point operations latency in nano seconds |

|                                                      | FPGA                                                                                                                         |

## List of Algorithms

| 1  | Multiplicative inverse of a modulo b using Extended Euclidean algorithm 7 |

|----|---------------------------------------------------------------------------|

| 2  | Calculation of $\alpha$                                                   |

| 3  | RNS Base Exchange from $\mathcal{K}$ to $Q$                               |

| 4  | Montgomery modular reduction                                              |

| 5  | RNS Montgomery modular reduction                                          |

| 6  | Binary Double and Add point multiplication algorithm                      |

| 7  | Montgomery ladder algorithm                                               |

| 8  | Binary to $NAF_w$ conversion                                              |

| 9  | $NAF_w$ point multiplication algorithm                                    |

| 10 | Calculation of $k_1$ and $k_2$                                            |

| 11 | Simultaneous multiple point multiplication                                |

| 12 | Greedy algorithm to find DBNS form of an integer                          |

| 13 | Tree-based DB-Chain search algorithm                                      |

| 14 | Always Double-and-Add point multiplication algorithm                      |

| 15 | Optimised RNS Montgomery algorithm                                        |

| 16 | Modification of Algorithm 15                                              |

| 17 | Improved Sum of residues reduction                                        |

## List of Symbols

List of symbols used in this thesis.

| $\langle A \rangle_m$              | $A \mod m$ .                                                                                                                                                                                     |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gcd( <i>A</i> , <i>B</i> )         | The greatest common divisor of $A$ and $B$ .                                                                                                                                                     |

| $mods(A, B) \dots$<br>$A \oplus B$ | $\left\langle \langle A \rangle_B + \left\lfloor \frac{B}{2} \right\rfloor \right\rangle_B - \left\lfloor \frac{B}{2} \right\rfloor.$<br>The bitwise XOR of the integers <i>A</i> and <i>B</i> . |

| $A \odot B$                        | The bitwise XNOR of the integers $A$ and $B$ .                                                                                                                                                   |

| $A \lor B \dots$                   | The bitwise OR of the integers $A$ and $B$ .                                                                                                                                                     |

| $A \wedge B$                       | The bitwise AND of the integers $A$ and $B$ .                                                                                                                                                    |

| Ā                                  | The bitwise NOT of the integer A.                                                                                                                                                                |

| $A_i{}^j$                          | The bit $j$ of the integer $A_i$ .                                                                                                                                                               |

| <i>a</i>    <i>b</i>               | Bit $a$ concatenation to bit $b$ .                                                                                                                                                               |

| $(A, B) \leftarrow (C, D) \dots$   | The value of $C$ and $D$ is loaded to registers $A$ and $B$ respectively at the same clock edge.                                                                                                 |

| R                                  | Set of Real numbers.                                                                                                                                                                             |

| $\mathbb{F}_p$                     | Prime Field.                                                                                                                                                                                     |

| $\mathbb{F}_{2^m}$                 | Binary Field.                                                                                                                                                                                    |

| # <i>E</i>                         | The order of the elliptic curve $E$ .                                                                                                                                                            |

| $A_{\mathcal{B}}$                  | The RNS presentation of $A$ over the RNS base $\mathcal{B}$ .                                                                                                                                    |

| $(b_{n-1}b_{n-1}\ldots b_0)$       | Binary representation of an <i>n</i> -bit integer <i>B</i> . ( $b_i \in \{0, 1\}$ ).                                                                                                             |

| '0'                                | Zero bit.                                                                                                                                                                                        |

| [ <i>u</i> ]                       | The function $ceil(u)$ .                                                                                                                                                                         |

| <i>[u]</i>                         | The function $floor(u)$ .                                                                                                                                                                        |

| $\oplus$                           | RNS addition operator.                                                                                                                                                                           |

| Α                                  | Matrix A.                                                                                                                                                                                        |

| <b>A</b> <sup><i>T</i></sup>       | Transpose of Matrix A.                                                                                                                                                                           |

| <i>X</i>                           | Vector X.                                                                                                                                                                                        |

| $ReLu(x) = \begin{cases} x & x \ge 0\\ 0 & x < 0 \end{cases} \dots$ | Relu function.                                     |

|---------------------------------------------------------------------|----------------------------------------------------|

| ⊗                                                                   | RNS multiplication operator.                       |

| ©                                                                   | RNS squaring operator.                             |

| ⊕                                                                   | RNS addition and modular reduction operator.       |

| _                                                                   | RNS subtraction and modular reduction operator.    |

| ⊗                                                                   | RNS multiplication and modular reduction operator. |

| ©                                                                   | RNS squaring and modular reduction operator.       |

| 0                                                                   | RNS modular reduction operator.                    |

|                                                                     |                                                    |

## List of Acronyms

| 1D-CNN                                 | 1-Dimensional Convolutional Neural Network                                                                                                                                                                                                                    |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AES                                    | Advanced Encryption Standard                                                                                                                                                                                                                                  |

| ANN                                    | Artificial Neural Networks                                                                                                                                                                                                                                    |

| ANSI                                   | American National Standards Institute                                                                                                                                                                                                                         |

| ASIC                                   | Application Specific Integrated Circuit                                                                                                                                                                                                                       |

| BE                                     | Base Exchange                                                                                                                                                                                                                                                 |

| CLB                                    | Configurable Logic Block                                                                                                                                                                                                                                      |

| CNN                                    | Convolutional Neural Network                                                                                                                                                                                                                                  |

| СРА                                    | Carry Propagate Adder                                                                                                                                                                                                                                         |

| CPU                                    | Central Processing Unit                                                                                                                                                                                                                                       |

| CSA                                    | Carry Select Adder                                                                                                                                                                                                                                            |

| CRT                                    | Chinese Remainder Theorem                                                                                                                                                                                                                                     |

| DAG                                    | Directed Acyclic Graph                                                                                                                                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                               |

| DBC                                    | Double Base Chain                                                                                                                                                                                                                                             |

| DBC<br>DBNS                            | Double Base Chain<br>Double Base Number System                                                                                                                                                                                                                |

|                                        |                                                                                                                                                                                                                                                               |

| DBNS                                   | Double Base Number System                                                                                                                                                                                                                                     |

| DBNS<br>DEMA                           | Double Base Number System<br>Differential Electro-Magnetic Analysis                                                                                                                                                                                           |

| DBNS                                   | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange                                                                                                                                                            |

| DBNS                                   | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange<br>Deep Learning                                                                                                                                           |

| DBNS                                   | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange<br>Deep Learning<br>Deep Neural Network                                                                                                                    |

| DBNS<br>DEMA<br>DH<br>DL<br>DNN<br>DPA | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange<br>Deep Learning<br>Deep Neural Network<br>Differential Power Analysis                                                                                     |

| DBNS                                   | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange<br>Deep Learning<br>Deep Neural Network<br>Differential Power Analysis<br>Differential Side-Channel Analysis                                               |

| DBNS                                   | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange<br>Deep Learning<br>Deep Neural Network<br>Differential Power Analysis<br>Differential Side-Channel Analysis<br>Digital Signal Processing                  |

| DBNS                                   | Double Base Number System<br>Differential Electro-Magnetic Analysis<br>Diffie-Hellman Key Exchange<br>Deep Learning<br>Deep Neural Network<br>Differential Power Analysis<br>Differential Side-Channel Analysis<br>Digital Signal Processing<br>Decision Tree |

| ECDSA | Elliptic Curve Digital Signature Algorithm      |

|-------|-------------------------------------------------|

| ЕСРА  | Elliptic Curve Point Addition                   |

| ECPD  | Elliptic Curve Point Doubling                   |

| ECPM  | Elliptic Curve Point Multiplication             |

| ЕСРТ  | Elliptic Curve Point Tripling                   |

| ETSI  | European Telecommunications Standards Institute |

| FA    | Full Adder                                      |

| FC    | Fully Connected                                 |

| FPGA  | Field Programmable Gate Array                   |

| GAN   | Generative Adversarial Network                  |

| GLV   | Gallant-Lambert-Vanstone                        |

| НА    | Half Adder                                      |

| HDL   | Hardware Description Language                   |

| ITS   | Intelligent Transportation System               |

| JSF   | Joint Sparse Form                               |

| k-NN  | k-Nearest Neighbours                            |

| LSTM  | Long Short-Term Memory                          |

| LSB   | Least Significant Bit                           |

| LUT   | Look-Up Table                                   |

| MESD  | Multiple-Exponents, Single-Data Attack          |

| ML    | Machine Learning                                |

| MLP   | Multi-Layer Perception                          |

| MMR   | Montgomery Modular Reduction                    |

| MSB   | Most Significant Bit                            |

| MR    | Modular Reduction                               |

| MUX   | Multiplexer                                     |

| NAF   | Non-Adjacent Form                               |

| NIST  | National Institute of Standards and Technology  |

| PCA   | Principal Component analysis                    |

| POI   | Point Of Interest                               |

| RAM   | Random Access Memory                            |

| RF    | Random Forest                                   |

| RNN   | Recurrent Neural Networks                       |

| RNS   | Residue Number System                           |

|       |                                                 |

| ROM   | Read-Only Memory                          |

|-------|-------------------------------------------|

| RSA   | Rivest-Shamir-Adleman                     |

| SECG  | Standard for Efficient Cryptography Group |

| SEMA  | Simple Electro-Magnetic Analysis          |

| SEMD  | Single Exponent Multiple Data Attack      |

| SCA   | Side-Channel Attacks                      |

| SNR   | Signal to Noise Ration                    |

| SOR   | Sum of Residues                           |

| SPA   | Simple Power Analysis                     |

| SSCA  | Simple Side-Channel Analysis              |

| SVM   | Support Vector Machine                    |

| V2I   | Vehicle-to-Infrastructure                 |

| V2V   | Vehicle-to-Vehicle                        |

| VHDL  | VHSIC Hardware Description Language       |

| VHSIC | Very High Speed Integrated Circuits       |

| VLSI  | Very Large Scale Integration              |

| ZEMD  | Zero Exponent Multiple Data Attack        |

When theory and experiment agree, that is the time to be especially suspicious.

Niels Bohr

# Introduction

In the recent decade, we have witnessed rapid developments in applications of public-key cryptography (PKC). The elliptic curve cryptography (ECC) especially has been at the centre of attention because it provides the same level of security as its counterparts, such as RSA and ElGamal, with smaller bit-size keys. Other than data security (confidentiality), PKC offers authentication, data integrity, and non-repudiation, which makes it suitable for a range of applications. Blockchain technology and Bitcoin cryptocurrency were introduced in 2009 using ECC as a core function to implement non-repudiation and authentication. Blockchain was found very interesting in business applications and became one of the pillars of FINTECH 3.0. Other than business and finance applications, Blockchain has been used in many different domains like digital voting and supply chain management. A wide range of cryptocurrencies is now available in the market, and they are becoming increasingly prevalent. Intelligent transportation systems (ITS) introduced in 2010, use ECC as their standard to sign and verify short communication and control car-to-car and car-to-infrastructures messages. The self-driving cars which first allowed on the roads for testing in 2015, use the same methods to authenticate communications. The IoT security and cloud computing security are other examples of new emerging applications that use elliptic curve cryptography as their underlying cryptosystem.

The security of the elliptic curve cryptosystems is based on the elliptic curve discrete logarithm problem (ECDLP). It is assumed that finding a random multiple of a known base point on the elliptic curve (EC) is computationally infeasible. A multiple of a point on the EC is calculated by a one-way function that is called "point multiplication" (or scalar multiplication). The point multiplication is a time-consuming process by nature. It uses the curve's algebraic formulas iteratively to calculate the new point. The core arithmetic primitive in the computation of a point coordinates is the modular reduction over the finite field characteristic, which is a complex arithmetic operation.

The latency of point multiplication imposes limitations in exploiting ECC in high-level applications. For instance, consider an ITS scenario. Cars and infrastructures must send digitally signed control and safety messages to each other and verify the messages they receive. A digital signature needs one point-multiplication, and verification needs two point-multiplications using an elliptic curve digital signature (ECDSA) scheme. By growing the number of cars on the road, verification of all incoming messages may not be possible; that may result in losing critical safety messages. A similar scenario applies to the self-driving cars technology, where decision-making relies on the verified messages received from roads infrastructures and other cars.

The latency of ECDSA is a determining factor of transactions speed in cryptocurrencies and verification of blocks in the Blockchain technology. The overall functionality of these applications can be limited by the latency of the cryptographic functions. Hence, this latency to be reduced as much as possible. The solution is the use of cryptographic co-processors. A co-processor is a hardware core that performs supplement functions of the primary processor (CPU).

Since the early days of computers, co-processors have been used to relieve the main CPU and accelerate processing times. They may be used for floating-point arithmetic (FPU), as graphics accelerators GPU), digital signal processing (DSP), or I/O interfacing (such as PCI and USB chips).

Cryptographic hardware has been an overwhelming research topic in recent years. Significant research has been done to reduce the latency of the elliptic curve point multiplication. There are different approaches to the problem. Many works in the literature, have tried to improve the elliptic curves group laws and propose algorithms to perform point multiplications in fewer iterations. Some works focused on improving modular arithmetic as the core function of the most public-key cryptosystems. Some other works concentrated on the implementation methods of cryptographic hardware, VLSI algorithms, and timing closure problems on either ASIC or FPGA devices.

An essential criterion the cryptographic co-processors must meet is physical security. A cryptographic algorithm may be mathematically secure. However, the hardware that runs this algorithm can leak the information. In 1996, Kocher found that cryptographic systems can be broken by monitoring and analysing side-channel information such as timing, power consumption, and electromagnetic radiation. Side-channel analysis attacks are a serious threat to the security of embedded devices, such as smart-cards, IoT devices, Blockchain, cryptocurrencies, etc. Recently, side-channel attacks on applications of ECC cryptosystems have been extensively studied. Matthews [1] showed that the security of smart cards can be compromised using low cost side-channel attacks. Wunan et al. [2] presented a side-channel attack case on Blockchain's ECDSA and acquired the private key. In [3], San Pedro et al. performed a successful side-channel attack on the hardware cryptocurrency wallets. A most recent research paper from Stanford university [4], showed that privacy focused cryptocurrencies like Zcach and Monero are vulnerable against side-channel attacks.

In a nutshell, there are numerous examples of how implementations of ECC algorithms resulted in significant vulnerabilities in the cryptographic software or hardware.

The application of machine-learning and deep-learning in the side-channel data analysis has made side-channel attacks increasingly powerful. It has been shown [5] that such techniques can efficiently deal with desynchronised traces and even attack masked implementations.

As side-channel attacks are becoming more powerful, research on finding effective countermeasures to dismiss the revealed vulnerabilities is essential. Otherwise, the security promised by cryptosystems, in theory, would be unreliable in the real world.

This thesis studies the hardware implementation of the ECC in the context of Residue Number Systems (RNS). RNS represents integers by their values modulo several pairwise co-prime integers named the moduli. RNS is an active area of research allowing faster public-key cryptography operations due to its inherent parallelism. The contribution of the thesis is

in three areas.

First, I proposed efficient hardware implementations for RNS arithmetic. The proposed implementations are based on an improvement in the Montgomery modular reduction algorithm used in RNS, as it is a dominant method for RNS modular reduction. Our experiments show the hardware implementation of the new RNS Montgomery algorithm on FPGA is more efficient than the existing works in the literature. In addition to the improvement of the Montgomery modular reduction algorithm, a new modular reduction algorithm based on the sum of residues (SOR) is proposed. The motive of this design is that the SOR algorithm is highly parallel and it can efficiently reduce the calculation time. The proposed hardware architectures were implemented with different levels of parallelism and they have shown a good trade-off between cost and speed.

Second, taking advantage of parallel computing methods, I proposed a new architecture for hardware implementation of ECC group laws. I used different point multiplication algorithms to design a low-latency ECC co-processor. The proposed architectures were implemented on the FPGA and the obtained results confirm a reduction in ECC point multiplication latency.

Third, I analysed the side-channel leakage data of an RNS ECC co-processor using machine and deep learning algorithms. The experimental results confirm the method is secure from side-channel attacks.

The structure of this thesis is as follows:

**Chapter 2** provides the background required for reading this thesis. The chapter starts with an introduction to Residue Number Systems (RNS) and arithmetic operations in the context of RNS. It then continues with a brief discussion on elliptic curves and point multiplication algorithms. Next, the FPGA hardware design is briefly outlined. Side-channel data analysis and side-channel attacks and countermeasures are reviewed. Machine-learning and deep learning algorithms, and their applications in side-channel data analysis are discussed.

**Chapter 3** describes the hardware design of the ECC arithmetic primitives. This chapter details improvements on RNS Montgomery and SOR modular reduction algorithms. It also presents the implementation results.

**Chapter 4** proposes hardware architectures for the ECC co-processor. The RTL design of the ECC co-processor is described. Implementation is performed for three different elliptic curves which are widely used in the industry, including

- The curve SECP256k1, which is used for Bitcoin, Ethereum, and Blockchain.

- The curve ED25519, that is widely used in numerous network security protocols, such as Transport Layer Security (TLS) and Secure Shell (SSH).

- The curve Brainpool256r1, which is the recommended curve in the ITS security standard.

**Chapter 5** elaborates on side-channel power data gathering, pre-processing, and analysis. Various machine and deep learning algorithms are studied for the analysis of side-channel data. A successful attack to the GLV RNS ECC hardware is performed and efficient countermeasures are proposed.

**Chapter 6** discusses the achievements made in the field and concludes the thesis, future works and research directions.

**Appendix A** lists the computer programs used for the simulation of our proposed algorithms, including the RNS Montgomery reduction algorithm, the SOR reduction algorithm, and tree-based and Lévia - Thériault's DBC algorithms.

**Appendix B** lists VHDL hardware implementations of the proposed modular reduction algorithms and ECC co-processor implementations.

## 2 Background

### 2.1 The residue number systems

The Residue number systems (RNS) were discovered by Svoboda and Valach in 1955 [6] and independently by Garner in 1959 [7], who were trying to apply this numbering system into the implementation of fast arithmetic and fault-tolerant computing. Carry-free propagation and channel-independent properties of RNS make them well suited for long integers arithmetic. The residue number system uses a base of co-prime moduli  $\mathcal{B} = \{m_1, m_2, \dots, m_N\}$ , called the *RNS base*, to split an integer *X* into small *n*-bit integers  $\{x_1, x_2, \dots, x_N\}$  where  $x_i$  is the residue of *X* divided by  $m_i$  denoted as  $x_i = X \mod m_i$  or simply  $x_i = \langle X \rangle_{m_i}$ . Each modulus is called an *RNS channel*. The integer *X* is then represented using *N* RNS channels.

$$RNS(X) = \{x_1, x_2, \cdots, x_N\}.$$

(2.1)

The range of the RNS, also known as dynamic range, is computed as:

$$M = \prod_{i=1}^{N} m_i. \tag{2.2}$$

### 2.1.1 The Chinese Remainder Theorem

The Chinese scholar Sun Tzu described a riddle in his book "Arithmetical classic" in the third century.

We have things of which we do not know the number If we count them by threes, we have two left over If we count them by fives, we have three left over If we count them by sevens, we have two left over How many things are there?

Sun Tzu gave a rule, *Great Generalisation*, for the solution of his puzzle. In 1247, another Chinese scientist, Qin Jiushao, generalised the Great Generalisation into what is called the

Chinese Remainder Theorem (CRT) today [8].

The CRT has a close relationship with the RNS. Reconstruction of the integer  $X, 0 \le X < M$ , from its RNS form  $\{x_1, \ldots, x_N\}$  is possible using the CRT [9]:

$$X = \left\langle \sum_{i=1}^{N} \left\langle x_i \cdot M_i^{-1} \right\rangle_{m_i} M_i \right\rangle_M.$$

(2.3)

Where  $M_i = \frac{M}{m_i}$ , and  $M_i^{-1}$  is the multiplicative inverse of  $M_i$ . In other terms,  $M_i \cdot M_i^{-1} \mod m_i = 1$ . Throughout this thesis, we assume that:

$$2^n > m_N > \dots > m_1 > 2^{n-1}.$$

(2.4)

As a result, the dynamic range falls in the range  $2^{N \cdot (n-1)} < M < 2^{N \cdot n}$ .

Based on the Chinese remainder theorem, The RNS representation of an integer with in the RNS dynamic range is unique.

### 2.1.2 Arithmetic operations in RNS

RNS is a non-positional numbering system. Arithmetic operations in RNS are categorised into simple and complex operations. Addition, subtraction, and multiplication are simple operations that can be performed very efficiently in RNS. These operations are performed on each channel independently. However, operations like division, sign detection, comparison, and modular reduction are complex in RNS.

Suppose, *X* and *Y* are two *l*-bit integers presented in RNS form that is,  $RNS(X) = \{x_1, x_2, \dots, x_N\}$ , and  $RNS(Y) = \{y_1, y_2, \dots, y_N\}$ . The integers *A*, *S*, *Z* are the addition, subtraction, and multiplication results of *X* and *Y*, respectively. Then, the RNS are calculated as follows:

$$RNS(A) = \{ \langle x_1 + y_1 \rangle_{m_1}, \langle x_2 + y_2 \rangle_{m_2}, \cdots, \langle x_N + y_N \rangle_{m_N} \}.$$

(2.5)

$$RNS(S) = \{ \langle x_1 - y_1 \rangle_{m_1}, \langle x_2 - y_2 \rangle_{m_2}, \cdots, \langle x_N - y_N \rangle_{m_N} \}.$$

$$(2.6)$$

$$RNS(Z) = \{ \langle x_1 \cdot y_1 \rangle_{m_1}, \langle x_2 \cdot y_2 \rangle_{m_2}, \cdots, \langle x_N \cdot y_N \rangle_{m_N} \}.$$

(2.7)