## Nonlinear Modelling of GaAs and GaN High Electron Mobility Transistors

By

Jabra Tarazi

A dissertation submitted to Macquarie University in fulfilment of the requirements for the degree of Doctor of Philosophy Department of Engineering November 2020

ii

#### Statement of Candidate

I certify that the work in this thesis entitled "Nonlinear Modelling of GaAs and GaN High Electron Mobility Transistors" has not previously been submitted for a degree, nor has it been submitted as part of requirements for a degree to any other university or institution other than Macquarie University.

Except where acknowledged in the customary manner, the material presented in this thesis is, to the best of my knowledge, original and written by me.

In addition, I certify that all information sources and literature used are indicated in the thesis.

> Jabra Tarazi November 2020

#### Synopsis

This dissertation reports the work carried out by the author in a collaborative research projects between the author employers and Macquarie University. Professor Anthony Parker and Professor Michael Heimlich are the academic supervisors from Macquarie University. Dr. Simon Mahon and Mr. Anthony Fattorini are the industrial managers from Macom and Altum RF. This dissertation contains eight chapters.

This dissertation presents a new approach to scalable, large-signal modelling of GaAs and GaN microwave HEMT devices. The model can be used to accurately synthesise arbitrary device geometries and is consistent with the small-signal model.

In Chapter 3, a formulation of an intrinsic small-signal model that is consistent with the associated large-signal model is presented. The extracted small-signal parameters of the equivalent model linearly scaled with device width and are independent of frequency in the non-dispersive operating regions. Memory effects, i.e. thermal and trap states, are embedded in the steady-state small-signal intrinsic parameters, and for the largesignal model to scale accurately, these effects need to be separated from the extracted small-signal intrinsic data.

In Chapter 4, a lumped-element thermal model is formulated that can accurately model the local temperature rise, i.e. at the individual gate finger, and that scales correctly with number of fingers. The lumped-element thermal model is fitted to SPICE thermal model data, whose results are verified using Gate Resistance Thermometry (GRT) measurements. A newly-developed trap-state characterisation technique that is used to fit an adequate trap circuit model over a wide bias range is presented in Chapter 5.

The thermal and trap circuit models form part of the complete large-signal model which is fitted to the extracted multi-bias small-signal intrinsic parameters in Chapter 6. In Chapter 7, a case study power amplifier design is presented using GaN HEMT technology that is based on the complete large-signal modelling techniques and procedures developed in this dissertation.

**Chapter 1** presents today's device modelling challenges for MMIC designs, discusses the aim and the scope of the work and outlines the thesis structure.

Chapter 2 presents a background and literature review of GaAs and GaN FET devices. Basic GaAs and GaN HEMT device physics is discussed. Nonlinear dynamic effects are introduced, and the difference between small-signal and large-signal HEMT device modelling is outlined. Approaches to nonlinear modelling of HEMT devices are presented, including physics-based models, measurement-based models and more accurate nonlinear models. The information in this chapter is the work of other researchers.

In **Chapter 3** a formulation of an intrinsic small-signal model that is consistent with the associated large-signal model is presented. Initially the intrinsic active region in HEMT devices is introduced, and a fully reactive intrinsic FET equivalent circuit model is presented. A description of the small-signal *S*-parameter measurements required for the extraction process is provided. Different electromagnetic simulators are introduced as possible tools to analyse the extrinsic access metalisation of HEMT devices. An algorithm for the extraction of the intrinsic small-signal parameters is provided and applied to commercial GaAs and GaN technologies. Results indicate that the intrinsic linear model parameters are invariant with frequency and scale linearly with the gatefinger width of the device.

In Chapter 3 the intrinsic small-signal model formulation, extraction technique and verification by linear scalability and frequency-independence, were developed by Jabra Tarazi, building on suggestions from Professor Anthony Parker. All measurement and simulations were performed by Jabra Tarazi. The extraction work done on GaN devices is recent and was performed by Jabra Tarazi, but has not been published yet. A large portion of this work is published as a conference paper:

J. Tarazi, S. J. Mahon, A. P. Fattorini, M. C. Heimlich, and A. E. Parker, "A scalable linear model for FETs," in 2011 IEEE MTT-S International Microwave Symposium, June 2011, pp. 1–4.

The role of all other authors in this paper was supervisory.

In **Chapter 4** a thermal FEM SPICE model is developed to model the local temperature rise in multifinger devices taking into account self-heating, mutual heating and end effects. A lumped-element thermal model is formulated that can accurately model the local temperature rise, i.e. at the individual gate finger, and scales correctly with number of fingers. The lumped-element thermal model is fitted to SPICE thermal model data, whose results are verified using GRT measurements.

Jabra Tarazi implemented the FEM thermal model for a multifinger device in SPICE using an AWK script which is coded by him. All simulations in Chapter 4 were performed by Jabra Tarazi. The GRT measurements used to verify the SPICE thermal model were supplied by the semiconductor foundry. A significant part of this work have been published in the following conference paper:

J. Tarazi, A. E. Parker, B. Schwitter, and S. J. Mahon, "Thermal modelling of multifinger GaAs/GaN FETs using SPICE," in 2014 1st Australian Microwave Symposium (AMS), June 2014, pp. 7–8.

The role of all other authors in this paper was supervisory.

The formulation and the fitting of the scalable lumped-element thermal model is a work of Jabra Tarazi which has not been published yet.

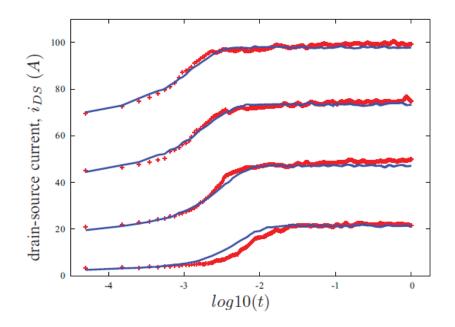

In Chapter 5 a newly-developed trap-state characterisation technique is presented. The trap state probe is introduced and implemented to observe the full gate-lag transient. The trap state extraction procedure is presented, and the trap rate is extracted. An extracted large-signal HEMT device, that includes a fitted trap circuit model, is then used to simulate and verify the measured gate-lag transients. The model also demonstrates the capability to predict the low-frequency dispersion of the Y-parameters.

The trap model extraction technique is developed by Jabra Tarazi building on suggestions from Dr. James Rathmell and Professor Anthony Parker. All measurements and characterisation work in Chapter 5 is performed by Jabra Tarazi. The formulation of the instantaneous drain current is the work of Jabra Tarazi. The extraction of the trap state, fitting of the trap model to extracted trap state data, and fitting of the large-signal model is the work of Jabra Tarazi. This work have been published in the following conference paper:

J. Tarazi, J. G. Rathmell, A. E. Parker, and S. J. Mahon, "Extraction of a trapping model over an extended bias range for GaN and GaAs HEMTs," in 2017 IEEE MTT-S International Microwave Symposium (IMS), 2017, pp. 244–247.

The role of all other authors in this paper was supervisory.

In Chapter 6 the complete model was fitted to the extracted multi-bias smallsignal intrinsic parameters, which were shown to scale linearly with the device size. The "MQFET" large-signal model is introduced. The drain current and its derivatives, and the channel capacitances of the model are fitted to the multi-bias small-signal measured data. The model is shown to predict the small-signal and large-signal performance of arbitrary synthesised device geometries.

Jabra Tarazi developed the procedure for the large-signal model extraction with guidance from Professor Parker. Most measurements and characterising work in Chapter 6 is performed by Jabra Tarazi. Dr. Bryan Schwitter assisted with some of the measurements and the thermal data. The Verilog-A code of the MQFET model is a Macquarie University proprietary intellectual property that developed by Professor Parker. A part of this work has been published in the following conference paper:

• J. Tarazi, B. K. Schwitter, A. E. Parker, and S. J. Mahon, "AlGaN/GaN HEMT

nonlinear model fitting including a trap model," in 2015 IEEE MTT-S International Microwave Symposium, May 2015, pp. 1–4.

The role of all other authors in this paper was supervisory.

In Chapter 7 a 10 Watt, 10 to 40 GHz GaN power amplifier is designed based on the complete large-signal model developed in the previous chapters. An introduction to non-uniform distributed amplifiers is provided. The de-embedding of the measured load-pull target to the intrinsic terminals of the device is discussed. Scaling the intrinsic load-pull target is discussed and cross-checked with Cripps' load-line theory. The design benefited from the scalable model in optimising the transistor unit cell layout. The design also benefited from the built-in electrothermal simulation capability. A state of the art 4-to-1, 10 to 40 GHz impedance transformer is designed, fabricated and used in the design.

The distributed amplifier and the broadband transformer are designed by Jabra Tarazi. Dr. Schwitter performed device measurements and characterisation and he also provided an updated extracted model utilising the extraction techniques developed by Jabra Tarazi. The design work in this chapter has not been published yet.

Finally, **Chapter 8** concludes the dissertation by summarising the major outcomes. Areas for future research are suggested.

### Abstract

Accurate modelling of transistors is considered to be an invaluable foundation for successful circuits. This dissertation presents a new approach to scalable, large-signal modelling of GaAs and GaN microwave HEMT devices, that can be used to accurately synthesise arbitrary device geometries. The modelling technique involves an extraction of frequency-independent small-signal intrinsic model parameters that linearly scale with zero offset in proportion to device width. These parameters are extracted from multi-bias steady-state small-signal measurements, i.e. thermal and trap states, are embedded in the extracted small-signal model parameters. Local temperature rise and trap-state of the measured device are separately characterised. A lumped-element thermal model is formulated that can accurately model the local temperature rise, i.e. at the individual gate finger, and scales correctly with number of fingers. A newlydeveloped trap-state characterisation technique that is used to fit an adequate trap circuit model over a wide bias range is presented. The thermal and trap circuit models form part of the complete large-signal model, in which the interaction of the thermal and trap models are critical to the model completeness, scalability and accuracy, as well as the consistency with the small-signal model.

The complete model is fitted to the extracted multi-bias small-signal intrinsic parameters. The model is shown to accurately predict the small-signal and large-signal performance of arbitrary synthesised device geometries. The model is then used to design a GaN PA which benefited from the scalability and built-in electrothermal simulation capability of the model to achieve best electrical and thermal performance.

## Acknowledgements

I would firstly like to thank my principal supervisor Prof. Anthony Parker for his guidance throughout my candidature. Tony was a strong supporter of all my research, and provided me with great advice. I am privileged to have had the opportunity to work with Tony and receive guidance and support from such an expert in the field of device modelling.

Many thanks go to Dr. Simon Mahon who supported and embraced my research during my time at Macom. Thanks also to Prof. Michael Heimlich who also supported my work and helped delivering the important software needed in my research.

I would also like to thank my manager at Altum RF, Mr. Anthony Fattorini for his endless help and support that gave me during my PhD. Tony has been always more of a mentor than a boss and he is a great asset to the whole engineering industry. His wealth of knowledge, guidance, patience, and generosity were fundamental to my development as an engineer. I am very fortunate to have the opportunity to work with him.

Many thanks to all my colleagues at Altum RF who provided motivation for my research. I am particularly fortunate to receive support from my colleague Dr. Bryan Schwitter who provided a lot of technical help and guidance during my research. Bryan and I had a lot of useful discussions that have provided motivation and insight for my research. I am also grateful to Mr. Greg Baker and Dr. Niels Kramer for the encouragement and support they provided during the writing of this thesis.

Many thanks go to Dr. James Rathmell, who provided a detailed edit of this thesis

in a quick time. Jim added invaluable ideas to my research and was always keen to see me finish my PhD. Jim resurrected my PhD dream in 2016 when he contacted me, out of no where, to collaborate on an idea that added a great value to this research.

I must not forget to thank Peter Vun who I am grateful to have worked with at Macquarie University during the period of 2007 to 2009. Peter introduced me to the transistor modelling world and provided invaluable support in the early stages of my career.

To mum and dad, thank you for your ongoing love and support. You have always encouraged me to pursue my goals and for that I am forever grateful.

And finally I thank my beautiful wife Mary, for her endless patience and support. Your unlimited love and enthusiasm have always been the main doses of motivation that got me through to the finish line of this challenge.

## Contents

| Sy            | nops  | sis           |                               | v   |

|---------------|-------|---------------|-------------------------------|-----|

| A             | bstra | $\mathbf{ct}$ |                               | xi  |

| $\mathbf{A}$  | cknov | wledge        | ements x                      | iii |

| Li            | st of | Figur         | es x                          | ix  |

| $\mathbf{Li}$ | st of | Table         | s xx                          | ix  |

| 1             | Intr  | oducti        | ion                           | 1   |

|               | 1.1   | HEM           | $\Gamma$ Modelling Challenges | 2   |

|               | 1.2   | Motiv         | ation                         | 3   |

|               |       | 1.2.1         | Aims                          | 4   |

|               |       | 1.2.2         | Scope                         | 5   |

| <b>2</b>      | Bac   | kgrou         | nd                            | 7   |

|               | 2.1   | High l        | Electron Mobility Transistor  | 7   |

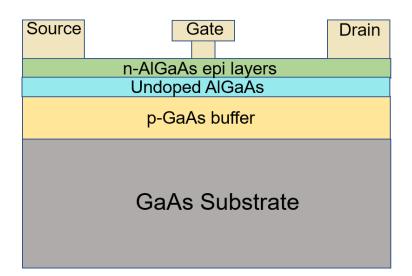

|               |       | 2.1.1         | GaAs pHEMT                    | 8   |

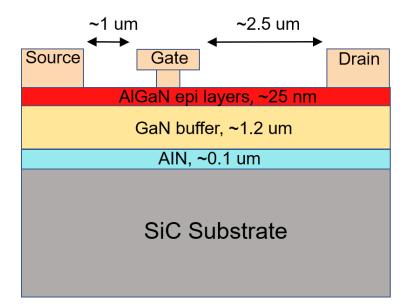

|               |       | 2.1.2         | AlGaN/GaN HEMT                | 9   |

|               | 2.2   | Intrins       | sic Model Topology            | 9   |

|               | 2.3   | Large-        | signal Models Review          | 12  |

|               |       | 2.3.1         | Measurement-based Models      | 12  |

|   |                | 2.3.2   | Behavioural Models                                         | 14 |

|---|----------------|---------|------------------------------------------------------------|----|

|   |                | 2.3.3   | Compact Models                                             | 15 |

|   |                | 2.3.4   | MQFET                                                      | 17 |

|   | 2.4            | Thern   | nal State                                                  | 18 |

|   |                | 2.4.1   | FETs Thermal Modelling Overview                            | 19 |

|   | 2.5            | Trap S  | State                                                      | 22 |

|   |                | 2.5.1   | Modelling of Trapping                                      | 23 |

| 3 | $\mathbf{Ext}$ | ractio  | n and Verification of Intrinsic Small-signal Model Parame- | -  |

|   | ters           | 5       |                                                            | 27 |

|   | 3.1            | Scalab  | oility of Intrinsic Model Parameters                       | 28 |

|   | 3.2            | Small-  | -signal Measurement                                        | 34 |

|   |                | 3.2.1   | HEMT Test Structures                                       | 34 |

|   |                | 3.2.2   | Calibration Structures                                     | 35 |

|   |                | 3.2.3   | Measurement Plan                                           | 36 |

|   | 3.3            | Extra   | ction of Intrinsic Parameters                              | 36 |

|   |                | 3.3.1   | Electromagnetic Analysis For Device Metalisation           | 37 |

|   |                | 3.3.2   | De-embedding the Extrinsic Network from Small-signal Mea-  |    |

|   |                |         | sured Data                                                 | 45 |

|   |                | 3.3.3   | Noise                                                      | 49 |

|   | 3.4            | Practi  | ical Application and Verification                          | 51 |

|   |                | 3.4.1   | Application to GaAs Process Technology                     | 51 |

|   |                | 3.4.2   | Application to GaN Process Technology                      | 54 |

|   | 3.5            | Summ    | nary                                                       | 66 |

| 4 | The            | ermal I | Modelling and Model Implementation                         | 69 |

|   | 4.1            | Globa   | l and Local Thermal State                                  | 70 |

|   | 4.2            | Finite  | -element Model                                             | 71 |

|   | 4.3            | SPICI   | E Implementation                                           | 74 |

|   |                | 4.3.1   | Non-linear Temperature Dependent Thermal Resistance        | 76 |

|   |                | 4.3.2   | Heat Flow in the Third Dimension                           | 77 |

|          | 4.4  | Application To GaN Technology                                    | 8 |

|----------|------|------------------------------------------------------------------|---|

|          |      | 4.4.1 Thermal Extraction                                         | 9 |

|          | 4.5  | SPICE Simulation Results                                         | 1 |

|          |      | 4.5.1 Model Calibration and Verification                         | 1 |

|          |      | 4.5.2 SPICE Model Results and Observations                       | 5 |

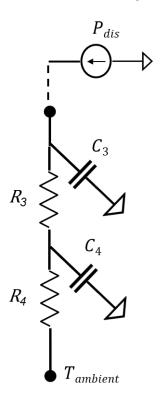

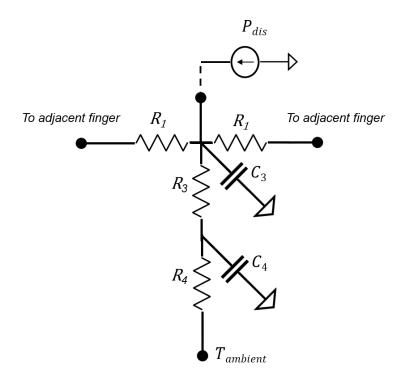

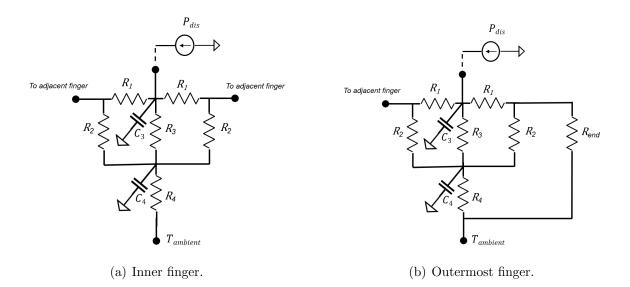

|          | 4.6  | SPICE-based Gate-finger Lumped-element Model                     | 8 |

|          |      | 4.6.1 Vertical Heat Flow                                         | 9 |

|          |      | 4.6.2 Lateral Heat Flow 92                                       | 2 |

|          | 4.7  | Lumped-Element Model                                             | 4 |

|          | 4.8  | Fitting Lumped-Element Model to SPICE Data                       | 6 |

|          | 4.9  | Summary 10                                                       | 1 |

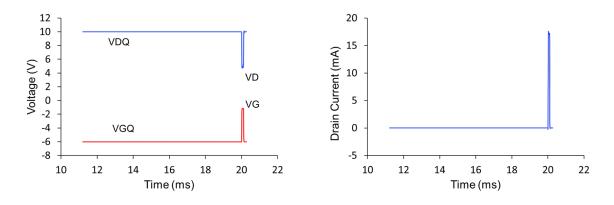

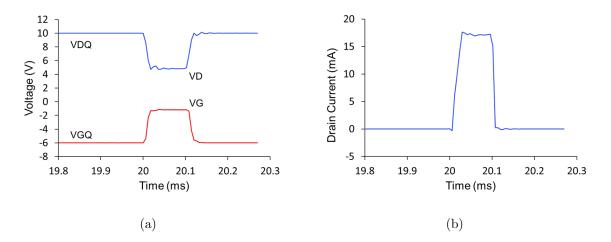

| <b>5</b> | Tra  | p Characterisation and Model Implementation 103                  | 3 |

|          | 5.1  | Trap State Probe                                                 | 4 |

|          | 5.2  | Trap State Extraction                                            | 6 |

|          | 5.3  | Trap Rate                                                        | 8 |

|          | 5.4  | Discussion                                                       | 9 |

|          | 5.5  | Application to GaN Process Technology 113                        | 3 |

|          |      | 5.5.1 Trap Extraction                                            | 3 |

|          | 5.6  | Summary                                                          | 8 |

| 6        | Fitt | ing and Verification of a Complete Large-signal Model, Including |   |

|          | The  | ermal and Trapping Effects 119                                   | 9 |

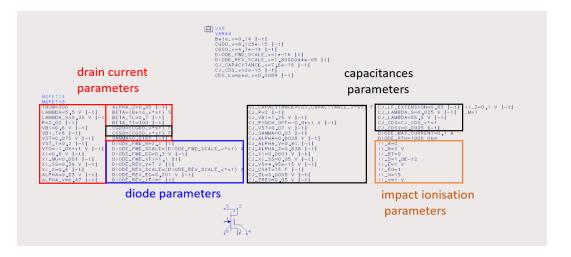

|          | 6.1  | Modelling Approach                                               | 0 |

|          | 6.2  | Application to GaN Process Technology                            | 4 |

|          |      | 6.2.1 Small-Signal Measurement Details                           | 4 |

|          |      | 6.2.2 Model Fitting                                              | 4 |

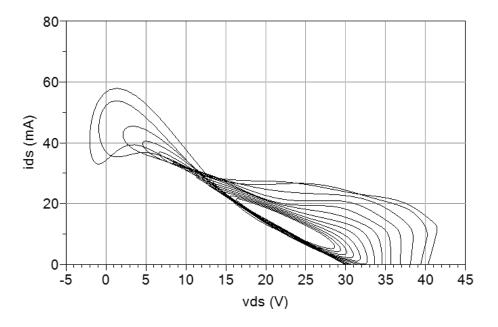

|          | 6.3  | Model Verifications                                              | 9 |

|          |      | 6.3.1 New Device Synthesis                                       | 0 |

|          |      | 6.3.2 Large-signal Verification                                  | 3 |

|          |      | 6.3.3 Scaling Limits                                             | 5 |

|              | 6.4   | Summ    | ary                                                   | 135 |

|--------------|-------|---------|-------------------------------------------------------|-----|

| 7            | Cas   | e Stud  | y                                                     | 137 |

|              | 7.1   | Distrik | buted Power Amplifier Design Challenges               | 138 |

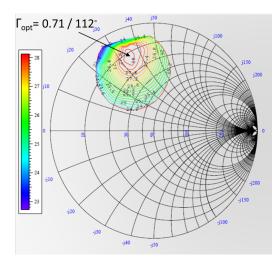

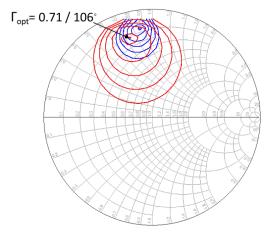

|              |       | 7.1.1   | Intrinsic Load-pull Target                            | 140 |

|              |       | 7.1.2   | Load-pull Target Scaling                              | 143 |

|              |       | 7.1.3   | Cripps Optimal Load line                              | 145 |

|              | 7.2   | Design  | 1                                                     | 146 |

|              |       | 7.2.1   | Transistor Unit Cell Optimisation                     | 148 |

|              |       | 7.2.2   | Broadband Impedance Transformer                       | 149 |

|              | 7.3   | Simula  | ations                                                | 156 |

|              | 7.4   | Summ    | ary                                                   | 159 |

| 8            | Con   | clusio  | n and Future Opportunities                            | 161 |

|              | 8.1   | Outco   | mes                                                   | 161 |

|              |       | 8.1.1   | Non-dispersive Scalable Small-signal Characterisation | 163 |

|              |       | 8.1.2   | Single-finger Thermal Characterisation                | 163 |

|              |       | 8.1.3   | Trap-state Extraction                                 | 164 |

|              | 8.2   | Broad   | er Adoption                                           | 164 |

|              | 8.3   | Future  | e Opportunities                                       | 165 |

|              |       | 8.3.1   | Further Model Improvement                             | 165 |

|              |       | 8.3.2   | Application Perspective                               | 166 |

| $\mathbf{A}$ | App   | oendix  | Α                                                     | 167 |

|              | A.1   | 2D FE   | EM SPICE CODE                                         | 167 |

| в            | App   | oendix  | В                                                     | 175 |

|              | B.1   | 3D FE   | EM SPICE CODE                                         | 175 |

| Li           | st of | Abbre   | eviations                                             | 181 |

| Re           | efere | nces    |                                                       | 183 |

## List of Figures

| 2.1 | A basic example of GaAs HEMT structure                                                   | 9  |

|-----|------------------------------------------------------------------------------------------|----|

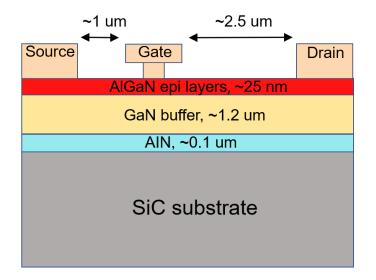

| 2.2 | A basic example of GaN HEMT structure                                                    | 10 |

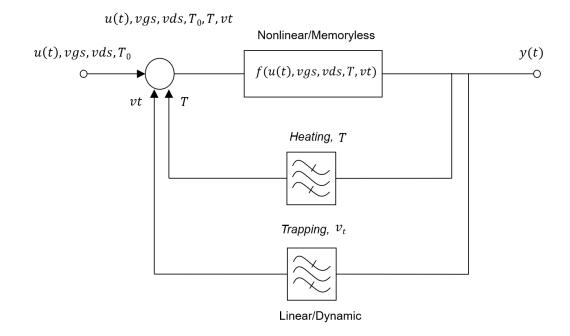

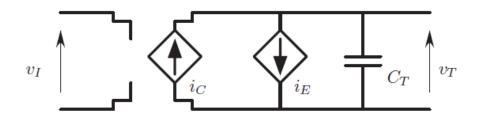

| 2.3 | A simple block diagram model of a nonlinear device illustrating how the                  |    |

|     | memory effects can be included                                                           | 11 |

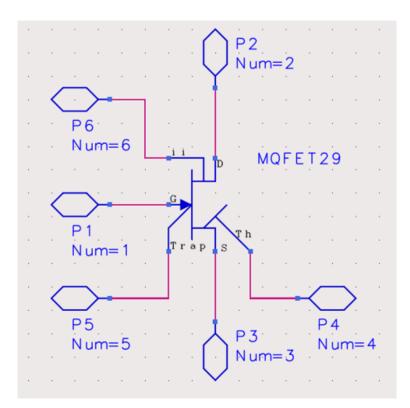

| 2.4 | MQFET model symbol showing the accessible nodes including the dy-                        |    |

|     | namic feedback nodes; thermal, trap and impact ionisation. The model                     |    |

|     | is used in Chapter 5 as part of a complete large-signal intrinsic model                  |    |

|     | with Chapters 3, 4 and 5 preparing for this integration                                  | 18 |

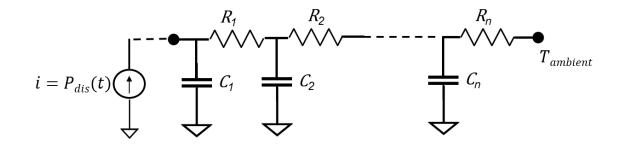

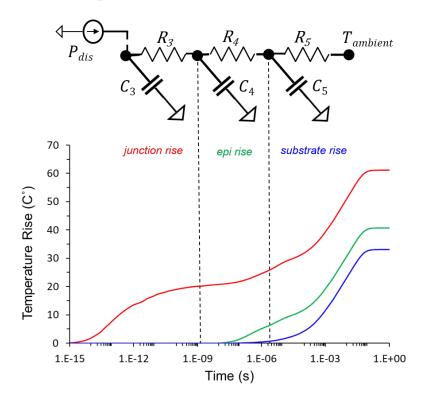

| 2.5 | RC ladder network used in dynamic electrothermal transistor models                       | 19 |

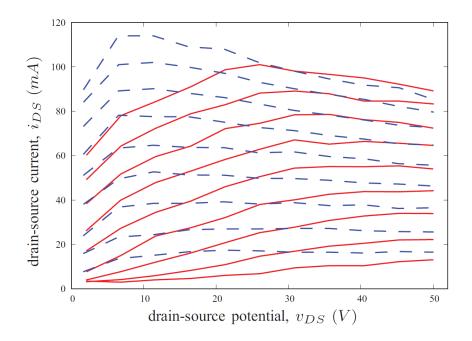

| 2.6 | Pulsed-I/V of a GaN device, measured at two different times. Duty                        |    |

|     | cycle 10%, pulse time: blue dash 50 $\mu$ s, red solid 1s                                | 23 |

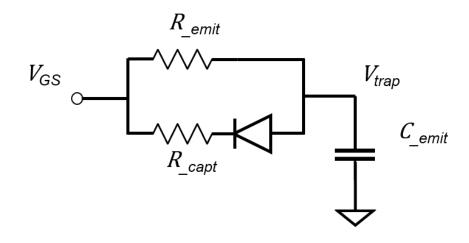

| 2.7 | Traditional circuit model of a trap centre with a single diode                           | 24 |

| 2.8 | Circuit model of a trap centre [1]                                                       | 24 |

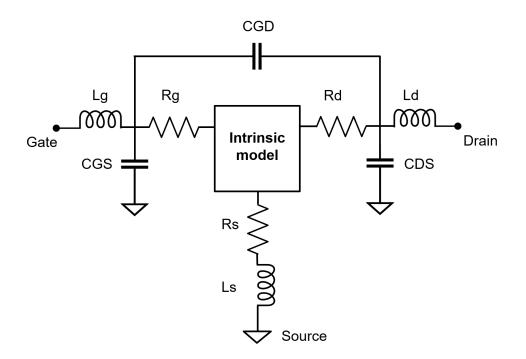

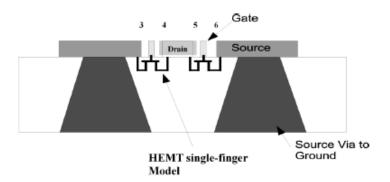

| 3.1 | HEMT device Model representation showing the extrinsic equivalent cir-                   |    |

|     | cuit                                                                                     | 29 |

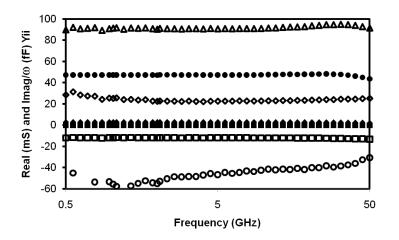

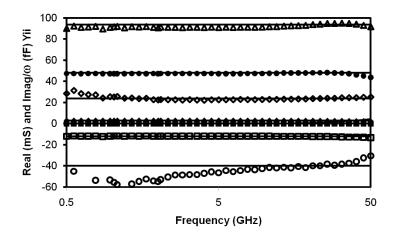

| 3.2 | Intrinsic Y-parameters of each finger of a 2×75 $\mu {\rm m}$ HEMT at 3.5 V              |    |

|     | and 100 mA/mm: $y_{11}$ (triangles), $y_{12}$ (squares), $y_{21}$ (circles) and $y_{22}$ |    |

|     | (diamonds). Real parts shown with filled shapes, imaginary hollow. $\ .$ .               | 31 |

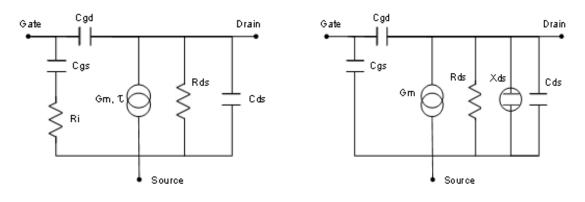

| 3.3 | Intrinsic FET equivalent circuit models.                                                 | 31 |

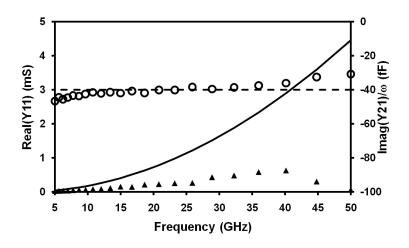

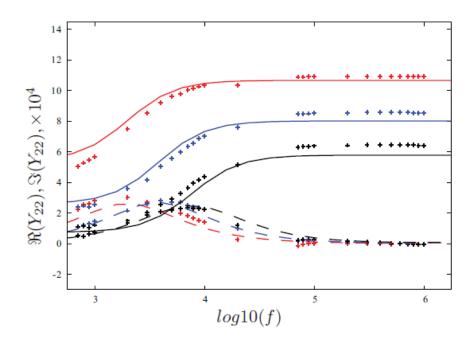

| 3.4  | Intrinsic Y-parameters vs model with $R_i = 7 \Omega$ : Real part of $y_{11}$ (data            |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | shown as triangles, model as solid line), Imaginary part of $y_{12}$ (data                     |    |

|      | shown as hollow circles, model as dashed line)                                                 | 32 |

| 3.5  | Fit to intrinsic data with the non-dispersive model $y_{11}$ (triangles), $y_{12}$             |    |

|      | (squares), $y_{21}$ (circles) and $y_{22}$ (diamonds). Real parts shown with filled            |    |

|      | shapes, imaginary hollow.                                                                      | 33 |

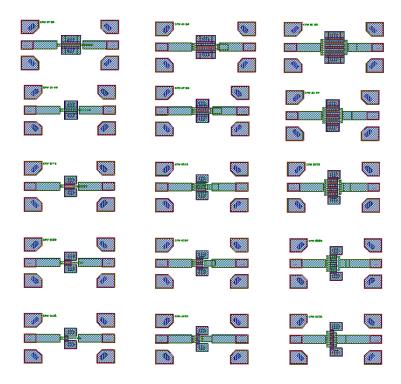

| 3.6  | Test structures of various HEMT devices used for single-finger model                           |    |

|      | extraction and verification.                                                                   | 34 |

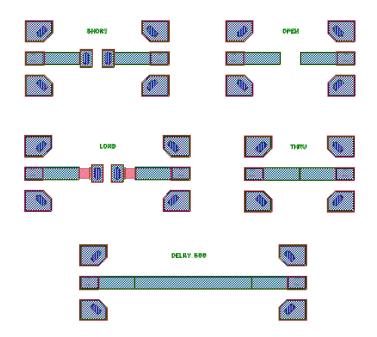

| 3.7  | SOLT calibration structures used with the Vector Network Analyser to                           |    |

|      | deembedd the small-signal measurements to the DUT                                              | 35 |

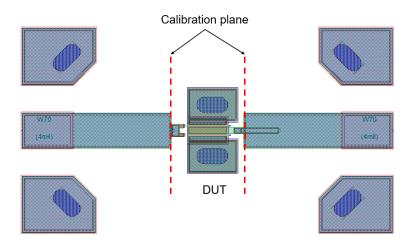

| 3.8  | A 2 $\times 75~\mu{\rm m}$ microstrip HEMT device layout showing the SOLT cali-                |    |

|      | bration reference planes.                                                                      | 37 |

| 3.9  | Connecting the intrinsic single-finger model to an EM-analysed access                          |    |

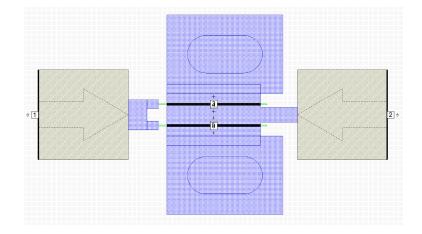

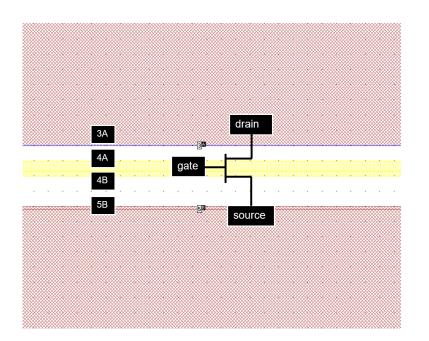

|      | network structure that uses internal ports                                                     | 38 |

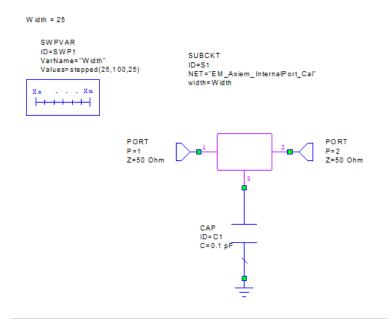

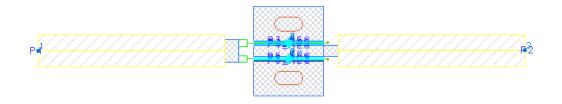

| 3.10 | AXIEM EM structure setup for $2 \times 75 \ \mu m$ microstrip device                           | 39 |

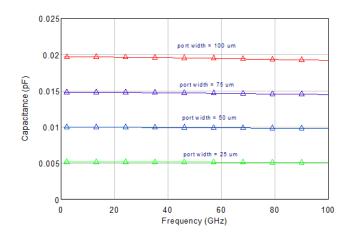

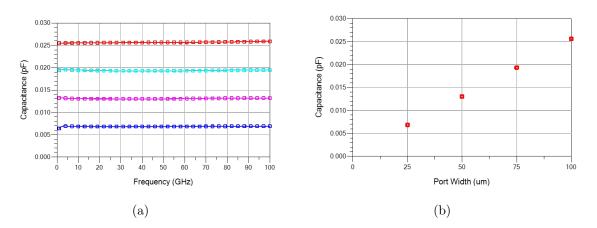

| 3.11 | AXIEM's internal port capacitance versus frequency with port width                             |    |

|      | swept from 25 $\mu$ m to 100 $\mu$ m                                                           | 40 |

| 3.12 | AXIEM EM structure used to calculate the capacitance associated with                           |    |

|      | its internal port                                                                              | 40 |

| 3.13 | AXIEM internal port connected in a schematic.                                                  | 41 |

| 3.14 | Momentum layout setup for a 2 ×75 $\mu$ m                                                      | 42 |

| 3.15 | Momentum's internal port capacitance with differential gap-port width                          |    |

|      | swept from 25 $\mu \mathrm{m}$ to 100 $\mu \mathrm{m}$ versus (a) frequency and (b) port width |    |

|      | at 10 GHz                                                                                      | 42 |

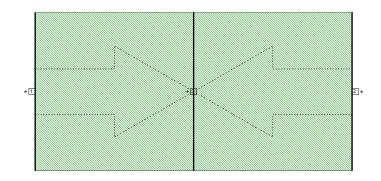

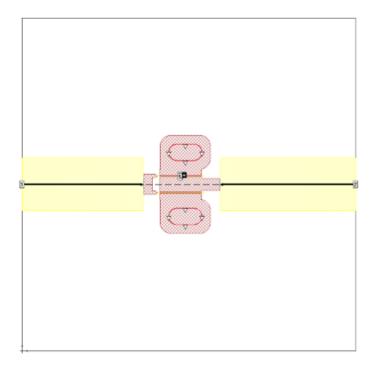

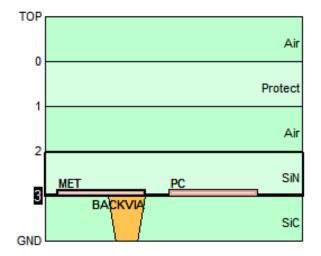

| 3.16 | Sonnet layout setup for a $2 \times 75 \ \mu m$ microstrip device                              | 44 |

| 3.17 | Sonnet co-calibrated ports setup, illustrating how the intrinsic model is                      |    |

|      | connected to the EM in the schematic.                                                          | 44 |

| 3.18 | Sonnet stack-up example.                                                                       | 45 |

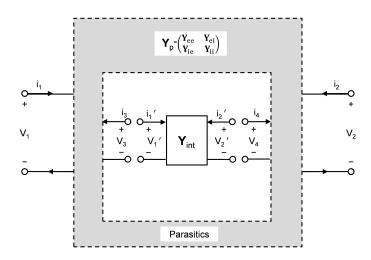

| 3.19 | Extrinsic one-finger HEMT in admittance form with gate, drain and                              |    |

|      | source metal, $Y_p$ segregated from the intrinsic device $Y_{int}$                             | 46 |

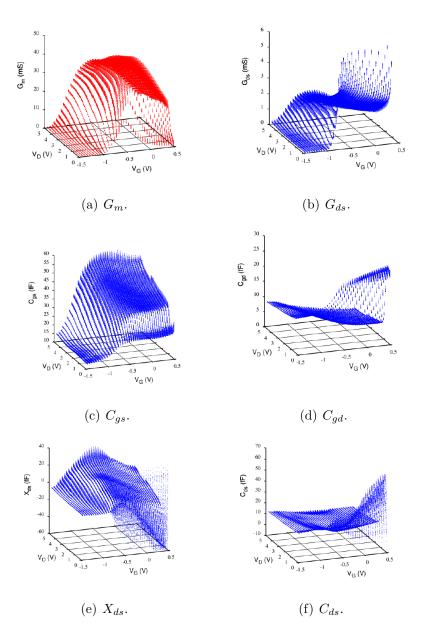

| 3.20 | Intrinsic model parameters extracted for a wide range of gate and drain                  |    |

|------|------------------------------------------------------------------------------------------|----|

|      | biases. Measurements taken from 50 MHz to 50 GHz with 64 points                          |    |

|      | covering the frequency range in logarithmic steps.                                       | 53 |

| 3.21 | Extracted transconductance, $g_m$ , (circles) and output conductance, $10 \times G_d$    | s, |

|      | (squares) per finger for four HEMT widths. Solid lines show scaling fit.                 | 54 |

| 3.22 | Extracted gate-source capacitance, $C_{gs}$ , (circles, left axis), gate-drain           |    |

|      | capacitance, $C_{gd}$ , (triangles, right), drain-source capacitance, $C_{ds}$ , (dia-   |    |

|      | monds, right), drain-source transcapacitance, $X_{ds}$ , (squares, right) per            |    |

|      | finger for four HEMT widths. Lines show scaling.                                         | 55 |

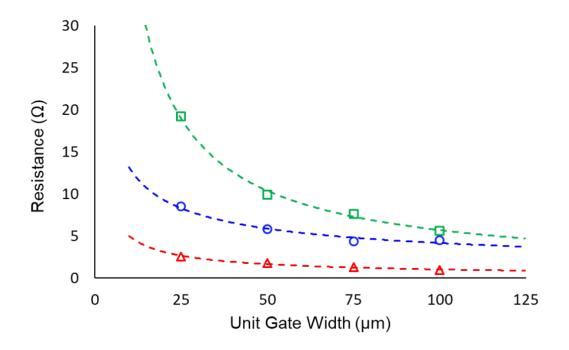

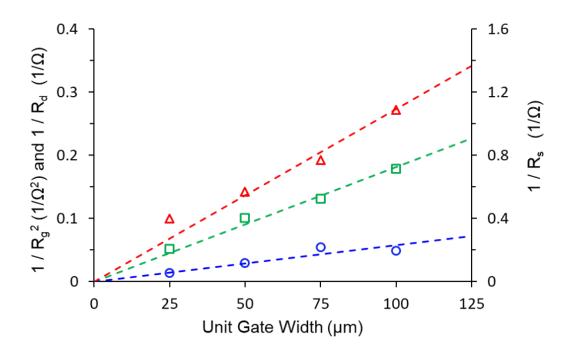

| 3.23 | Access resistances, $R_g$ (blue circles), $R_s$ (red triangles) and $R_d$ (green         |    |

|      | squares). Dashed lines are plotted as a guide.                                           | 57 |

| 3.24 | Access conductances, $1/R_g^2$ (blue circles), $1/R_s$ (red triangles) and $1/R_d$       |    |

|      | (green squares). Dashed lines represent a linear fit to the data with zero               |    |

|      | offset.                                                                                  | 57 |

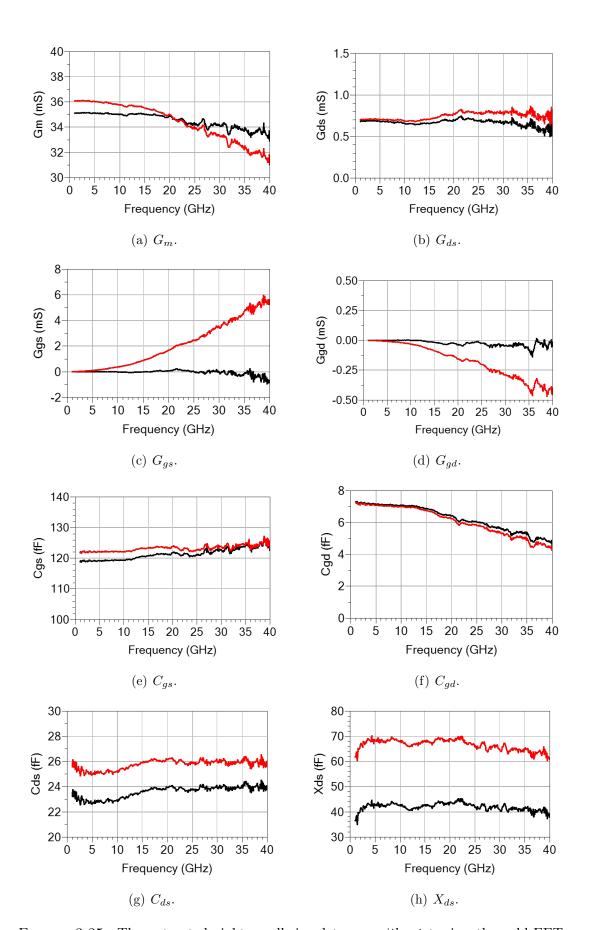

| 3.25 | The extracted eight small-signal terms $without$ tuning the cold-FET ex-                 |    |

|      | tracted access resistances (red) and with tuning the cold-FET extracted                  |    |

|      | access resistances (black). The data shown is for 75 $\mu \mathrm{m}$ single-finger at   |    |

|      | $V_{DS} = 20$ V and $V_{GS} = -1.5$ V over frequencies from 1-40 GHz in 0.1              |    |

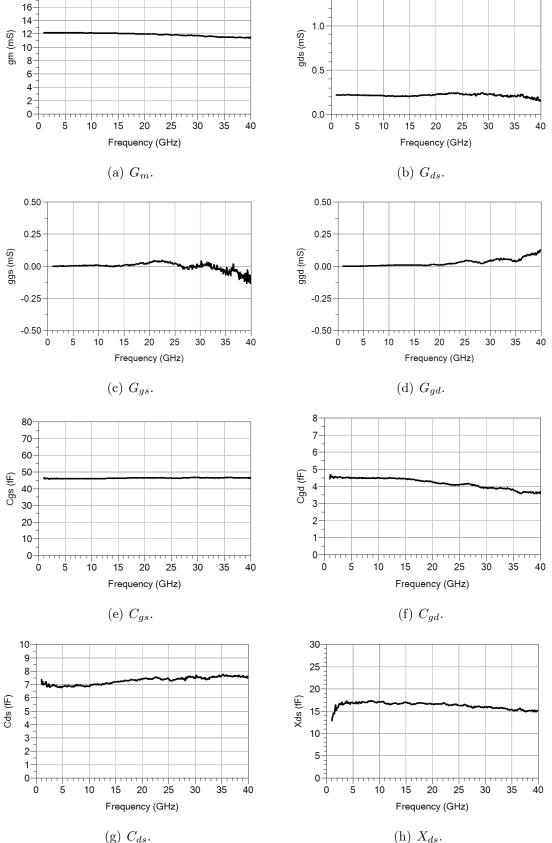

|      | GHz steps.                                                                               | 58 |

| 3.26 | The extracted eight small-signal terms for the 25 $\mu {\rm m}$ single-finger linear     |    |

|      | model at $V_{DS} = 20$ V and $V_{GS} = -1.5$ V over frequencies from 1-40 GHz            |    |

|      | in 0.1 GHz steps.                                                                        | 60 |

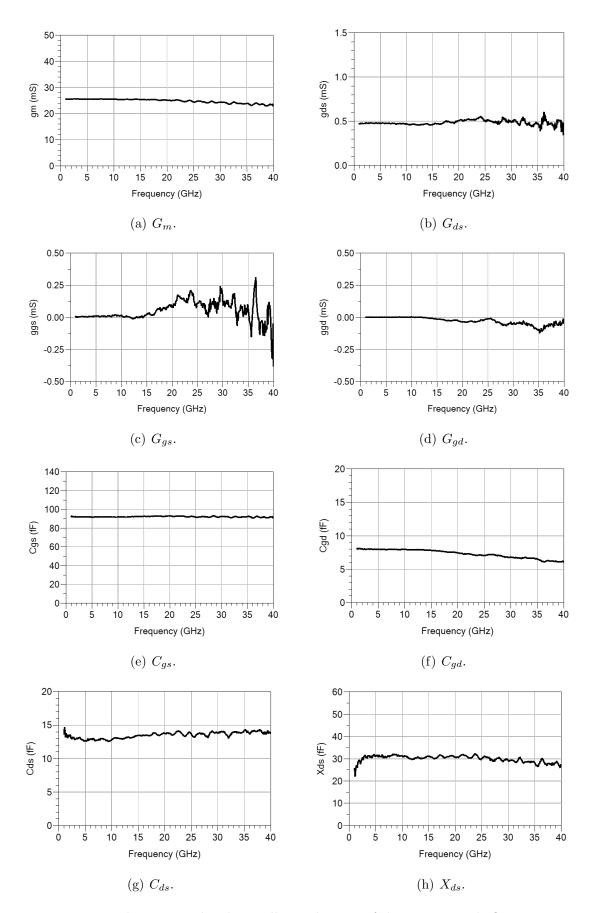

| 3.27 | The extracted eight small-signal terms of the 50 $\mu {\rm m}$ single-finger at $V_{DS}$ |    |

|      | = 20 V and $V_{GS}$ = -1.5 V over frequencies from 1-40 GHz in 0.1 GHz                   |    |

|      | steps.                                                                                   | 61 |

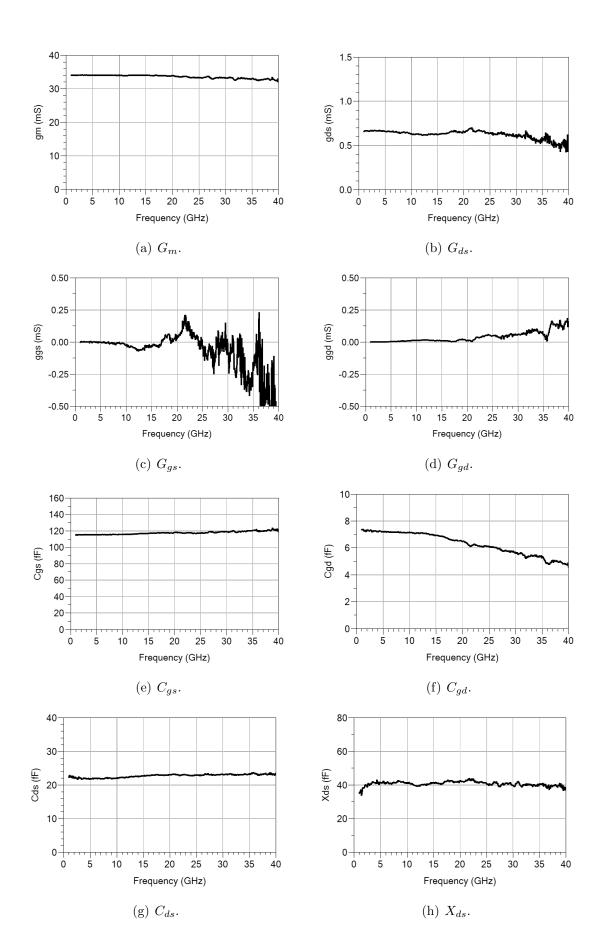

| 3.28 | The extracted eight small-signal terms of the 75 $\mu {\rm m}$ single-finger at $V_{DS}$ |    |

|      | = 20 V and $V_{GS}$ = -1.5 V over frequencies from 1-40 GHz in 0.1 GHz                   |    |

|      | steps.                                                                                   | 62 |

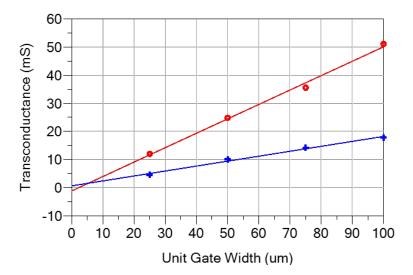

| 3.29 | Extracted transconductance $g_m$ (red) and output conductance $g_{ds}$ (blue)            |    |

|      | per finger for four GaN HEMT widths. Solid lines show scaling fit                        | 63 |

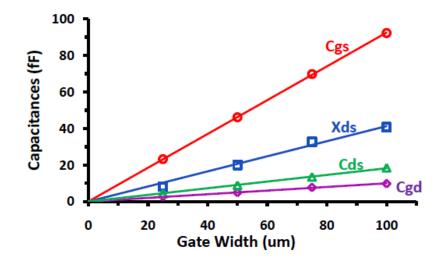

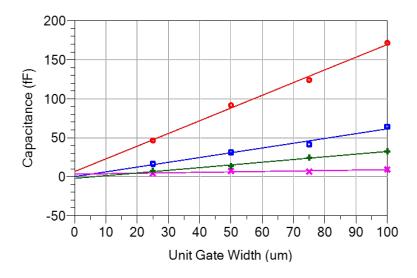

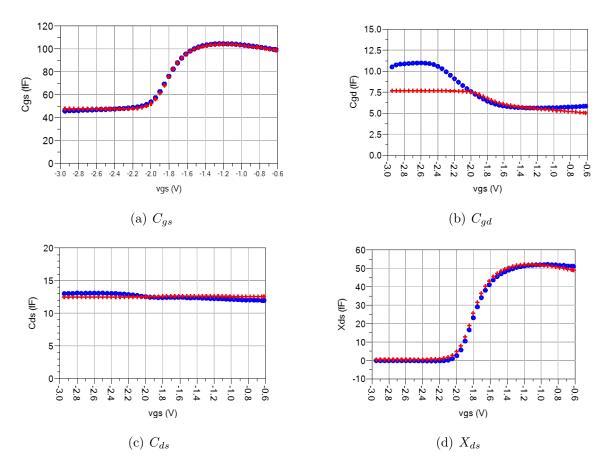

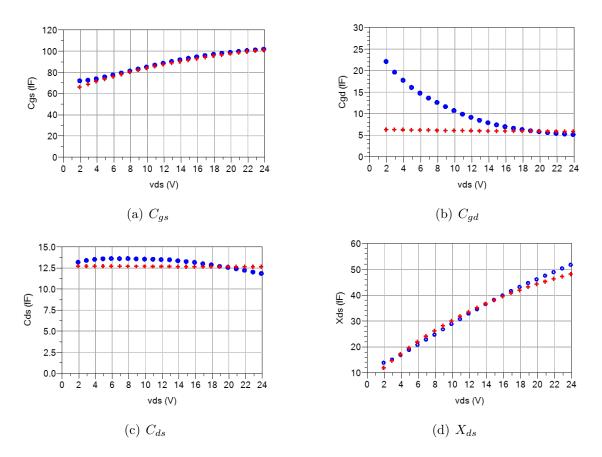

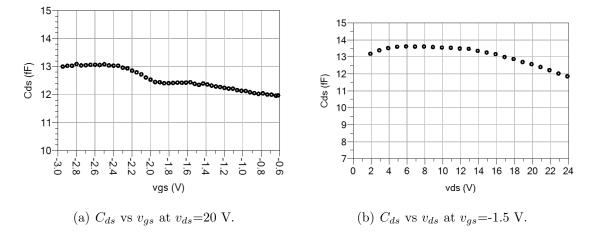

| 3.30 | Extracted gate-source capacitance $C_{gs}$ (red), gate-drain capacitance $C_{gd}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (magenta), drain-source capacitance $C_{ds}$ (green) and drain-source tran-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | scapacitance $X_{ds}$ (blue) per finger for four GaN HEMT widths. Solid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | lines show scaling fit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63 |

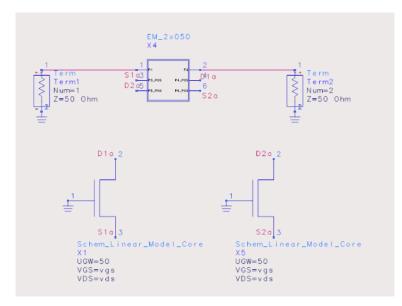

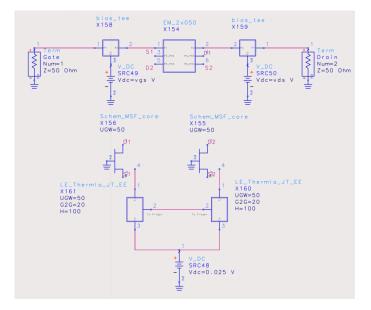

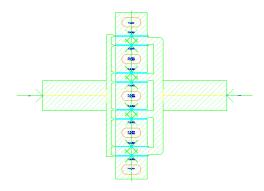

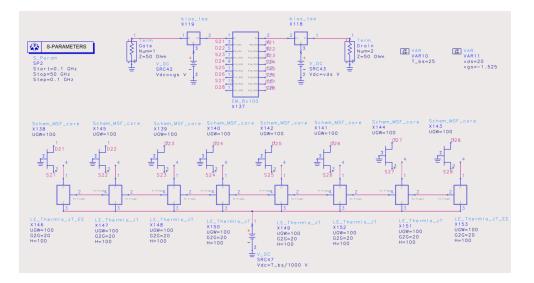

| 3.31 | A schematic of a complete $2\times 50~\mu{\rm m}$ showing the lumped-element the<br>r-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | mal model connection to the thermal node of the model. $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

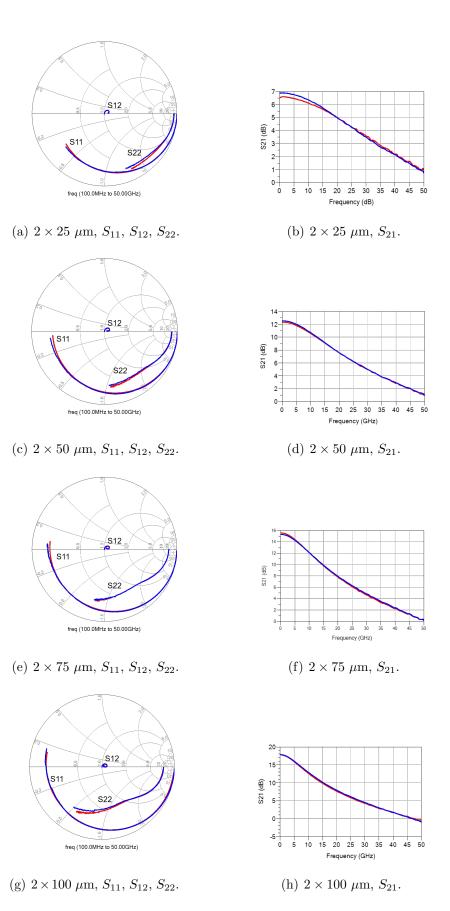

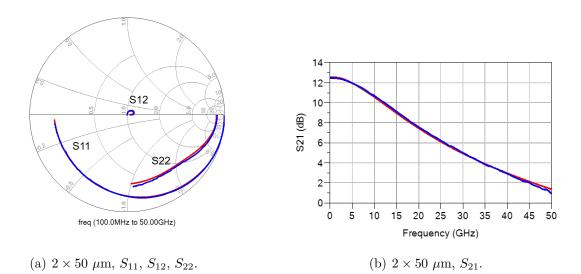

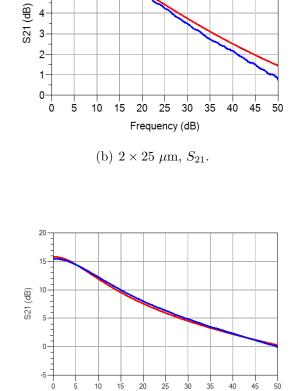

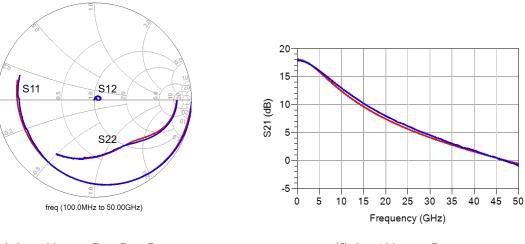

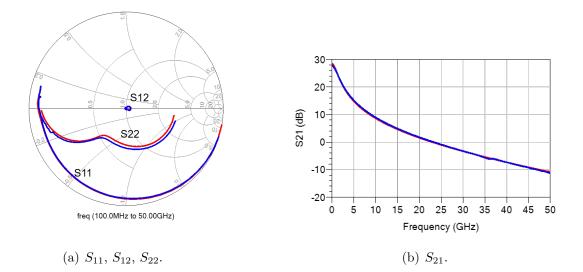

| 3.32 | Modelled (blue) and measured (red) $S$ -parameters performance from top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | to bottom for 2 $\times$ 25, 2 $\times$ 50 , 2 $\times$ 75 and 2 $\times$ 100 $\mu {\rm m}$ devices at $V_{DS}=$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | 20 V and $V_{GS} = -1.5$ V over frequencies from 1-50 GHz in 0.1 GHz steps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65 |

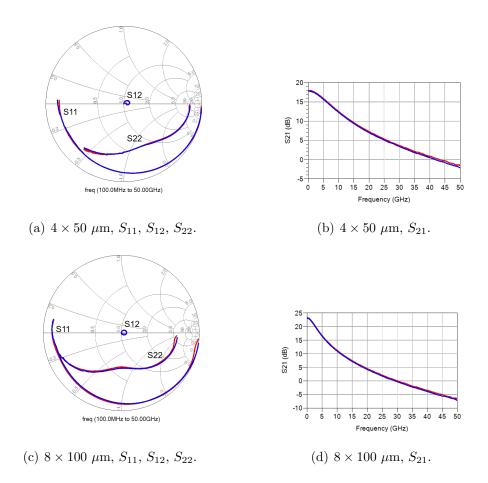

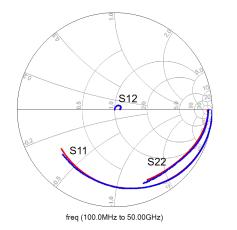

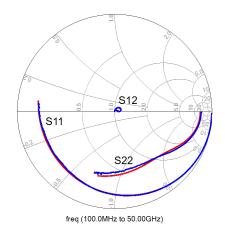

| 3.33 | Modelled (blue) and measured (red) $S$ -parameters performance from top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | to bottom for $4 \times 50 \ \mu \text{m}$ and $8 \times 50 \ \mu \text{m}$ devices at $V_{DS} = 20 \text{ V}$ and $V_{GS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | = -1.5 V over frequencies from 1-50 GHz in 0.1 GHz steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66 |

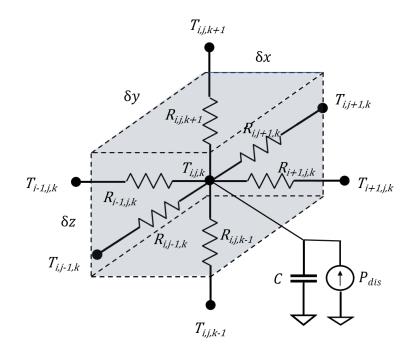

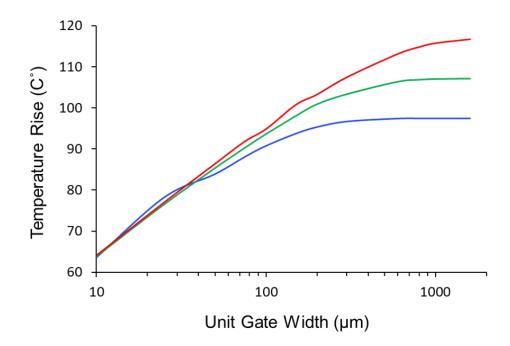

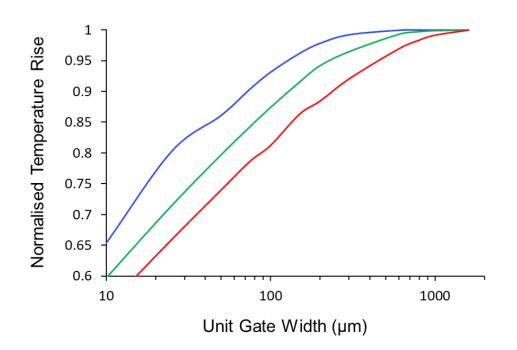

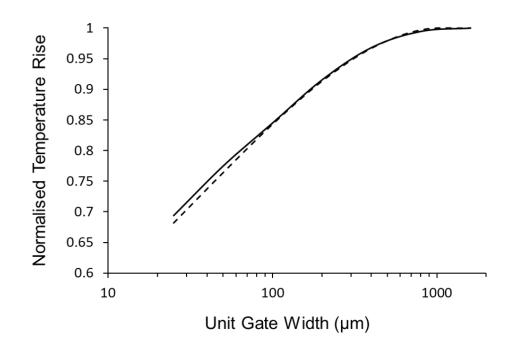

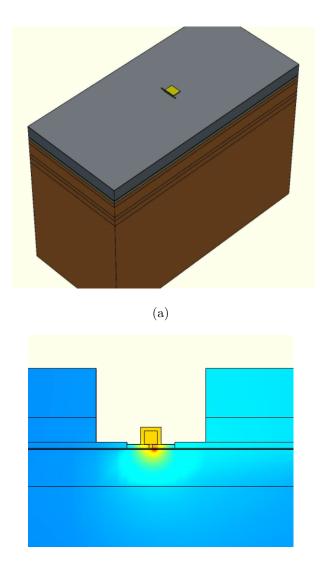

| 4.1  | 3D representation of the SPICE finite-element thermal model. ${\cal C}$ repre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | sents the heat capacity of the volume highlighted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73 |

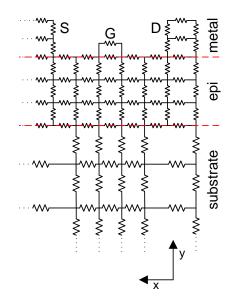

| 4.2  | A simplified representation of the SPICE finite-element thermal model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | Capacitors not shown here for simplicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74 |

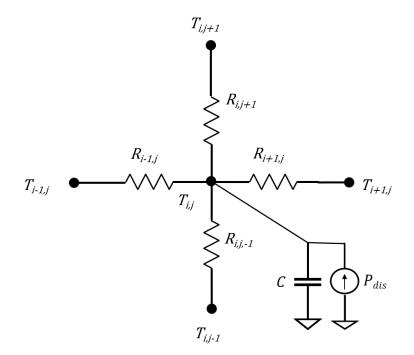

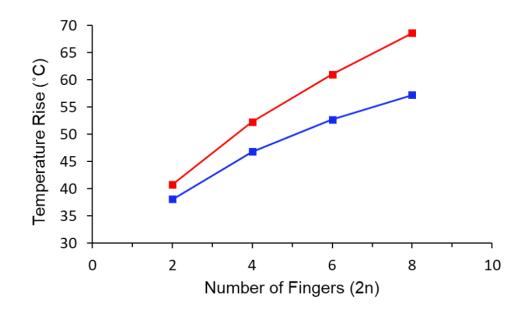

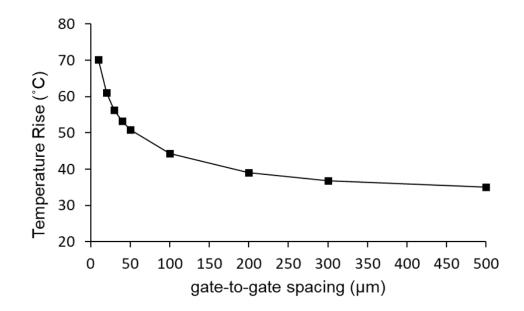

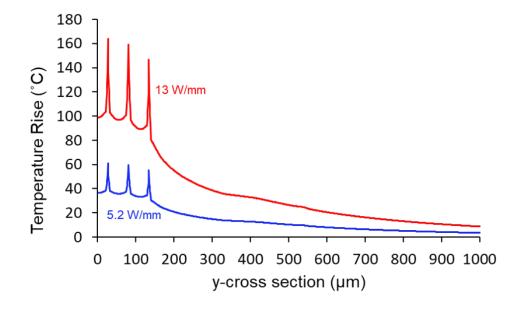

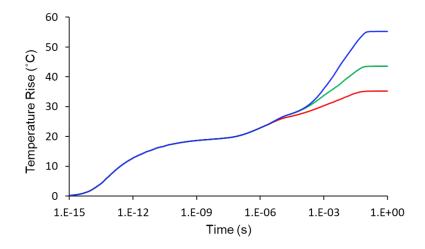

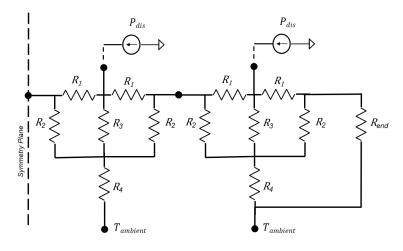

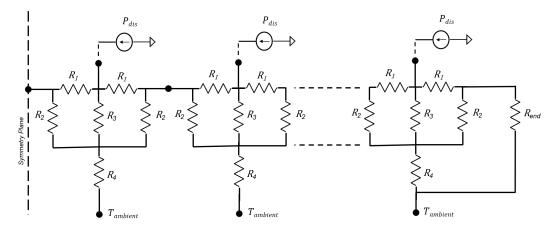

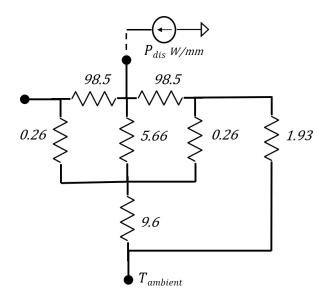

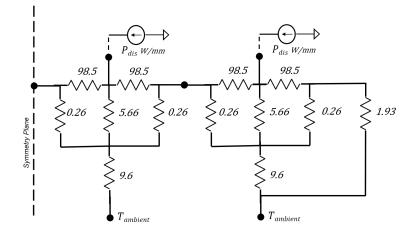

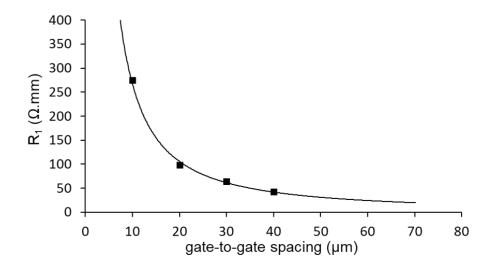

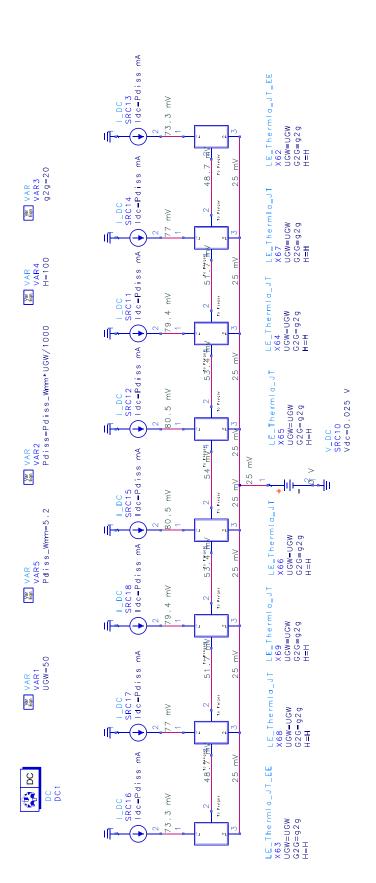

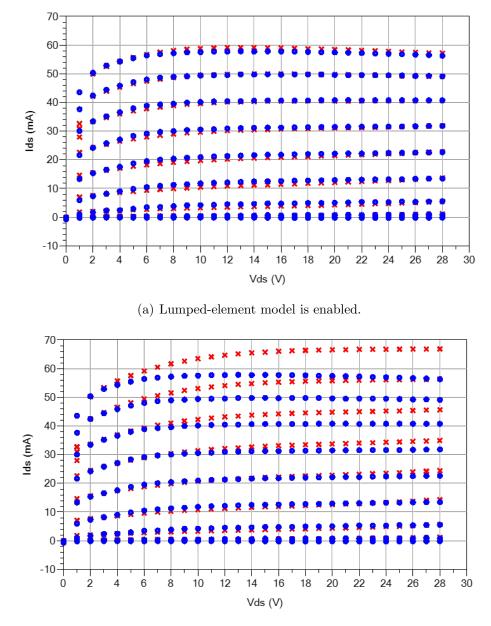

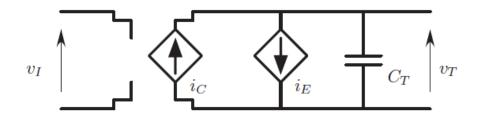

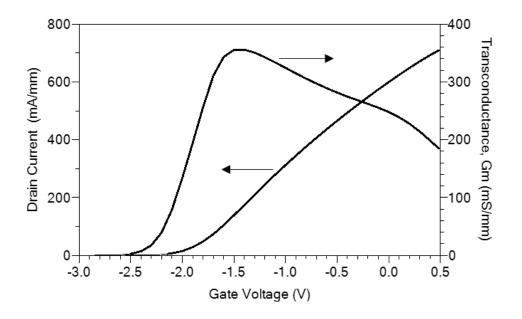

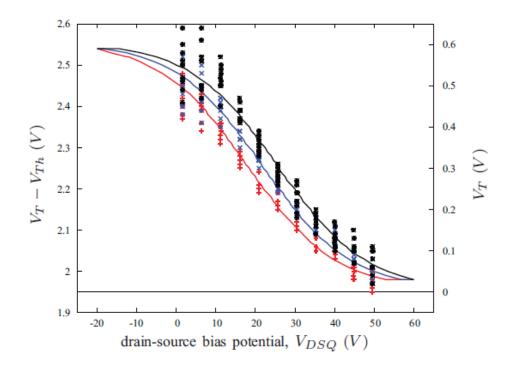

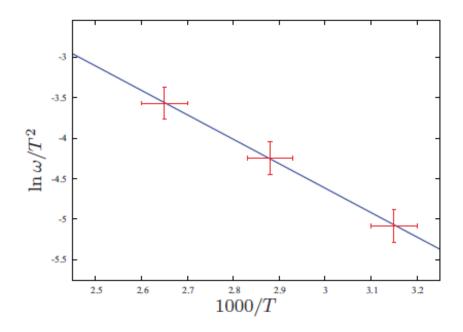

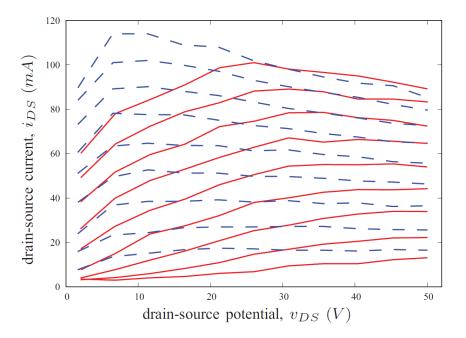

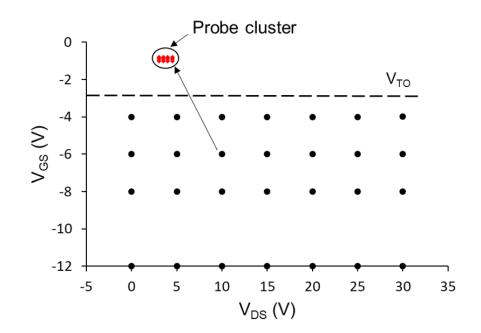

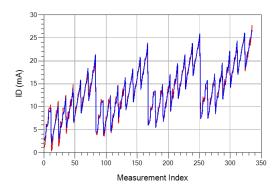

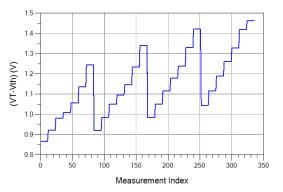

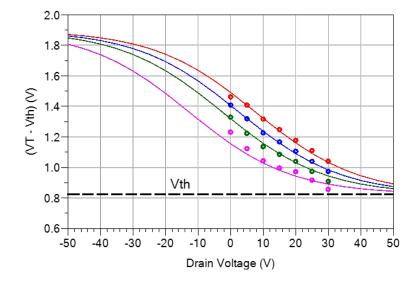

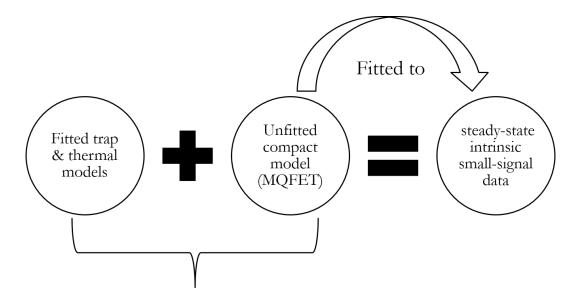

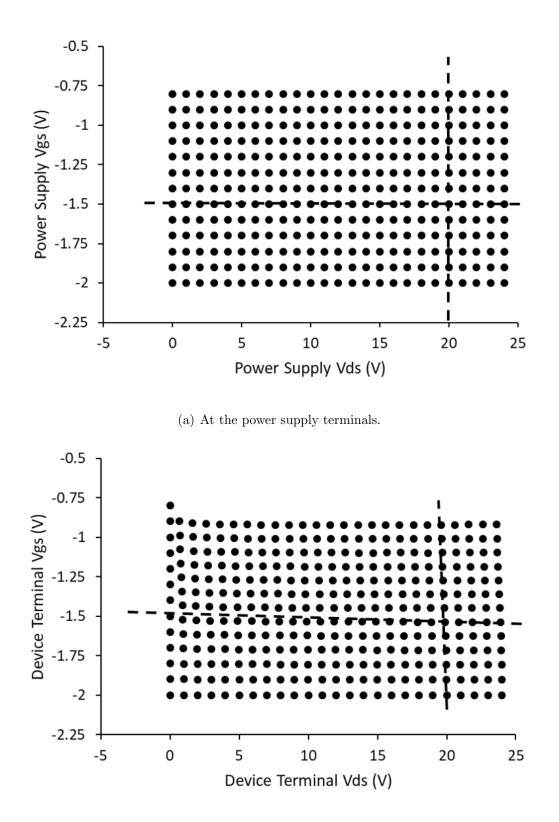

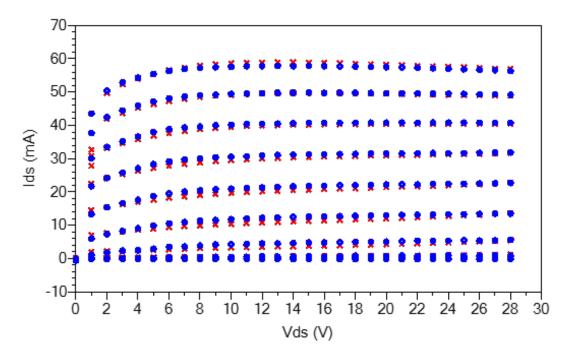

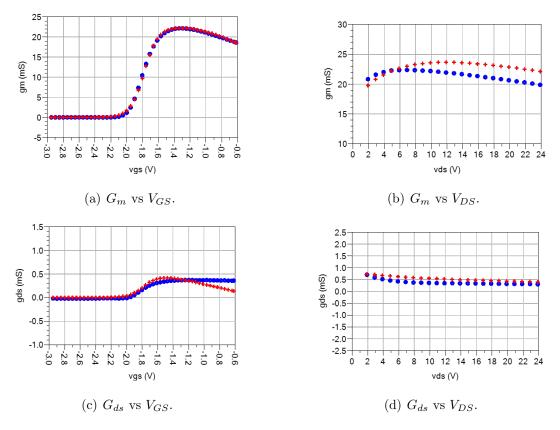

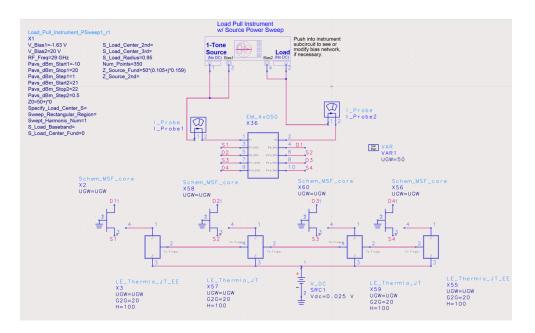

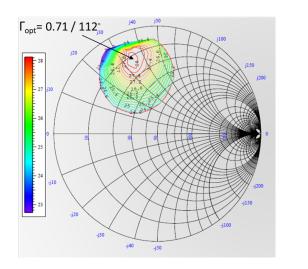

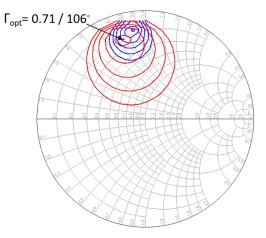

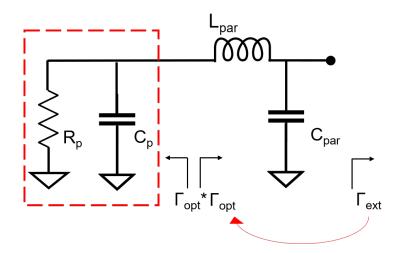

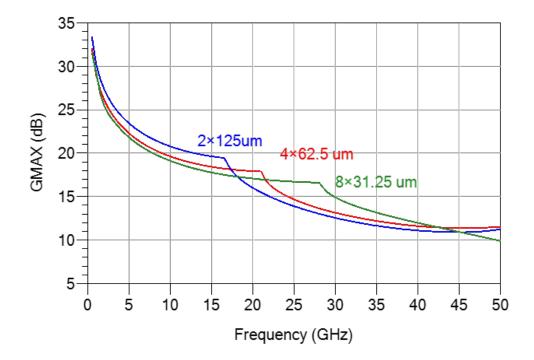

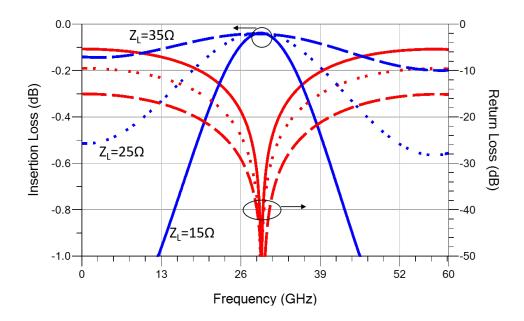

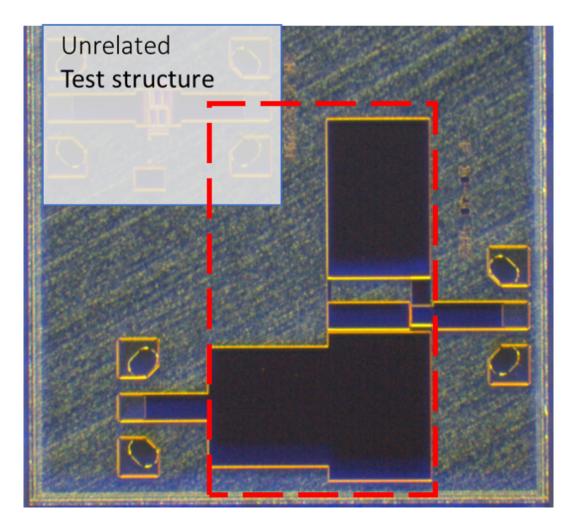

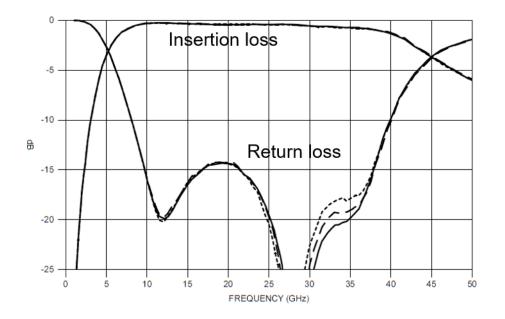

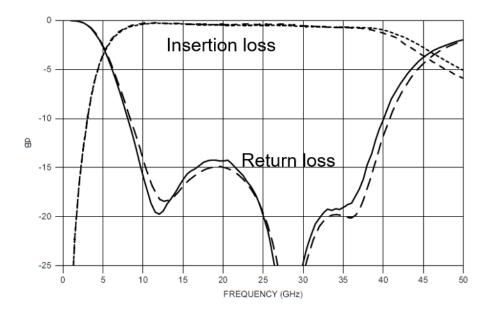

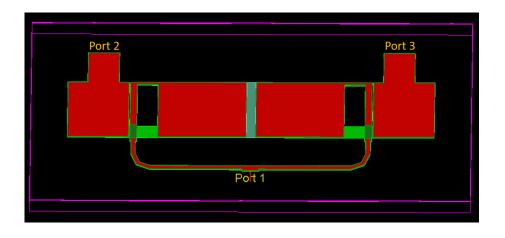

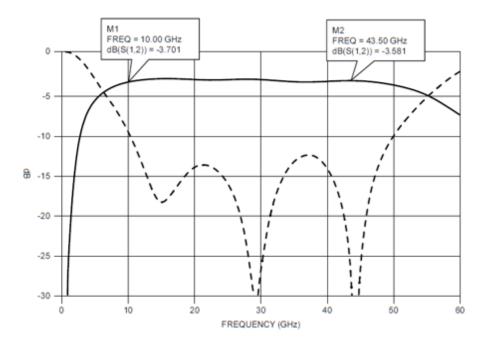

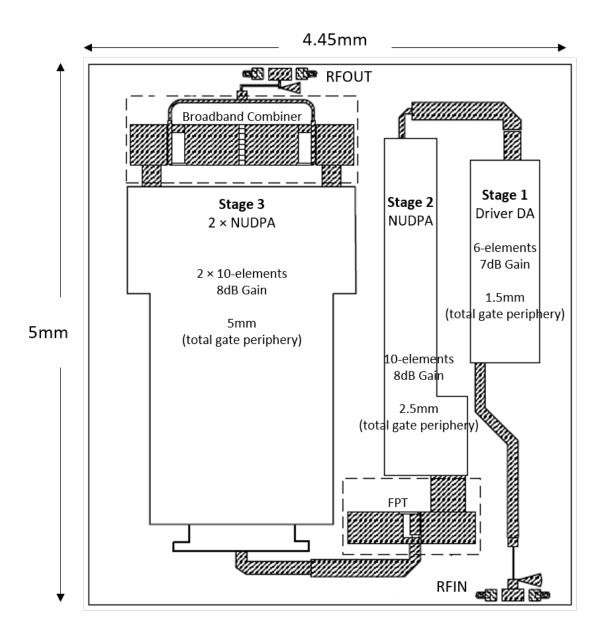

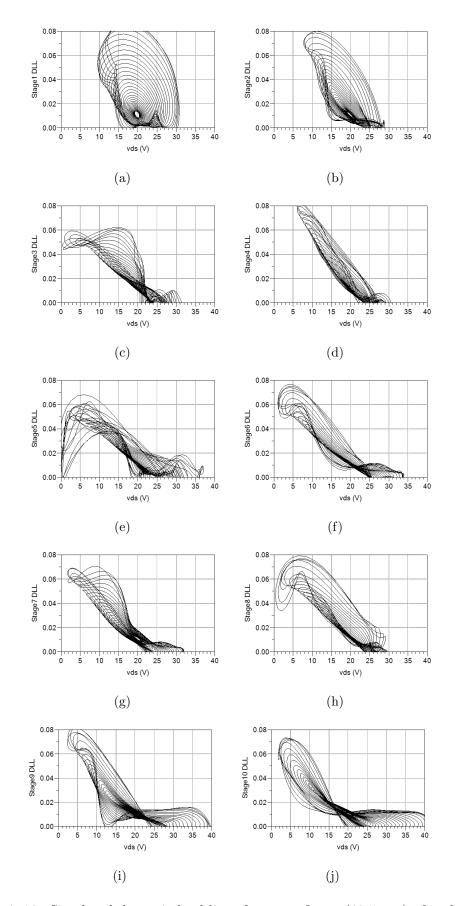

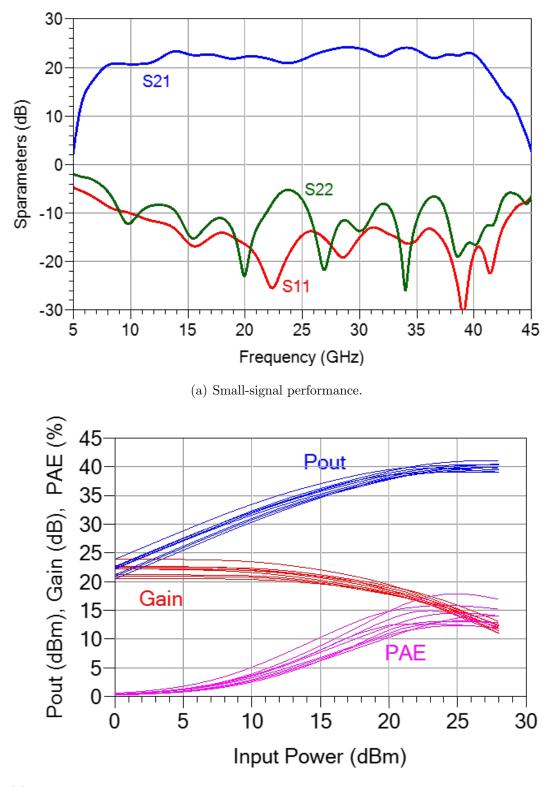

| 4.3  | Simplified 2D representation of the SPICE finite-element thermal model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |